没有合适的资源?快使用搜索试试~ 我知道了~

首页RISCV指令集原版-卷2-特权指令集v1.12

RISCV指令集原版-卷2-特权指令集v1.12

需积分: 43 17 下载量 11 浏览量

更新于2023-03-03

评论

收藏 656KB PDF 举报

RISCV指令集原版-卷2-特权指令集v1.12 英文原版 The RISC-V Instruction Set Manual Volume II: Privileged Architecture Document Version 1.12-draft

资源详情

资源评论

资源推荐

The RISC-V Instruction Set Manual

Volume II: Privileged Architecture

Document Version 1.12-draft

Editors: Andrew Waterman

1

, Krste Asanovi´c

1,2

1

SiFive Inc.,

2

CS Division, EECS Department, University of California, Berkeley

andrew@sifive.com, krste@berkeley.edu

February 29, 2020

Contributors to all versions of the spec in alphabetical order (please contact editors to suggest

corrections): Krste Asanovi´c, Peter Ashenden, Rimas Aviˇzienis, Jacob Bachmeyer, Allen J. Baum,

Jonathan Behrens, Paolo Bonzini, Ruslan Bukin, Christopher Celio, Chuanhua Chang, David Chis-

nall, Anthony Coulter, Palmer Dabbelt, Monte Dalrymple, Dennis Ferguson, Marc Gauthier, Andy

Glew, Gary Guo, Mike Frysinger, John Hauser, David Horner, Olof Johansson, David Kruckemyer,

Yunsup Lee, Andrew Lutomirski, Prashanth Mundkur, Jonathan Neusch¨afer, Rishiyur Nikhil, Ste-

fan O’Rear, Albert Ou, John Ousterhout, David Patterson, Dmitri Pavlov, Kade Phillips, Josh

Scheid, Colin Schmidt, Michael Taylor, Wesley Terpstra, Matt Thomas, Tommy Thorn, Ray Van-

DeWalker, Megan Wachs, Steve Wallach, Andrew Waterman, Clifford Wolf, and Reinoud Zandijk.

This document is released under a Creative Commons Attribution 4.0 International License.

This document is a derivative of the RISC-V privileged specification version 1.9.1 released under

following license:

c

2010–2017 Andrew Waterman, Yunsup Lee, Rimas Aviˇzienis, David Patterson,

Krste Asanovi´c. Creative Commons Attribution 4.0 International License.

Please cite as: “The RISC-V Instruction Set Manual, Volume II: Privileged Architecture, Document

Version 1.12-draft”, Editors Andrew Waterman and Krste Asanovi´c, RISC-V Foundation, June

2019.

Preface

This is a draft of version 1.12 of the RISC-V privileged architecture proposal. The document

contains the following versions of the RISC-V ISA modules:

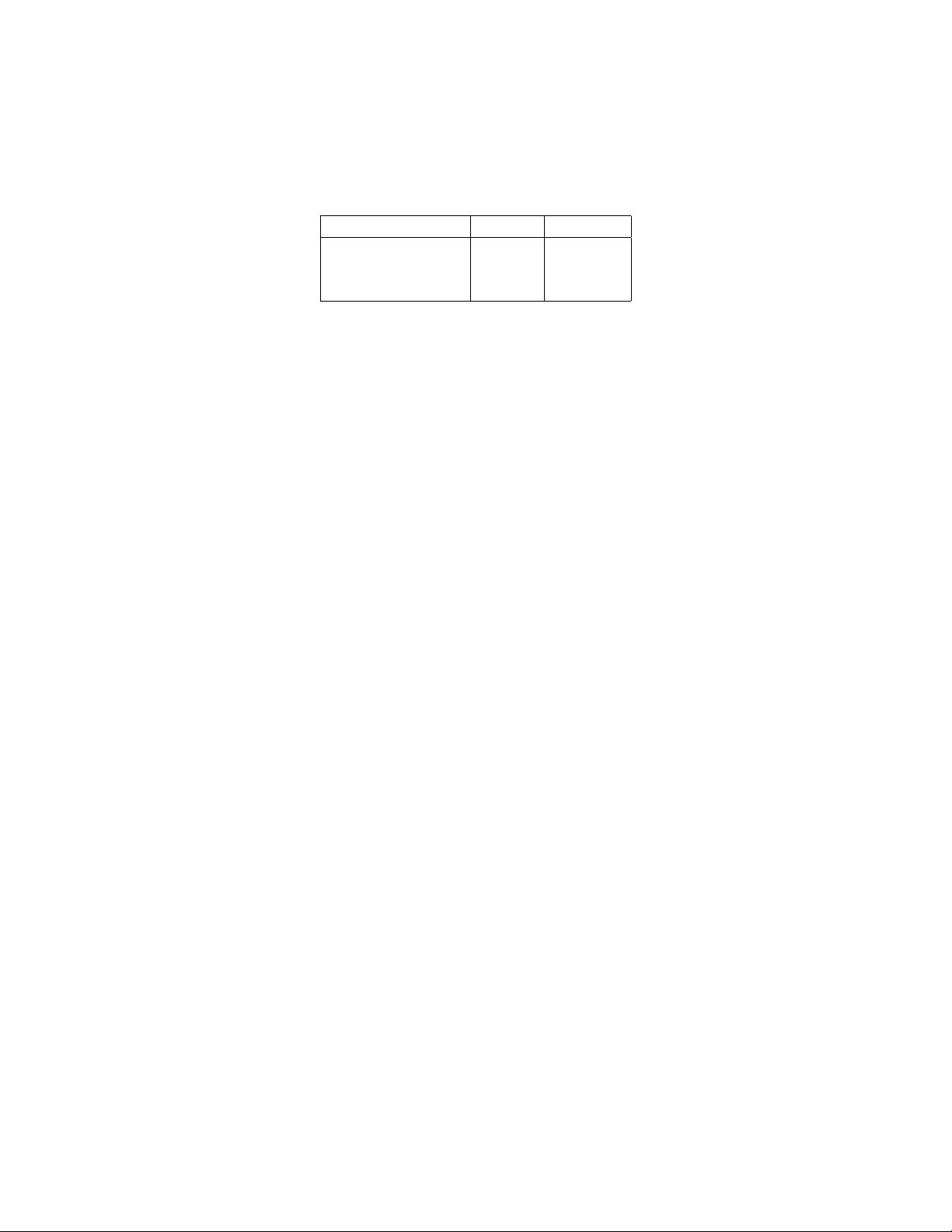

Module Version Status

Machine ISA 1.12 Draft

Supervisor ISA 1.12 Draft

Hypervisor ISA 0.6 Draft

N Extension 1.1 Draft

The Machine and Supervisor ISAs, version 1.11, have been ratified by the RISC-V Foundation.

Version 1.12 of these modules, described in this document, is a minor revision to version 1.11.

The following changes have been made since version 1.11, which, while not strictly backwards

compatible, are not anticipated to cause software portability problems in practice:

• Changed MRET and SRET to clear mstatus.MPRV when leaving M-mode.

• Reserved additional satp patterns for future use.

• Stated that the scause Exception Code field must implement bits 4–0 at minimum.

• Relaxed I/O regions have been specified to follow RVWMO. The previous specification implied

that PPO rules other than fences and acquire/release annotations did not apply.

• Constrained the LR/SC reservation set size and shape when using page-based virtual memory.

Additionally, the following compatible changes have been made since version 1.11:

• Defined the RV32-only CSR mstatush, which contains most of the same fields as the upper

32 bits of RV64’s mstatus.

• Permitted the unconditional delegation of less-privileged interrupts.

• Added optional big-endian and bi-endian support.

Finally, the hypervisor architecture proposal has been extensively revised.

i

ii Volume II: RISC-V Privileged Architectures V1.12-draft

Preface to Version 1.11

This is version 1.11 of the RISC-V privileged architecture. The document contains the following

versions of the RISC-V ISA modules:

Module Version Status

Machine ISA 1.11 Ratified

Supervisor ISA 1.11 Ratified

Hypervisor ISA 0.3 Draft

Changes from version 1.10 include:

• Moved Machine and Supervisor spec to Ratified status.

• Improvements to the description and commentary.

• Added a draft proposal for a hypervisor extension.

• Specified which interrupt sources are reserved for standard use.

• Allocated some synchronous exception causes for custom use.

• Specified the priority ordering of synchronous exceptions.

• Added specification that xRET instructions may, but are not required to, clear LR reserva-

tions if A extension present.

• The virtual-memory system no longer permits supervisor mode to execute instructions from

user pages, regardless of the SUM setting.

• Software is strongly recommended to allocate ASIDs globally, so that a future extension can

globalize ASIDs for improved performance and hardware flexibility.

• SFENCE.VMA semantics have been clarified.

• Made the mstatus.MPP field WARL, rather than WLRL.

• Made the unused xip fields WPRI, rather than WIRI.

• Made the unused misa fields WLRL, rather than WIRI.

• Made the unused pmpaddr and pmpcfg fields WARL, rather than WIRI.

• Required all harts in a system to employ the same PTE-update scheme as each other.

• Rectified an editing error that misdescribed the mechanism by which mstatus.xIE is written

upon an exception.

• Described scheme for emulating misaligned AMOs.

• Specified the behavior of the misa and xepc registers in systems with variable IALIGN.

• Specified the behavior of writing self-contradictory values to the misa register.

• Defined the mcountinhibit CSR, which stops performance counters from incrementing to

reduce energy consumption.

• Specified semantics for PMP regions coarser than four bytes.

• Specified contents of CSRs across XLEN modification.

• Moved PLIC chapter into its own document.

Volume II: RISC-V Privileged Architectures V1.12-draft iii

Preface to Version 1.10

This is version 1.10 of the RISC-V privileged architecture proposal. Changes from version 1.9.1

include:

• The previous version of this document was released under a Creative Commons Attribution

4.0 International License by the original authors, and this and future versions of this document

will be released under the same license.

• The explicit convention on shadow CSR addresses has been removed to reclaim CSR space.

Shadow CSRs can still be added as needed.

• The mvendorid register now contains the JEDEC code of the core provider as opposed to

a code supplied by the Foundation. This avoids redundancy and offloads work from the

Foundation.

• The interrupt-enable stack discipline has been simplified.

• An optional mechanism to change the base ISA used by supervisor and user modes has been

added to the mstatus CSR, and the field previously called Base in misa has been renamed

to MXL for consistency.

• Clarified expected use of XS to summarize additional extension state status fields in mstatus.

• Optional vectored interrupt support has been added to the mtvec and stvec CSRs.

• The SEIP and UEIP bits in the mip CSR have been redefined to support software injection

of external interrupts.

• The mbadaddr register has been subsumed by a more general mtval register that can now

capture bad instruction bits on an illegal instruction fault to speed instruction emulation.

• The machine-mode base-and-bounds translation and protection schemes have been removed

from the specification as part of moving the virtual memory configuration to sptbr (now

satp). Some of the motivation for the base and bound schemes are now covered by the PMP

registers, but space remains available in mstatus to add these back at a later date if deemed

useful.

• In systems with only M-mode, or with both M-mode and U-mode but without U-mode

trap support, the medeleg and mideleg registers now do not exist, whereas previously they

returned zero.

• Virtual-memory page faults now have mcause values distinct from physical-memory access

exceptions. Page-fault exceptions can now be delegated to S-mode without delegating excep-

tions generated by PMA and PMP checks.

• An optional physical-memory protection (PMP) scheme has been proposed.

• The supervisor virtual memory configuration has been moved from the mstatus register to

the sptbr register. Accordingly, the sptbr register has been renamed to satp (Supervisor

Address Translation and Protection) to reflect its broadened role.

• The SFENCE.VM instruction has been removed in favor of the improved SFENCE.VMA

instruction.

• The mstatus bit MXR has been exposed to S-mode via sstatus.

• The polarity of the PUM bit in sstatus has been inverted to shorten code sequences involving

MXR. The bit has been renamed to SUM.

• Hardware management of page-table entry Accessed and Dirty bits has been made optional;

simpler implementations may trap to software to set them.

剩余134页未读,继续阅读

fastwind1985

- 粉丝: 0

- 资源: 9

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0