没有合适的资源?快使用搜索试试~ 我知道了~

首页BCM53333-DS06-R.pdf

资源详情

资源评论

资源推荐

53333-DS06-R

5300 California Avenue • Irvine, CA 92617 • Phone: 949-926-5000 • Fax: 949-926-5203 December 19, 2014

Data Sheet

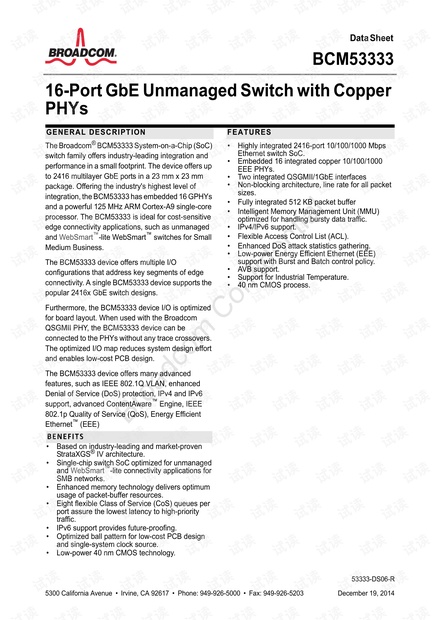

BCM53333

16-Port GbE Unmanaged Switch with Copper

PHYs

GENERAL DESCRIPTION

FEATURES

The Broadcom

®

BCM53333 System-on-a-Chip (SoC)

switch family offers industry-leading integration and

performance in a small footprint. The device offers up

to 2416 multilayer GbE ports in a 23 mm x 23 mm

package. Offering the industry's highest level of

integration, the BCM53333 has embedded 16 GPHYs

and a powerful 125 MHz ARM Cortex-A9 single-core

processor. The BCM53333 is ideal for cost-sensitive

edge connectivity applications, such as unmanaged

and WebSmart

™

-lite WebSmart

™

switches for Small

Medium Business.

The BCM53333 device offers multiple I/O

configurations that address key segments of edge

connectivity. A single BCM53333 device supports the

popular 2416x GbE switch designs.

Furthermore, the BCM53333 device I/O is optimized

for board layout. When used with the Broadcom

QSGMII PHY, the BCM53333 device can be

connected to the PHYs without any trace crossovers.

The optimized I/O map reduces system design effort

and enables low-cost PCB design.

The BCM53333 device offers many advanced

features, such as IEEE 802.1Q VLAN, enhanced

Denial of Service (DoS) protection, IPv4 and IPv6

support, advanced ContentAware

™

Engine, IEEE

802.1p Quality of Service (QoS), Energy Efficient

Ethernet

™

(EEE)

• Highly integrated 2416-port 10/100/1000 Mbps

Ethernet switch SoC.

• Embedded 16 integrated copper 10/100/1000

EEE PHYs.

• Two integrated QSGMII/1GbE interfaces

• Non-blocking architecture, line rate for all packet

sizes.

• Fully integrated 512 KB packet buffer

• Intelligent Memory Management Unit (MMU)

optimized for handling bursty data traffic.

• IPv4/IPv6 support.

• Flexible Access Control List (ACL).

• Enhanced DoS attack statistics gathering.

• Low-power Energy Efficient Ethernet (EEE)

support with Burst and Batch control policy.

• AVB support.

• Support for Industrial Temperature.

• 40 nm CMOS process.

• Based on industry-leading and market-proven

StrataXGS

®

IV architecture.

• Single-chip switch SoC optimized for unmanaged

and WebSmart

™

-lite connectivity applications for

SMB networks.

• Enhanced memory technology delivers optimum

usage of packet-buffer resources.

• Eight flexible Class of Service (CoS) queues per

port assure the lowest latency to high-priority

traffic.

• IPv6 support provides future-proofing.

• Optimized ball pattern for low-cost PCB design

and single-system clock source.

• Low-power 40 nm CMOS technology.

BENEFITS

Broadcom Confidential

Broadcom

®

, the pulse logo, Connecting everything

®

, the Connecting everything logo, BroadScale

®

,

ContentAware

™

, Ethernet@Wirespeed

™

, and StrataXGS

®

IV are among the trademarks of Broadcom

Corporation and/or its affiliates in the United States, certain other countries and/or the EU. Any other trademarks

or trade names mentioned are the property of their respective owners.

This data sheet (including, without limitation, the Broadcom component(s) identified herein) is not designed,

intended, or certified for use in any military, nuclear, medical, mass transportation, aviation, navigations,

pollution control, hazardous substances management, or other high-risk application. BROADCOM PROVIDES

THIS DATA SHEET “AS-IS,” WITHOUT WARRANTY OF ANY KIND. BROADCOM DISCLAIMS ALL

WARRANTIES, EXPRESSED AND IMPLIED, INCLUDING, WITHOUT LIMITATION, THE IMPLIED

WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-

Broadcom Corporation

5300 California Avenue

Irvine, CA 92617

© 2014 by Broadcom Corporation

All rights reserved

Printed in the U.S.A.

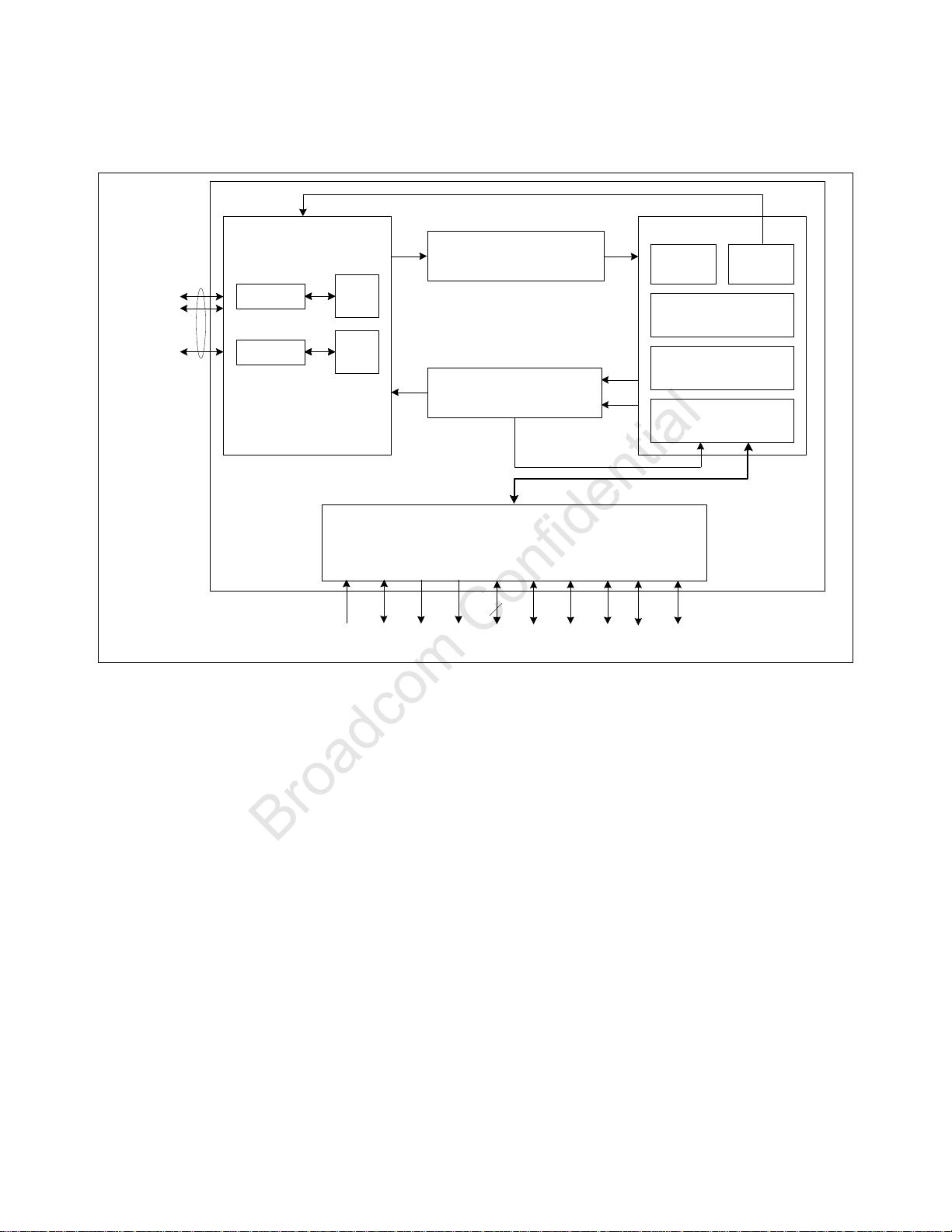

Figure 1: BCM53333 Functional Block Diagram

MMU

8 x 1G

MAC

8 x GPHY

8 x 1G

MAC

8 x GPHY

16 GbE

.

.

.

Egress Pipeline

(EP)

Ingress Pipeline

(IP)

Ethernet

Switch Controller

Scheduling

Queueing

Admission

Control

Flow

Control

512 KB Packet Buffer

(4K x 128B)

Cortex-A9

125 MHz

I$ = 32K / D$ = 32K

L2$ = 128 KB

SPI

Serial

Flash

RS

-

232

JTAG

GPIO

8

MDIO

LED

Serial

LED

Parallel

Reset

BSC

I

2

C/

Broadcom Confidential

Revision HistoryBCM53333 Data Sheet

Broadcom

®

16-Port GbE Unmanaged Switch with Copper PHYs

December 19, 2014 • 53333-DS06-R Page 3

Revision History

Revision Date Change Description

53333-DS06-R 12/19/14 Updated:

• Table 34: “Ordering Information for RoHS6 Devices with Exemption 15

(Eutectic Bumps Internally Between Die and Substrate),” on page 93

Added:

• Table 33: “Ordering Information for RoHS6 Devices (Contact Broadcom

for Availability),” on page 93

53333-DS05-R 07/18/14 Updated:

• Change Advanced Data Sheet to Data Sheet.

• “Power Supply Current” on page 79 - Added power column to Power

Supply Current Tables.

Broadcom Confidential

Revision HistoryBCM53333 Data Sheet

Broadcom

®

16-Port GbE Unmanaged Switch with Copper PHYs

December 19, 2014 • 53333-DS06-R Page 4

53333-DS04-R 04/23/14 Updated:

• Changed AVS0 pin description to ‘Reserved’ in Table 8: “BCM5333X Hardware

Signals,” on page 54

• Table 12: “Operating Conditions,” on page 77 - Remove 0.97V option and

change 1.2V to ±3%.

• Table 17: “BSC Signals,” on page 81

– Input Low Voltage from 1.08V to 0.3*VDDO.

– Input High Voltage from 2.1V to 0.7*VDDO.

• Table 23: “SPI Slave Fast Mode Timing,” on page 86 - Change t_hold from 0 to

4 ns.

• Table 24: “MDC/MDIO Timing,” on page 87

– MDC Cycle Time from 74 to 80 ns.

– MDIO Setup Time from 10 to 20 ns.

– MDIO hold time from 0 to 10 ns.

• Table 26: “QSPI BSPI Mode Master Interface Timing Specifications,” on page 89

–T

WH

from ½T

CK

-3 to 0.4*T

CK

and max. 0.6*T

CK.

–T

WL

from ½T

CK

-3 to 0.4*T

CK

and max. 0.6*T

CK.

– Updated footnote a.

• Table 27: “QSPI MSPI Mode Master Interface Timing Specifications,” on page 90

–T

WH

from ½T

CK

-3 to 0.4*T

CK

and max. 0.6*T

CK.

–T

WL

from 1/0.6F

CLK

to 0.4*T

CK

and max. 0.6*T

CK.

– Updated footnote a.

• Table 29: “XTALP/XTALN Input Requirements,” on page 92

– Change V

IN

Min. from 500 to 800 mV

pp diff

.

– Change "Internal 100Ω termination" to "External 100Ω termination required.

• Table 30: “LC_PLL0_REFCLK Input Requirements,” on page 93

– Remove Min/Max Intput Voltage V

IL

and V

IH

– Change V

IN

Min. from 500 to 700 mV

pp

diff

• Table 31: “EXT_QS2_CLKP/N Output Specifications,” on page 94

– Change V

ODIFF

Min from 500 to 300 mV

pp

diff and Max from 2000 to 500

mV

pp

diff.

– Remove Min/Max Output Voltage V

OL

and V

OH

– Change EXT_QS2_CLK Rise/Fall time from 1.0 to 0.22 ns Max.

– Change EXT_QS2_CLK jitter from 0.5 to 2 ps Max.

– Remove Note: Internal 100Ω termination.

– Measured with 50Ω termination as recommended in the Hardware Design

Guide.

• Table 35: “AC-JTAG Transmit Setting (Driver Bias Current),” on page 98 - the

Transmit Amplitude of the entire table.

• “Power Supply Current” on page 79

• Section 9: “Thermal Characteristics,” on page 99

Removed:

• Hardware strapping pin description to enable Super Isolate Mode.

• MII Interface Timing.

Revision Date Change Description

Broadcom Confidential

Revision HistoryBCM53333 Data Sheet

Broadcom

®

16-Port GbE Unmanaged Switch with Copper PHYs

December 19, 2014 • 53333-DS06-R Page 5

53333-DS03-R 07/03/13 Updated:

• For power sequencing add requirement to power up the core VDDC at

the same time or before GP-AVDDL SUPPLY.

• Update Parallel LED Interface.

• Table 1: “5615X_5333X_5334XCT SoC Port Configurations,” on

page 14 - Remove DSCP

• Table 2: “Switch Features,” on page 29 - Adjust table sizes.

• Table 3: “Switch Internal Memory Table,” on page 35 - Remove DSCP

• Table 15: “5615X_5333X_5334XCT Hardware Signals,” on page 83 -

Add PU/PD

• Section 7: “Pin List Description” - Add PU/PD

53333-DS02-R 04/05/13 Updated:

• Update entire document.

• “Pin List by Signal Name” on page 143

• “AC Characteristics” on page 192

53333-DS01-R 12/21/12 Updated entire document.

53333-DS00-R 09/26/12 Initial release

Revision Date Change Description

Broadcom Confidential

剩余99页未读,继续阅读

cvskill

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0