基于基于FPGA的运动目标检测系统设计的运动目标检测系统设计

针对运动目标检测技术在国防军工领域的广泛应用,设计了一种基于FPGA的运动目标检测系统。利用CCD摄像

头采集带有运动目标的视频图像,并将采集后视频图像传输给SAA7113H进行解码,再将解码后的数字信号供

给FPGA实现帧间差分算法以达到运动目标检测的目的,之后将数据传输给SAA7121H芯片进行编码,并将编码

后的视频数据在显示单元中显示。实验测试结果表明,该运动目标检测系统能够实时地检测出运动目标,稳定

性高,实时性好。

0 引言引言

近年来,大规模集成电路的快速发展使其在

目前,运动目标检测最常用的是

1 系统的总体结构系统的总体结构

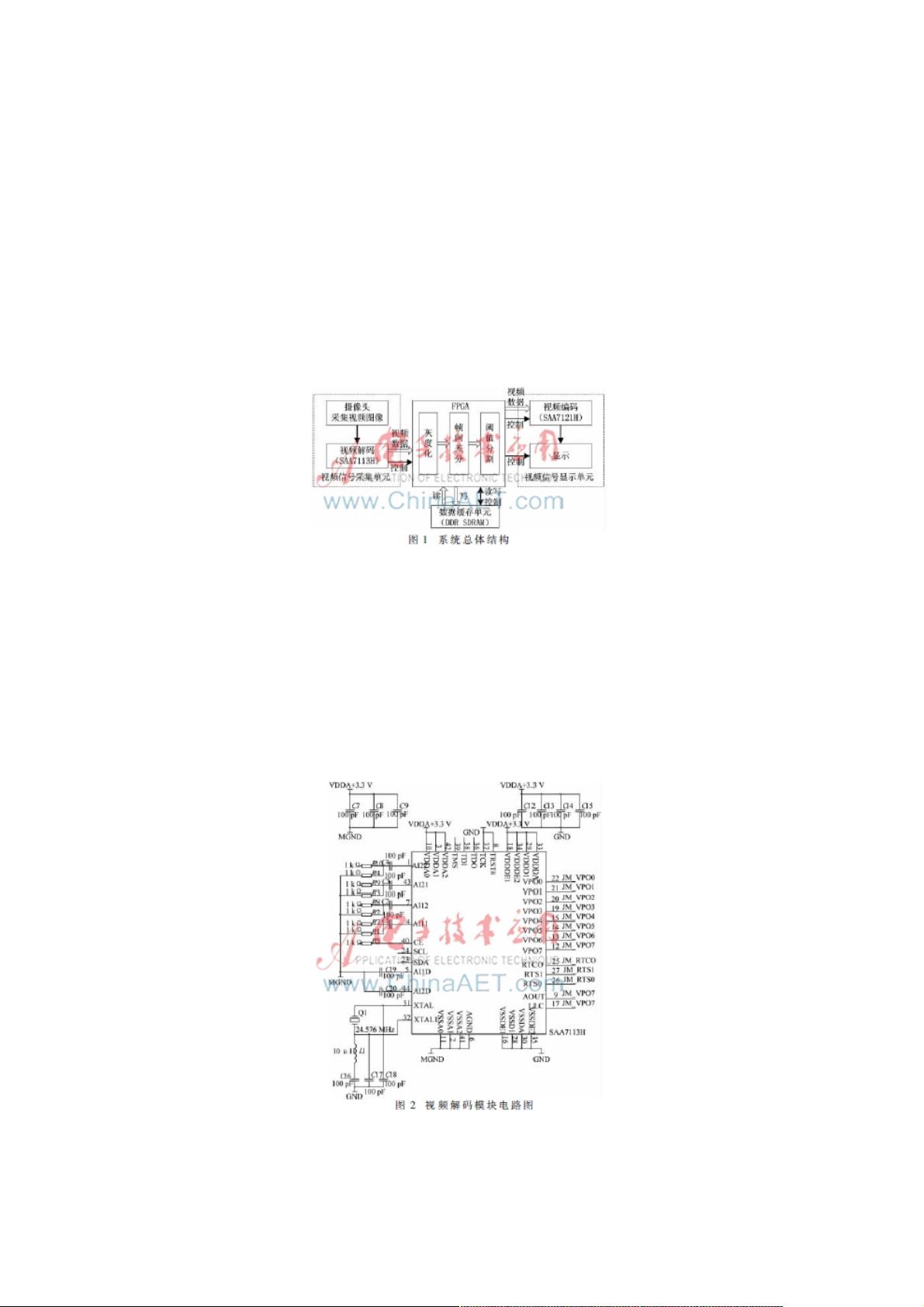

整个系统由视频信号采集单元、控制和算法实现单元、数据缓存单元和视频信号显示单元四部分组成,如图1所示。

视频采集单元在FPGA的控制下,对带有运动目标的模拟视频进行采集,并转换为数字视频信号传输到FPGA进一步处

理;FPGA主要负责对其他模块进行功能控制以及对传入的视频信号进行灰度化、帧间差分和阈值分割,以实现运动目标的检

测; 数据缓存单元是在FPGA的控制下,完成对视频图像数据的缓存,配合FPGA进行图像处理;视频信号显示单元是在

FPGA的控制下对处理前后的视频图像进行显示,可以直观地观察检测效果。

2 系统硬件设计系统硬件设计

2.1 视频信号采集单元视频信号采集单元

本系统使用的CCD(Charge Coupled Device)相机输出PAL制式视频。而FPGA只能处理数字视频信号,因此需要将

PAL制式信号转换为标准的数字视频格式。飞利浦公司研制的SAA7113H是一款功能强大的9位视频解码芯片,它可以自动检

测视频制式,并且可以输出包含YUV4:2:2在内的不同格式的数字视频。图2所示为本系统中视频解码模块的电路图。

本设计仅使用4路输入通道中的1路即可,将SAA7113H解码后的数字视频信号传输给FPGA进行下一步处理,片选信号

CE接高电平时,芯片选通;像素时钟接口LLC外接27 MHz时钟信号。

2.2 视频图像缓存单元视频图像缓存单元

在完成运动目标检测的过程中,需要至少缓存一帧图像。为了节省FPGA内部有限的存储资源,缓存数据量巨大的视频图

像时,本系统采用外接DDR SDRAM来进行数据缓存。Hynix公司研制的存储容量为2 M×4 Banks×16 bit的

HY57V281620FTP-H型号SDRAM满足本设计要求。其各引脚功能如表1所示。其中WE#无效时进行读操作;A0~A11为行列

评论0