没有合适的资源?快使用搜索试试~ 我知道了~

首页msp432p401r数据手册.pdf

SimpleLink MSP432P401x 微控制器 (MCU) 是具有集成 16 位精密 ADC 的优化型无线主机 MCU, 可借助FPU 和 DSP 扩展提供超低功耗性能, 其中包括 80μA/MHz 的工作功率和 660nA 的待机功耗。 作为优化的无线主机 MCU, MSP432P401x 可让开发人员向 基于 SimpleLink 无线连接解决方案的应用中添加高精度模拟和存储器扩展。 MSP432P401x 器件是 SimpleLink 微控制器 (MCU) 平台的一部分, 其中包括 Wi-Fi®、 低功耗 Bluetooth®、1GHz 以下器件和主机 MCU。 它们都共用配有单核软件开发套件 (SDK) 和丰富工具集的通用、 易用型开发环境。一次性集成 SimpleLink 平台后, 用户可以将产品组合中器件的任何组合添加至您的设计中。 SimpleLink 平台的最终目标是确保设计要求变更时, 完全重复使用代码。

资源详情

资源评论

资源推荐

Product

Folder

Order

Now

Technical

Documents

Tools &

Software

Support &

Community

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications,

intellectual property matters and other important disclaimers. PRODUCTION DATA.

English Data Sheet: SLAS826

MSP432P401R, MSP432P401M

ZHCSET7G –MARCH 2015–REVISED SEPTEMBER 2017

MSP432P401R、、MSP432P401M SimpleLink™ 混混合合信信号号微微控控制制器器

1 器器件件概概述述

1

1.1 特特性性

1

• 内核

– ARM

®

32 位 Cortex

®

-M4F CPU,具有浮点单元

和存储器保护单元

– 频率最高达 48MHz

– ULPBench™基准:

– 192.3 ULPMark™-CP

– 性能基准:

– 3.41 CoreMark/MHz

– 1.22 DMIPS/MHz (Dhrystone 2.1)

• 高级低功耗模拟 特性

– 具有 16 位精度和高达 1Msps 速率的 SAR 模数

转换器 (ADC)

– 差分和单端输入

– 两个窗口比较器

– 多达 24 个输入通道

– 内部电压基准,典型稳定度为 10ppm/°C

– 两个模拟比较器

• 存储器

– 高达 256KB 的闪存主存储器(分为两组,支持擦

除期间同时读取/执行)

– 16KB 的闪存信息存储器(用于引导加载程序

(BSL)、标签长度值 (TLV) 和闪存邮箱)

– 高达 64KB 的静态随机存取存储器 (SRAM)(包

括 6KB 的备用存储器)

– 32KB 的 ROM,含有 MSP432™外设驱动程序库

• 超低功耗工作模式

– 工作状态:80µA/MHz

– 低频工作状态:128kHz 时为 83µA

– LPM3(带 RTC):660nA

– LPM3.5(带 RTC):630nA

– LPM4:500nA

– LPM4.5:25nA

• 开发套件和软件(请参阅

工具和软件

)

– MSP-EXP432P401R LaunchPad™ 开发套件

– MSP-TS432PZ100 100 引脚目标板

– SimpleLink™ MSP432 软件开发套件 (SDK)

• 工作特性

– 宽电源电压范围:1.62V 至 3.7V

– 温度范围(环境):-40°C 至 85°C

• 灵活计时 特性

– 可调内部数控振荡器 (DCO)(最高达 48MHz)

– 32.768kHz 低频晶振支持 (LFXT)

– 支持最高达 48MHz 的高频晶体 (HFXT)

– 低频内部基准振荡器 (REFO)

– 超低功耗低频内部振荡器 (VLO)

– 模块振荡器 (MODOSC)

– 系统振荡器 (SYSOSC)

• 代码安全性 特性

– JTAG 和 SWD 锁定机制

– IP 保护(多达四个安全闪存区,每个区均可配置

起始地址和大小)

• 增强型系统 特性

– 可编程的电源电压监控与监测

– 多级复位,能够更好地控制应用以及调试

– 8 通道直接存储器访问 (DMA)

– 具备日历和报警功能的 RTC

• 时序和控制

– 多达四个 16 位定时器,每个定时器都有多达五

个捕捉/比较/PWM 功能

– 两个 32 位定时器,每个定时器都有中断生成功

能

• 串行通信

– 多达四个 eUSCI_A 模块

– 支持自动波特率侦测的通用异步收发器

(UART)

– IrDA 编码和解码

– 串行通信接口 (SPI)(最高达 16Mbps)

– 多达四个 eUSCI_B 模块

– I

2

C(支持多从器件寻址)

– SPI(最高达 16Mbps)

• 灵活的输入/输出 (I/O) 特性

– 超低泄漏电流 I/O(最大值为 ±20nA)

– 所有 I/O 都具有电容式触控功能

– 多达 48 个具有中断和唤醒功能的 I/O

– 多达 24 个具有端口映射功能的 I/O

– 八个具有毛刺脉冲滤波功能的 I/O

2

MSP432P401R, MSP432P401M

ZHCSET7G –MARCH 2015–REVISED SEPTEMBER 2017

www.ti.com.cn

器件概述

版权 © 2015–2017, Texas Instruments Incorporated

• 加密和数据完整性加速器

– 128 位、192 位或 256 位高级加密标准 (AES) 加

密和解密加速器

– 32 位硬件循环冗余校验 (CRC) 引擎

• JTAG 和调试支持

– 4 引脚 JTAG 和 2 引脚 SWD 调试接口

– 串行线迹

– 电源调试和应用 性能评测

1.2 应应用用

• 工业与自动化

– 玻璃破裂探测器

– 智能恒温器

– 门禁面板

– 气体监测器

– 现场发送器

– 过程自动化

– 家庭自动化

• 计量

– 流量计

– 电表

– 通信模块

• 测试和测量

– 数字万用表

– 无线数字万用表

– 非接触式和手持式数字仪表

• 医疗和健身

– 手表

– 活动监视器

– 健身配件

– 血糖仪

• 消费类电子产品

– 移动设备

– 传感器集线器

1.3 说说明明

SimpleLink MSP432P401x 微控制器 (MCU) 是具有集成 16 位精密 ADC 的优化型无线主机 MCU,可借助

FPU 和 DSP 扩展提供超低功耗性能,其中包括 80μA/MHz 的工作功率和 660nA 的待机功耗。作为优化的

无线主机 MCU,MSP432P401x 可让开发人员向 基于 SimpleLink 无线连接解决方案的应用中添加高精度模

拟和存储器扩展。

MSP432P401x 器件是 SimpleLink 微控制器 (MCU) 平台的一部分,其中包括 Wi-Fi

®

、低功耗 Bluetooth

®

、

1GHz 以下器件和主机 MCU。它们都共用配有单核软件开发套件 (SDK) 和丰富工具集的通用、易用型开发

环境。一次性集成 SimpleLink 平台后,用户可以将产品组合中器件的任何组合添加至您的设计中。

SimpleLink 平台的最终目标是确保设计要求变更时,完全重复使用代码。更多详细信息,请访问

www.ti.com/simplelink。

MSP432P401x 器件具有配套的综合生态系统,其中包含工具、软件、文档、培训和支持,旨在帮助您迅速

开始开发。只需 MSP-EXP432P401R LaunchPad 开发套件或 MSP-TS432PZ100 目标插座板(附带 MCU

示例)以及免费的 SimpleLink MSP432 SDK,即可开始开发。

(1) 要获得所有可用器件的最新部件、封装和订购信息,请参见

封装选项附录

(节 9)或浏览 TI 网站

www.ti.com.cn。

(2) 这里显示的尺寸为近似值。要获得包含误差值的封装尺寸,请参见

机械数据

(节 9)。

器器件件信信息息

(1)

器器件件型型号号 封封装装 封封装装尺尺寸寸

(2)

MSP432P401RIPZ

MSP432P401MIPZ

LQFP (100) 14mm x 14mm

MSP432P401RIZXH

MSP432P401MIZXH

NFBGA (80) 5mm x 5mm

MSP432P401RIRGC

MSP432P401MIRGC

VQFN (64) 9mm x 9mm

PCM

Power

Control

Manager

PSS

Power

Supply

System

CS

Clock

System

RTC_C

Real-Time

Clock

WDT_A

Watchdog

Timer

I/O Ports

P1 to P10

78 I/Os

I/O Ports

PJ

6 I/Os

Flash

256KB

128KB

RSTCTL

Reset

Controller

SYSCTL

System

Controller

AES256

Security

Encryption,

Decryption

CRC32

Precision

ADC

1 Msps,

SAR A/D

Comp_E0,

Comp_E1

Analog

Comparator

REF_A,

Voltage

Reference

TA0, TA1,

TA2,TA3

Timer_A

16 Bit

5 CCR

Timer32

2 x 32-bit

Timers

eUSCI_A0,

eUSCI_A1,

eUSCI_A2,

eUSCI_A3

(UART,

IrDA, SPI)

eUSCI_B0,

eUSCI_B1,

eUSCI_B2,

eUSCI_B3

(I C, SPI)

2

Bus

Control

Logic

DMA

8 Channels

Capacitive Touch I/O 0,

Capacitive Touch I/O 1

Address

Data

LFXIN,

HFXIN

LFXOUT,

HFXOUT

DCOR

LPM3.5 Domain

P1.x to P10.x

PJ.x

Backup

Memory

SRAM

6KB

CPU

MPU

NVIC, SysTick

FPB, DWT

ARM

Cortex-M4F

ITM, TPIU

JTAG, SWD

SRAM

(includes

Backup

Memory)

64KB

32KB

ROM

(Peripheral

Driver

Library)

32KB

Copyright © 2017 Texas Instruments Incorporated

3

MSP432P401R, MSP432P401M

www.ti.com.cn

ZHCSET7G –MARCH 2015–REVISED SEPTEMBER 2017

器件概述

版权 © 2015–2017, Texas Instruments Incorporated

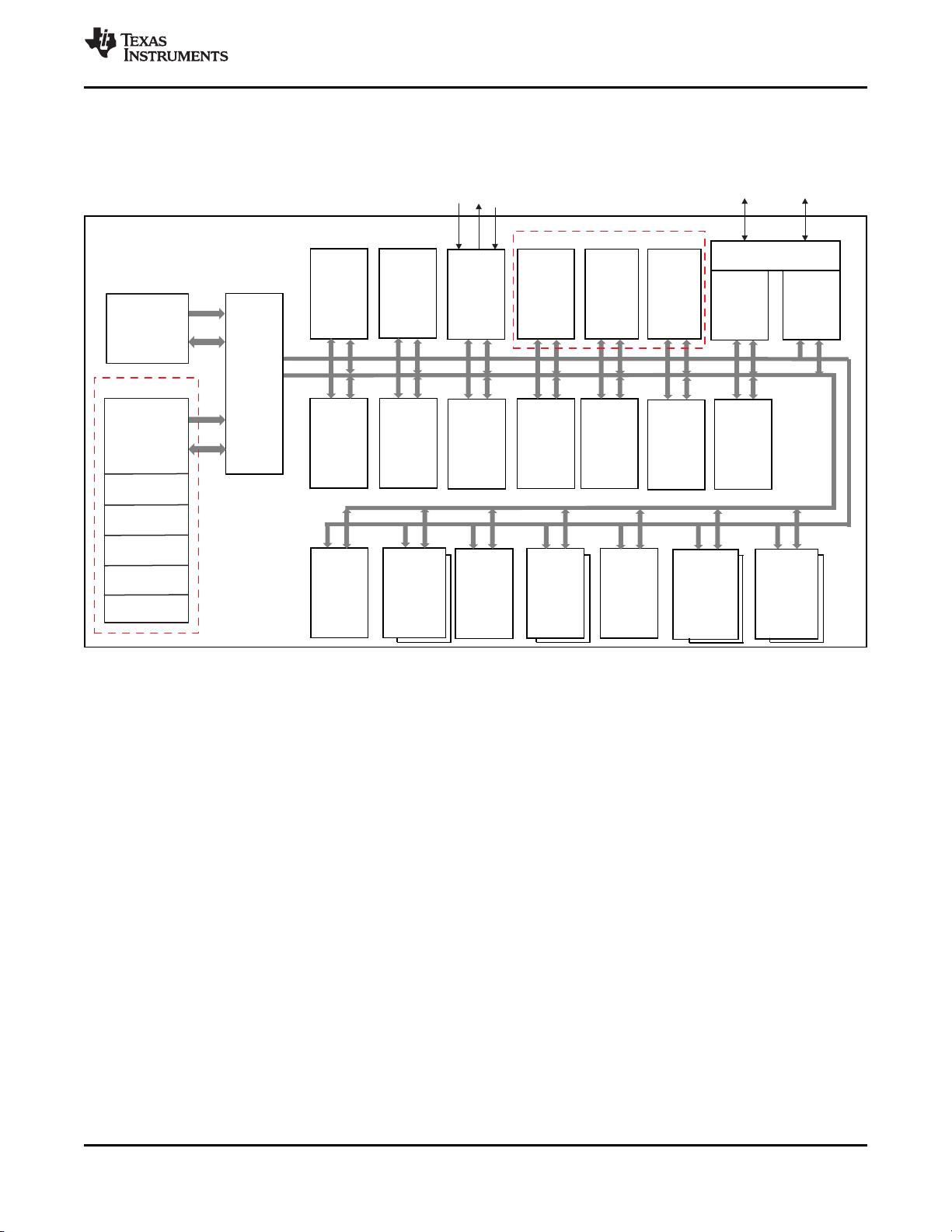

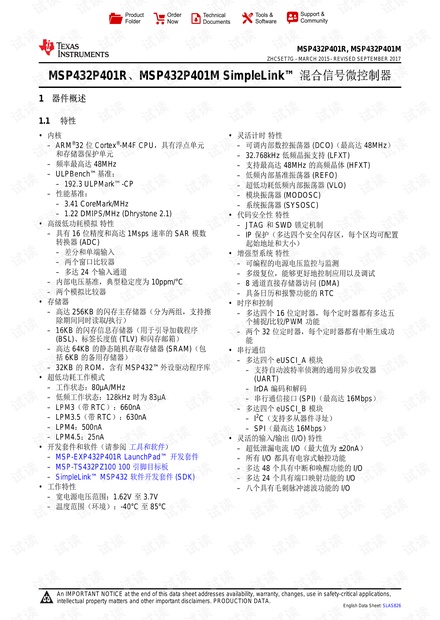

1.4 功功能能方方框框图图

图 1-1 给出了 MSP432P401R 和 MSP432P401M 器件的功能框图。

图图 1-1. MSP432P401R,,MSP432P401M 功功能能框框图图

CPU 和器件中的所有外设通过共同的先进高性能总线 (AHB) 矩阵彼此交互。在某些情况下,AHB 端口和外

设之间存在电桥。从存储器映射的角度来看,这些电桥对于应用而言是透明的,因此未显示在框图中。

4

MSP432P401R, MSP432P401M

ZHCSET7G –MARCH 2015–REVISED SEPTEMBER 2017

www.ti.com.cn

内容

版权 © 2015–2017, Texas Instruments Incorporated

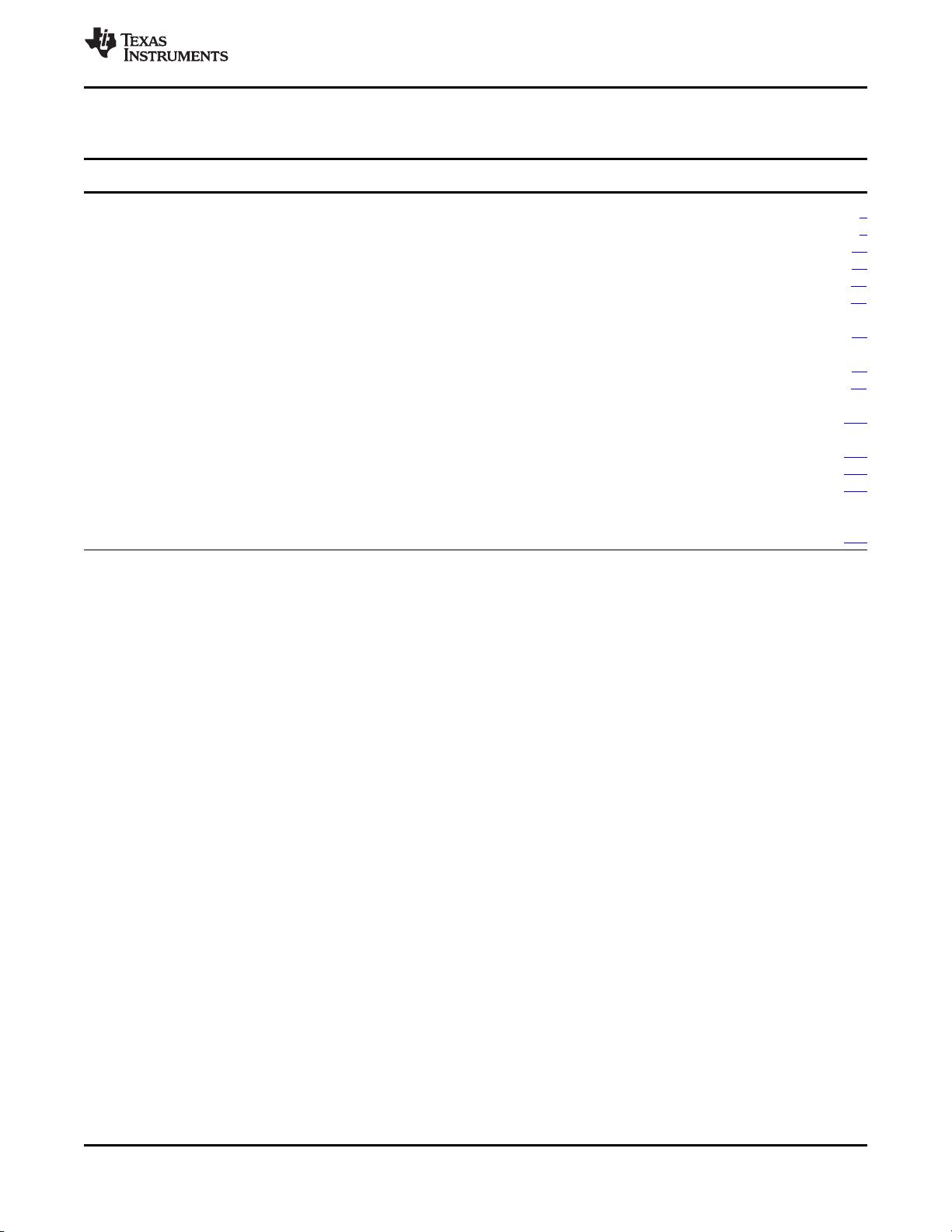

内内容容

1 器器件件概概述述 .................................................... 1

1.1 特性 ................................................... 1

1.2 应用 ................................................... 2

1.3 说明 ................................................... 2

1.4 功能方框图............................................ 3

2 修修订订历历史史记记录录............................................... 5

3 Device Comparison ..................................... 6

3.1 Related Products ..................................... 7

4 Terminal Configuration and Functions.............. 8

4.1 Pin Diagrams ......................................... 8

4.2 Pin Attributes ........................................ 11

4.3 Signal Descriptions.................................. 17

4.4 Pin Multiplexing ..................................... 27

4.5 Buffer Types......................................... 27

4.6 Connection for Unused Pins ........................ 27

5 Specifications........................................... 28

5.1 Absolute Maximum Ratings ........................ 28

5.2 ESD Ratings ........................................ 28

5.3 Recommended Operating Conditions............... 28

5.4 Recommended External Components ............. 29

5.5 Operating Mode V

CC

Ranges ....................... 29

5.6 Operating Mode CPU Frequency Ranges ......... 30

5.7 Operating Mode Peripheral Frequency Ranges .... 30

5.8 Operating Mode Execution Frequency vs Flash

Wait-State Requirements ........................... 31

5.9 Current Consumption During Device Reset......... 31

5.10 Current Consumption in LDO-Based Active

Modes – Dhrystone 2.1 Program ................... 31

5.11 Current Consumption in DC-DC-Based Active

Modes – Dhrystone 2.1 Program ................... 32

5.12 Current Consumption in Low-Frequency Active

Modes – Dhrystone 2.1 Program ................... 32

5.13 Typical Characteristics of Active Mode Currents for

CoreMark Program.................................. 33

5.14 Typical Characteristics of Active Mode Currents for

Prime Number Program............................. 34

5.15 Typical Characteristics of Active Mode Currents for

Fibonacci Program .................................. 35

5.16 Typical Characteristics of Active Mode Currents for

While(1) Program ................................... 36

5.17 Typical Characteristics of Low-Frequency Active

Mode Currents for CoreMark Program.............. 37

5.18 Current Consumption in LDO-Based LPM0 Modes. 38

5.19 Current Consumption in DC-DC-Based LPM0

Modes ............................................... 38

5.20 Current Consumption in Low-Frequency LPM0

Modes ............................................... 38

5.21 Current Consumption in LPM3, LPM4 Modes ...... 39

5.22 Current Consumption in LPM3.5, LPM4.5 Modes .. 39

5.23 Current Consumption of Digital Peripherals ........ 40

5.24 Thermal Resistance Characteristics ................ 40

5.25 Timing and Switching Characteristics ............... 41

6 Detailed Description ................................... 90

6.1 Overview ............................................ 90

6.2 Processor and Execution Features ................. 90

6.3 Memory Map ........................................ 91

6.4 Memories on the MSP432P401x .................. 111

6.5 DMA................................................ 114

6.6 Memory Map Access Details ...................... 115

6.7 Interrupts........................................... 117

6.8 System Control..................................... 119

6.9 Peripherals......................................... 124

6.10 Code Development and Debug .................... 134

6.11 Performance Benchmarks ......................... 136

6.12 Input/Output Diagrams ............................. 138

6.13 Device Descriptors (TLV) .......................... 176

6.14 Identification........................................ 178

7 Applications, Implementation, and Layout ...... 180

7.1 Device Connection and Layout Fundamentals .... 180

7.2 Peripheral and Interface-Specific Design

Information ......................................... 181

8 器器件件和和文文档档支支持持......................................... 183

8.1 入门和下一步....................................... 183

8.2 器件和开发工具命名规则........................... 183

8.3 工具和软件 ......................................... 184

8.4 文档支持 ........................................... 186

8.5 相关链接 ........................................... 187

8.6 社区资源 ........................................... 188

8.7 商标 ................................................ 188

8.8 静电放电警告....................................... 188

8.9 出口管制提示....................................... 188

8.10 术语表 .............................................. 188

9 机机械械、、封封装装和和可可订订购购信信息息 .............................. 188

5

MSP432P401R, MSP432P401M

www.ti.com.cn

ZHCSET7G –MARCH 2015–REVISED SEPTEMBER 2017

Submit Documentation Feedback

Product Folder Links: MSP432P401R MSP432P401M

修订历史记录

Copyright © 2015–2017, Texas Instruments Incorporated

2 修修订订历历史史记记录录

注:之前版本的页码可能与当前版本有所不同。

Changes from March 8, 2017 to September 26, 2017 Page

• 更新节 1.3,

说明

...................................................................................................................... 2

• 通篇将 ADC 模块的名称从“ADC14”更改为“精密 ADC” .......................................................................... 3

• Added VSW to Table 4-4, Connection for Unused Pins ....................................................................... 27

• Removed MAX values from Section 5.21 and Section 5.22................................................................... 39

• Added 节 5.25.2, Peripheral Register Access Timing ......................................................................... 41

• Changed the MAX value of the df

DCO

/dT parameter in external resistor mode to 60 ppm/°C in Table 5-12, DCO .... 51

• Changed the MAX value of the f

VLO

parameter to 18 kHz in Table 5-14, Internal Very-Low-Power Low-

Frequency Oscillator (VLO) ....................................................................................................... 53

• Changed the MAX value of the "REFO absolute tolerance calibrated" parameter at T

A

= –40°C to 85°C to ±4%

in Table 5-15, Internal-Reference Low-Frequency Oscillator (REFO) in 32.768-kHz Mode .............................. 53

• Changed the TYP and MAX values of the TC

REF+

parameter in Table 5-34, REF_A, Built-In Reference .............. 77

• Removed interrupt-related registers from Port 7 to Port 10 in 表 6-21, Port Registers (Base Address:

0x4000_4C00)...................................................................................................................... 101

• Corrected the bank 0 address range (changed 0x2000_007FF to 0x2000_07FF) in the last paragraph in 节

6.4.2.2, SRAM Bank Retention Configuration and Backup Memory ....................................................... 114

• Clarified DMA access to flash banks in 节 6.5.3, DMA Access Privileges ................................................. 115

• Corrected the mnemonics for the timer functions in 表 6-44 and 表 6-45 ................................................. 125

• Corrected the ADC channel mapping for the Battery Monitor and Temperature Sensor in 表 6-53, Precision ADC

Channel Mapping on 80-Pin ZXH Devices, and 表 6-54, Precision ADC Channel Mapping on 64-Pin RGC

Devices.............................................................................................................................. 133

剩余190页未读,继续阅读

口弟构成

- 粉丝: 11

- 资源: 2

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1