数字IC设计:前端与后端详解及关键工具

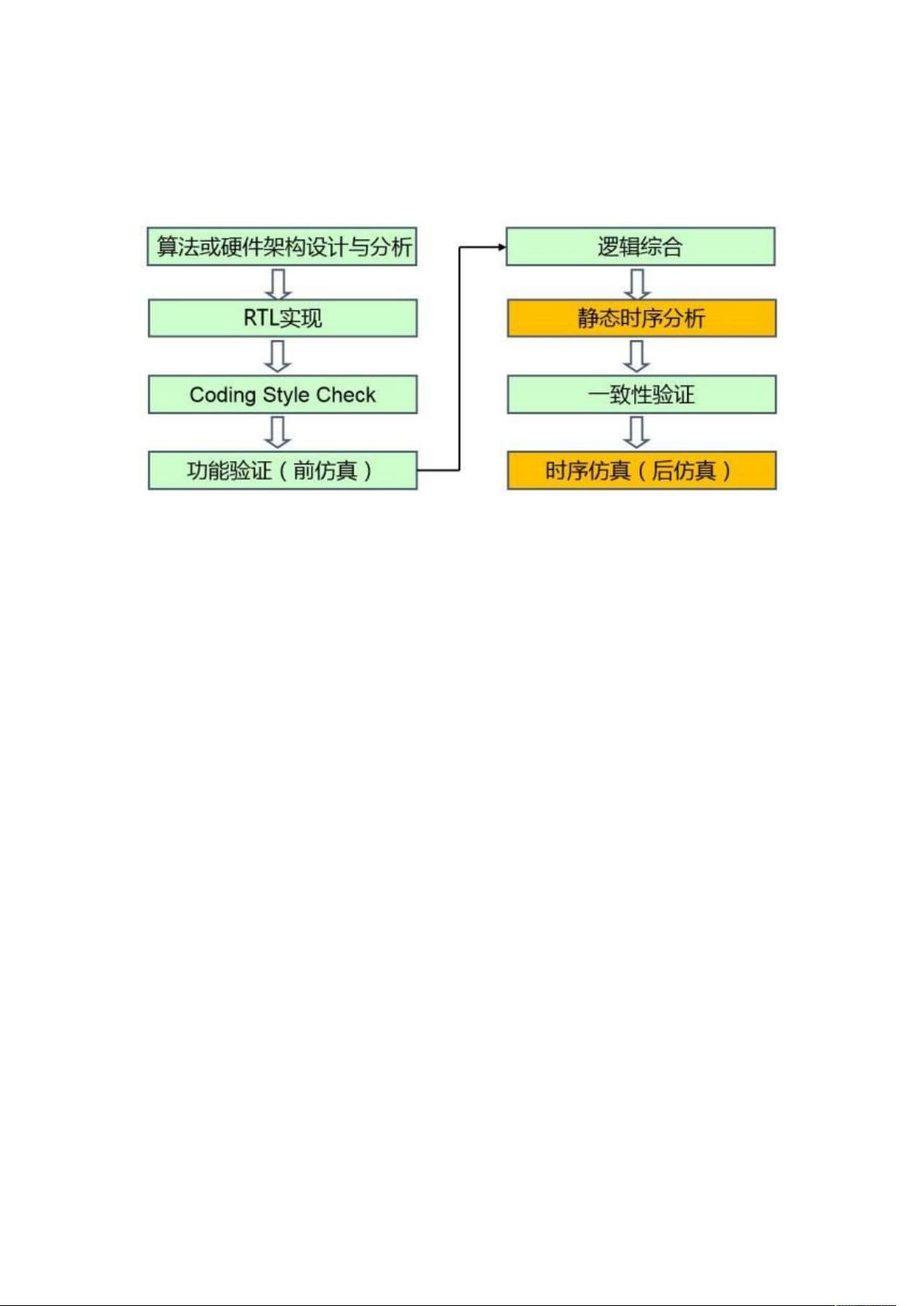

数字IC设计流程是一个复杂且严谨的过程,它主要分为前端设计和后端设计两个阶段。前端设计是数字集成电路设计的关键步骤,主要包括算法或硬件架构设计与分析。在这个阶段,工程师首先通过高层次的分析和建模,利用MATLAB、C++、C、SystemC、SystemVerilog等工具,为芯片中的数字部分构建软件功能模型,并通过大量仿真和调试,为RTL(Register Transfer Level,寄存器传输级)实现提供全局设计指导。前端设计对芯片性能和功耗有着决定性的影响,通常由具备通信、信号处理、计算机或软件背景的工程师主导,也有微电子专业背景的人员参与。

后端设计紧接着RTL实现,即根据前端设计的结果,将高层次描述转化为Verilog HDL代码。在这个过程中,熟练的工程师展现出强大的全局视角,能够同时考虑逻辑综合、静态时序分析(STA)、布局布线(P&R)、设计自动化(DFX)以及功耗分析等因素,确保代码质量高。初学者则需格外注意避免常见的错误,如ClockDomainCross和Lint问题,这时工具如Syglass、LEDA和0inCDC等起到关键作用,特别是在处理局部同步与全局异步设计策略时。

功能验证是设计流程的重要环节,通过Modelsim、VCS、NC-Verilog等工具进行大量仿真实验,旨在发现设计中的错误,特别是功能覆盖率这一关键指标。验证工程师在这个阶段的需求量大增,可能占据数月的时间。

最后,逻辑综合阶段的目标是将RTL代码转化为工艺库相关的网表,主要工具包括DesignCompiler和RTLCompiler,其中DesignCompiler在市场中占据主导地位。这一阶段之前的全部工作都是虚拟的,只有当逻辑综合完成并生成实际的网表后,才能转化为实际的芯片制造流程,进入物理实现阶段。在整个数字IC设计流程中,每个环节都紧密相连,共同确保产品的性能、效率和可靠性。

2019-04-02 上传

2019-10-11 上传

2023-02-28 上传

2021-12-23 上传

2021-11-07 上传

2024-02-21 上传

2023-02-28 上传