JESD204B Subclass1模式时钟设计与调试模式时钟设计与调试

JESD204B协议是用于数据转换器与FPGA/ASIC之间数据传输的高速串行协议,Subclass1模式是该协议完成确

定性延时功能的重要模式。对JESD204B协议Subclass1模式的工作原理和时钟设计要求进行分析,并总结出

Subclass1模式时钟调试方法。利用Xilinx Virtex-7系列FPGA搭建JESD204B自收发链路对该方法进行验证。结

果表明,该时钟调试方法能够满足Subclass1模式的时钟设计要求,保证数据的稳定收发。

0 引言引言

传统的数据转换器采用CMOS和LVDS等并行传输接口,随着数据传输速率的不断提高,并行传输总线逐渐暴露出信号同步

难、偏移大、抗干扰能力弱、布局布线面积大、成本高等问题

[1]

。而高速串行传输总线在以上方面则表现出巨大的优

势。JESD204B协议是国际组织JEDEC提出的一种高速串行协议,用于数据转换器与FPGA/ASIC之间的数据传输。该协议的

最高传输速率为12.5 Gbit/s,具有确定性延时功能,能够保持各通道数据的同步传输

[2-3]

。

Subclass1模式是JESD204B协议完成确定性延时功能的重要模式,如TI、ADI等主流半导体厂商的JESD204B接口数据转

换器产品都具备Subclass1模式。因此正确理解Subclass1确定性延时机制有助于JESD204B接口数据转换器的开发,而正确

的时钟关系是完成Subclass1模式的重中之重。本文分析了Subclass1模式的工作原理以及时钟设计需求,并根据该设计需求

总结出Subclass1时钟调试方法,利用Xilinx Virtex-7系列FPGA XC7VX690T搭建的JESD204B协议自收发回路验证该方法的

有效性

[4]

。

1 JESD204B确定性延时原理确定性延时原理

JESD204B协议将确定性延时定义为数据从发射端的并行端口输入到从接收端并行端口输出所经历的时间。该确定性延时具

有两层含义:(1)延时具有可重复性,不随时间或再同步事件而改变;(2)JESD204B的各个通道之间具有相同的确定性延时,

从而保证多通道数据的同步传输。

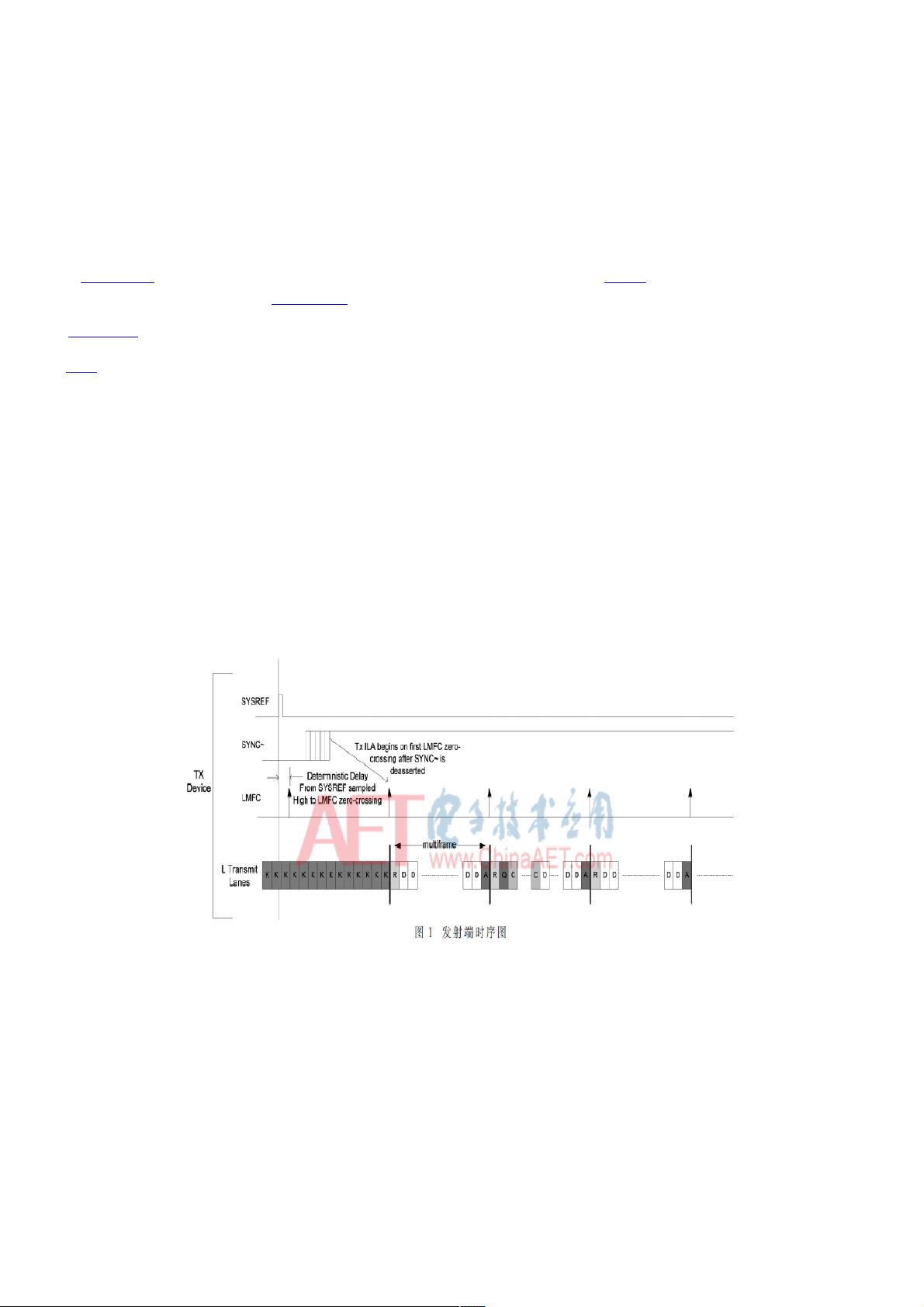

JESD204B协议确定性延时以多帧(Multi Frame)为处理单元,相应的时钟信号为本地多帧时钟(Local Multi Frame

Clock,LMFC)。图1和图2分别是JESD204B协议数据发射和接收过程的时序图。当发射端检测到来自接收端的~SYNC信号的

上升沿时,在下一个LMFC的上升沿开始发射ILA(Initial Lane Alignment)数据以及后续的用户数据。由于各通道数据到达接收

端的时间不同,接收端通过数据缓存器对先到达的数据进行缓存,并在某一特定时刻进行释放。该释放时刻通过RBD(Rx

Buffer Delay)来描述,该参数以帧的个数为计量单位,是指缓存器从接收端的某一LMFC上升沿开始所经历的缓存时间。当缓

存时间等于RBD帧的持续时间时,缓存器对数据进行释放,从而完成各通道之间的同步输出。

评论0