没有合适的资源?快使用搜索试试~ 我知道了~

首页Hynix SLC 128M Nand Flash

资源详情

资源评论

资源推荐

This document is a general product description and is subject to change without notice. Hynix does not assume any responsibility for

use of circuits described. No patent licenses are implied.

Rev 0.4 / Jun. 2007 1

HY27UF(08/16)1G2A Series

1Gbit (128Mx8bit / 64Mx16bit) NAND Flash

1Gb NAND FLASH

HY27UF081G2A

HY27UF161G2A

Rev 0.4 / Jun. 2007 2

HY27UF(08/16)1G2A Series

1Gbit (128Mx8bit / 64Mx16bit) NAND Flash

Document Title

1Gbit (128Mx8bit / 64Mx16bit) NAND Flash Memory

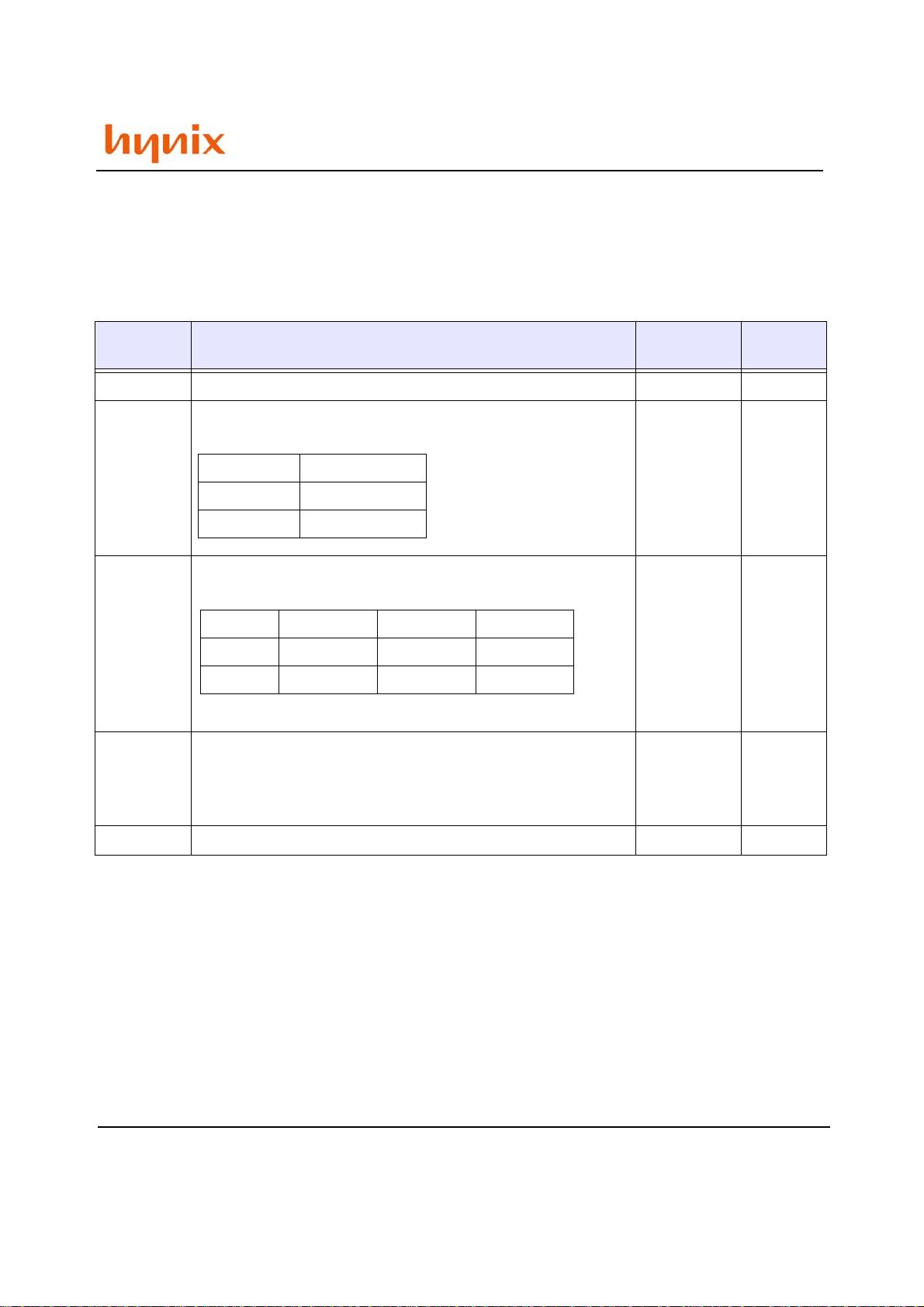

Revision History

Revision

No.

History Draft Date Remark

0.01

Initial Draft.

Dec. 28. 2005 Preliminary

0.1

1) Change NOP

2) Change AC Characteristics

May. 18. 2006 Preliminary

0.2

1) Delete Memory array map

2) Change AC Characteristics

3) Correct copy back function

Oct. 02. 2006 Preliminary

0.3

1) Change 1Gb Package Type

- FBGA package is added

- Figure & dimension are changed

2) Delet Preliminary

Nov. 23. 2006

0.4

1) Correct figure 19

Jun. 11. 2007

tOH

Before 12

After 10

tCS tCEA tREA

Before 25 35 25

After 20 25 20

Rev 0.4 / Jun. 2007 3

HY27UF(08/16)1G2A Series

1Gbit (128Mx8bit / 64Mx16bit) NAND Flash

FEATURES SUMMARY

HIGH DENSITY NAND FLASH MEMORIES

- Cost effective solutions for mass storage applications

NAND INTERFACE

- x8 or x16 bus width.

- Multiplexed Address/ Data

- Pinout compatibility for all densities

SUPPLY VOLTAGE

- VCC = 2.7 to 3.6V : HY27UFxx1G2A

Memory Cell Array

= (2K+64) Bytes x 64 Pages x 1,024 Blocks

= (1K+32) Bytes x 64 Pages x 1,024 Blocks

PAGE SIZE

- x8 device : (2K+64 spare) Bytes

: HY27UF081G2A

- x16 device : (1K+32 spare) Bytes

: HY27UF161G2A

BLOCK SIZE

- x8 device: (128K + 4K spare) Bytes

- x16 device: (64K + 2K spare) Words

PAGE READ / PROGRAM

- Random access: 25us (max.)

- Sequential access: 30ns (min.)

- Page program time: 200us (typ.)

COPY BACK PROGRAM MODE

- Fast page copy without external buffering

CACHE PROGRAM

- Internal (2048+64) Byte buffer to improve the program

throughput

FAST BLOCK ERASE

- Block erase time: 2ms (Typ.)

STATUS REGISTER

ELECTRONIC SIGNATURE

- 1st cycle: Manufacturer Code

- 2nd cycle: Device Code

- 3rd cycle: Internal chip number, Cell Type, Number of

Simultaneously Programmed Pages.

- 4th cycle: Page size, Block size, Organization, Spare

size

SERIAL NUMBER OPTION

CHIP ENABLE DON’T CARE

- Simple interface sith microcontroller

DATA RETENTION

- 100,000 Program/Erase cycles (with 1bit/528byte ECC)

- 10 years Data Retention

PACKAGE

- HY27UF(08/16)1G2A-T(P)

: 48-Pin TSOP1 (12 x 20 x 1.2 mm)

- HY27UF(08/16)1G2A-T (Lead)

- HY27UF(08/16)1G2A-TP (Lead Free)

- HY27UF081G2A-S(P)

: 48-Pin USOP1 (12 x 17 x 0.65 mm)

- HY27UF081G2A-S (Lead)

- HY27UF081G2A-SP (Lead Free)

- HY27UF081G2A-F(P)

: 63-Ball FBGA (9 x 11 x 1.0 mm)

- HY27UF081G2A-F (Lead)

- HY27UF081G2A-FP (Lead Free)

Rev 0.4 / Jun. 2007 4

HY27UF(08/16)1G2A Series

1Gbit (128Mx8bit / 64Mx16bit) NAND Flash

1. SUMMARY DESCRIPTION

The Hynix HY27UF(08/16)1G2A series is a 128Mx8bit with spare 4Mx8 bit capacity. The device is offered in 3.3V Vcc

Power Supply.

Its NAND cell provides the most cost-effective solution for the solid state mass storage market. The memory is divided

into blocks that can be erased independently so it is possible to preserve valid data while old data is erased.

The device contains 1024 blocks, composed by 64 pages consisting in two NAND structures of 32 series connected

Flash cells.

A program operation allows to write the 2112-byte page in typical 200us and an erase operation can be performed in

typical 2ms on a 128K-byte(X8 device) block.

Data in the page can be read out at 30ns cycle time per byte. The I/O pins serve as the ports for address and data

input/output as well as command input. This interface allows a reduced pin count and easy migration towards different

densities, without any rearrangement of footprint.

Commands, Data and Addresses are synchronously introduced using CE

, WE, ALE and CLE input pin. The on-chip Pro-

gram/Erase Controller automates all program and erase functions including pulse repetition, where required, and inter-

nal verification and margining of data.

The modify operations can be locked using the WP

input pin or using the extended lock block feature described later.

The output pin R/B

(open drain buffer) signals the status of the device during each operation. In a system with multi-

ple memories the R/B pins can be connected all together to provide a global status signal.

Even the write-intensive systems can take advantage of the HY27UF(08/16)1G2A extended reliability of 100K pro-

gram/erase cycles by providing ECC (Error Correcting Code) with real time mapping-out algorithm.

The chip could be offered with the CE

don’t care function. This function allows the direct download of the code from

the NAND Flash memory device by a microcontroller, since the CE

transitions do not stop the read operation.

The copy back function allows the optimization of defective blocks management: when a page program operation fails

the data can be directly programmed in another page inside the same array section without the time consuming serial

data insertion phase.

The cache program feature allows the data insertion in the cache register while the data register is copied into the

flash array. This pipelined program operation improves the program throughput when long files are written inside the

memory. A cache read feature is also implemented. This feature allows to dramatically improve the read throughput

when consecutive pages have to be streamed out.

The HYNIX HY27UF(08/16)1G2A series is available in 48 - TSOP1 12 x 20 mm, 48 - USOP 12 x 17 mmm, FBGA 9 x

11 mm.

1.1 Product List

PART NUMBER ORIZATION VCC RANGE PACKAGE

HY27UF081G2A x8

2.7V - 3.6 Volt

63FBGA / 48TSOP1 / 48USOP1

HY27UF161G2A x16 48TSOP1

Rev 0.4 / Jun. 2007 5

HY27UF(08/16)1G2A Series

1Gbit (128Mx8bit / 64Mx16bit) NAND Flash

9&&

966

:3

&/(

$/(

5(

:(

&(

,2a,2

,2a,2[RQO\

5%

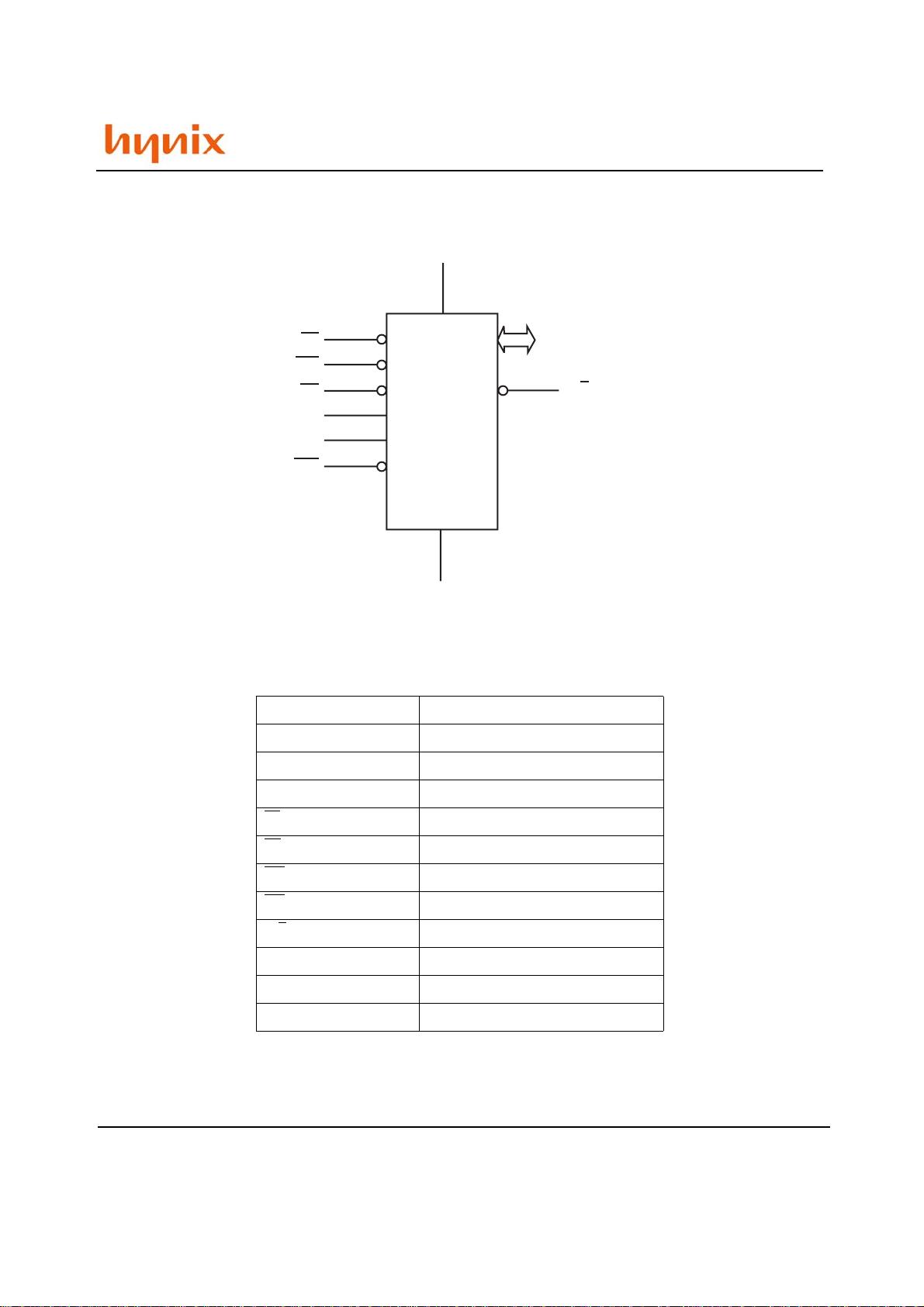

Figure1: Logic Diagram

IO15 - IO8 Data Input / Outputs (x16 only)

IO7 - IO0 Data Inputs / Outputs

CLE Command latch enable

ALE Address latch enable

CE

Chip Enable

RE Read Enable

WE Write Enable

WP Write Protect

R/B Ready / Busy

Vcc Power Supply

Vss Ground

NC No Connection

Table 1: Signal Names

剩余45页未读,继续阅读

star78

- 粉丝: 16

- 资源: 44

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1