没有合适的资源?快使用搜索试试~ 我知道了~

首页TI EtherCAT主站实现方案

TI EtherCAT主站实现方案

TI官方的Tether CAT主站实现方案,详细的可以到其官网上了解。EtherCAT(以太网控制自动化技术)是一个开放架构,以以太网为基础的现场总线系统,其名称的CAT为控制自动化技术(Control Automation Technology)字首的缩写。EtherCAT是确定性的工业以太网,最早是由德国的Beckhoff公司研发。

资源详情

资源评论

资源推荐

1

TIDUBZ1B–June 2016–Revised October 2016

Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

EtherCAT

®

Master Reference Design for Sitara™ AM57x Gigabit Ethernet

and PRU-ICSS with Time-Triggered Send

TI Designs

EtherCAT

®

Master Reference Design for Sitara™ AM57x

Gigabit Ethernet and PRU-ICSS with Time-Triggered Send

All trademarks are the property of their respective owners.

TI Designs

This TI Design details an EtherCAT

®

(EC) Master

interface operating on the Sitara™ AM572x processor

using the EC-Master stack from acontis. This

EtherCAT Master solution can be used for EtherCAT-

based PLC or motion control applications. EtherCAT

Master is profiled on the Gigabit Ethernet ports and the

PRU-ICSS Ethernet ports of the AM572x processor to

give designers flexibility to use any of the two Gigabit

Ethernet ports or four PRU-ICSS Ethernet ports on the

device. The EtherCAT Master implementation can

achieve less than 100-µs cycle times for both the

gigabit and the PRU-ICSS Ethernet ports.

Time-triggered send (TTS) can be enabled on the

PRU-ICSS to reduce jitter, achieve shorter cycle times,

and reduce latency in cases where distributed clocking

is not used.

Design Resources

TIDEP0079 Tools Folder

TMDXIDK5728 Tools Folder

TMDSIDK437x Tools Folder

AM572x Product Folder

ASK Our E2E Experts

Design Features

• EtherCAT Class A or Class B Master Stack

According to ETG.1500 Specification

• High-Performance Ethernet Driver for Maximum

EtherCAT Performance

• EtherCAT Feature: Pack Cable Redundancy Using

Two GMAC Ports or Two ICSS_PRU Ports

• EtherCAT Feature: Pack Hot Connect to Support

Flexible Configuration

• PRU-ICSS EMAC Feature: Time-Triggered Send

• Supported Operating System: TI-RTOS

Featured Applications

• EtherCAT Programmable Logic Controller (PLC)

System

• EtherCAT Motion Control Application

• EtherCAT Interface Boards

• EtherCAT Industrial Communication Gateways

Introduction

www.ti.com

2

TIDUBZ1B–June 2016–Revised October 2016

Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

EtherCAT

®

Master Reference Design for Sitara™ AM57x Gigabit Ethernet

and PRU-ICSS with Time-Triggered Send

An IMPORTANT NOTICE at the end of this TI reference design addresses authorized use, intellectual property matters and other

important disclaimers and information.

1 Introduction

This TI Design document presents the TI Sitara AM572x implementing an EtherCAT Master using acontis

EtherCAT Master stack (EC-Master). The acontis EtherCAT Master stack is a highly portable software

stack, and when combined with a high-performance TI Sitara CPU it provides a sophisticated EtherCAT

solution that users can use to implement EtherCAT communication-interface boards, EtherCAT-based

PLC, or EtherCAT-based motion-control applications.

The EC-Master architectural design does not require additional tasks, making it easier to transport code to

a different OS or to bare-metal systems. Because of this architecture and the high-speed Ethernet driver,

it is possible to implement applications on AM572x platform with cycle times of less than 100 µs.

2 EtherCAT

®

Protocol

EtherCAT is an IEEE 802.3 Ethernet-based fieldbus system. EtherCAT is a new standard in

communication speed. Because EtherCAT is inexpensive to implement, the system can use fieldbus

technology in applications which previously omitted fieldbus. EtherCAT is an open technology that is

standardized within the International Electrotechnical Commission (IEC). The technology is supported and

powered by the EtherCAT Technology Group (an international community of users and vendors). The

protocol is suitable for both hard and soft real-time requirements in automation technology. A primary

advantage of EtherCAT is that it supports automation applications that require short data-update times

with low communication jitter and reduced hardware costs.

In the EtherCAT protocol, the EtherCAT Master sends a telegram that passes through each node. Each

EtherCAT Slave device reads the data that is addressed to it as soon as the data is detected. Then, the

slave device inserts the data into the frame as the frame moves downstream. The frame is delayed by

hardware-propagation delay times. The last node in a segment (or branch) detects an open port and

sends the message back to the master using the full-duplex feature of Ethernet technology. The EtherCAT

Master is the only node within a segment that actively sends an EtherCAT frame. All other nodes forward

the frames downstream. This capability permits the network to achieve over 90% of the available network

bandwidth, prevents unpredictable delays, and guarantees real-time system response.

The EtherCAT protocol is optimized for process data transfer and is transported within the Ethernet frame

by using a special Ethertype identifier (0x88A4). EtherCAT communications consist of several EtherCAT

telegrams. Each telegram serves a specific memory area of the logical process image, up to 4GB. The

data sequence is independent of the physical order of the Ethernet terminals in the network.

In addition to data exchanges between the EtherCAT Master and Slave, EtherCAT is also suitable for

communication between controllers (master to master). Freely addressable network variables for process

data and a variety of services for parameterization, diagnosis, programming, and remote control cover a

range of requirements. The data interfaces for master-to-slave and master-to-master communication are

identical.

Two mechanisms are available for slave-to-slave communication. The first option is to use upstream

devices to quickly communicate to downstream devices within the same cycle. The other option is using

the freely configurable slave-to-slave communication that runs through the master device. The second

option requires two bus cycles (although not necessarily two control cycles).

www.ti.com

Block Diagram

3

TIDUBZ1B–June 2016–Revised October 2016

Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

EtherCAT

®

Master Reference Design for Sitara™ AM57x Gigabit Ethernet

and PRU-ICSS with Time-Triggered Send

3 Block Diagram

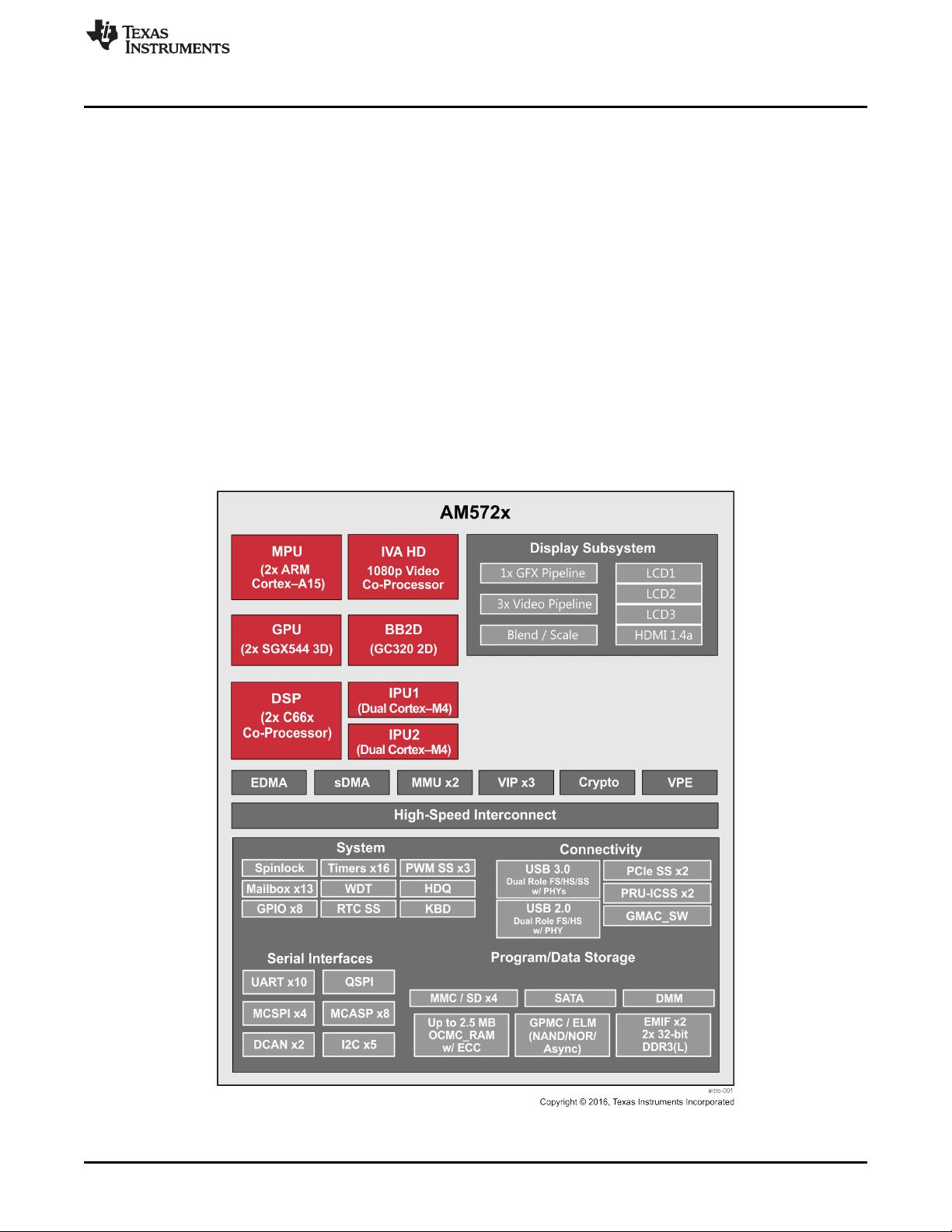

3.1 TI Sitara™ AM572x Overview

The Sitara AM572x brings high processing performance through the maximum flexibility of a mixed

processor solution that is fully integrated. The devices also combine programmable video processing with

a broad and highly integrated peripheral set which is well suitable for industrial applications.

Programmability is provided by dual-core ARM

®

Cortex

®

-A15 RISC CPUs with ARM

®

NEON™ technology,

and two TI C66x VLIW floating-point DSP cores. The ARM Cortex lets developers keep separate control

functions from other algorithms that are programmed on the DSPs and coprocessors. The separated

control functions reduce the complexity of the system software. The ARM Cortex-A15 CPU supports

multiple operating frequencies at a range of up to 1.5GHz. The AM572x processor is configured with two

dual-core Programmable Real-Time Unit and Industrial Communication Subsystems (PRU-ICSS). The

PRU-ICSS can be used for communication protocols such as EtherCAT Master and Slave, PROFINET,

Ethernet/IP, SERCOS, and so forth. This TI design shows two implementations of the acontis EC-Master:

one operates by using Gigabit Ethernet Media Access Controller (GMAC) ports, the other operates by

using Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS) ports and

Ethernet Media Access Controller (EMAC) ports. These options let users to select which type of EMAC to

use when running an EtherCAT Master.

Figure 1 shows the functional block diagram.

Figure 1. AM572x Block Diagram

EtherCAT® master core

XML parser

Process data image Mailbox services

Application

OS layer

(Easy operating

system adaptation)

EC link layer

(Optimized real-time Ethernet

driver with direct HW access)

Response

Request

Standard Ethernet MAC

.XML

Process data (PD) image description

EtherCAT network

information (ENI) file

Acyclic

commands

Cyclic commands

Copyright © 2016, Texas Instruments Incorporated

acontis EtherCAT

®

Master Architecture

www.ti.com

4

TIDUBZ1B–June 2016–Revised October 2016

Submit Documentation Feedback

Copyright © 2016, Texas Instruments Incorporated

EtherCAT

®

Master Reference Design for Sitara™ AM57x Gigabit Ethernet

and PRU-ICSS with Time-Triggered Send

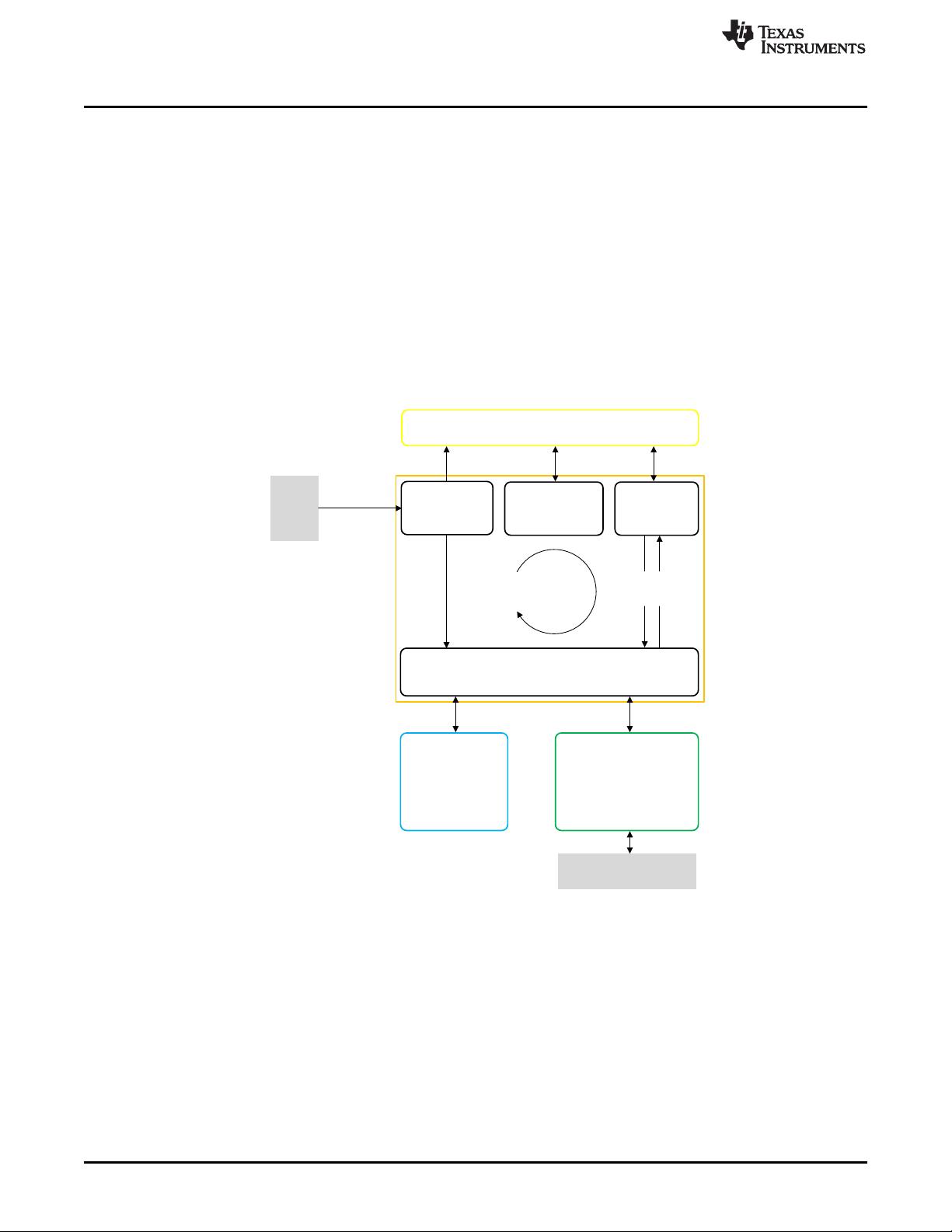

4 acontis EtherCAT

®

Master Architecture

Figure 2 shows the module architecture for the acontis EC-Master. The EC-Master stack is divided into

the following layers:

• EtherCAT Master Core

– In the core module, cyclic (process data update) and acyclic (mailbox) EtherCAT commands are

sent and received.

• Configuration Layer

– The EtherCAT Master is configured using an XML file whose format is fixed in the EtherCAT

specification ETG.2100. The EC-Master contains an OS-independent XML parser.

• Ethernet Link Layer

– This layer exchanges Ethernet frames between the master and the slave devices.

• OS Layer

– All OS-dependent system calls are encapsulated in a small OS layer.

Figure 2. acontis EC-Master Component Model Architecture

剩余18页未读,继续阅读

zyj198

- 粉丝: 1

- 资源: 4

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论10