没有合适的资源?快使用搜索试试~ 我知道了~

首页计算机组成原理课程设计---微程序控制器的设计

一、设计思路 按照要求设计指令系统,该指令系统能够实现数据传送,进行加、减运算和无条件转移,具有累加器寻址、寄存器寻址、寄存器间接寻址、存储器直接寻址、立即数寻址等五种寻址方式。从而可以想到如下指令: (1)24位控制位分别介绍如下: XRD : 外部设备读信号,当给出了外设的地址后,输出此信号,从指定外设读数据。 EMWR: 程序存储器EM写信号。 EMRD: 程序存储器EM读信号。 PCOE: 将程序计数器PC的值送到地址总线ABUS上。 EMEN: 将程序存储器EM与数据总线DBUS接通,由EMWR和EMRD决定是将DBUS数据写到EM中,还是从EM读出数据送到DBUS。 IREN: 将程序存储器EM读出的数据打入指令寄存器IR和微指令计数器uPC。 EINT: 中断返回时清除中断响应和中断请求标志,便于下次中断。 ELP: PC打入允许,与指令寄存器的IR3、IR2位结合,控制程序跳转。 ... ...

资源详情

资源评论

资源推荐

“计算机组成原理”课程设计报告

微程序控制器的设计

一、设计思路

按照要求设计指令系统,该指令系统能够实现数据传送,进行加、减运

算和无条件转移,具有累加器寻址、寄存器寻址、寄存器间接寻址、存储器

直接寻址、立即数寻址等五种寻址方式。从而可以想到如下指令:

(1)24 位控制位分别介绍如下:

XRD : 外部设备读信号,当给出了外设的地址后,输出此信号,从指定

外设读数据。

EMWR: 程序存储器 EM 写信号。

EMRD: 程序存储器 EM 读信号。

PCOE: 将程序计数器 PC 的值送到地址总线 ABUS 上。

EMEN: 将程序存储器 EM 与数据总线 DBUS 接通,由 EMWR 和 EMRD

决 定 是 将 DBUS 数 据 写 到 EM 中 , 还 是 从 EM 读 出 数 据 送 到

DBUS。

IREN: 将程序存储器 EM 读出的数据打入指令寄存器 IR 和微指令计数器

uPC。

EINT: 中断返回时清除中断响应和中断请求标志,便于下次中断。

ELP: PC 打入允许,与指令寄存器的 IR3、IR2 位结合,控制程序跳转。

MAREN:将数据总线 DBUS 上数据打入地址寄存器 MAR。

MAROE:将地址寄存器 MAR 的值送到地址总线 ABUS 上。

OUTEN:将数据总线 DBUS 上数据送到输出端口寄存器 OUT 里。

STEN: 将数据总线 DBUS 上数据存入堆栈寄存器 ST 中。

RRD: 读寄存器组 R0-R3,寄存器 R?的选择由指令的最低两位决定。

RWR: 写寄存器组 R0-R3,寄存器 R?的选择由指令的最低两位决定。

CN: 决定运算器是否带进位移位,CN=1 带进位,CN=0 不带进位。

FEN: 将标志位存入 ALU 内部的标志寄存器。

X2: X2、X1、X0 三位组合来译码选择将数据送到 DBUS 上的寄存器。

X1: 见 16 页表。

X0:

WEN: 将数据总线 DBUS 的值打入工作寄存器 W 中。

AEN: 将数据总线 DBUS 的值打入累加器 A 中。

S2: S2、S1、S0 三位组合决定 ALU 做何种运算。

本实验还需用到的五条机器指令:IN(输入)、ADD(二进制加法)、STA

(存数)、OUT(输出)、JMP(无条件转移),其指令格式如下:

助记符 机器指令码 说明

IN 0000 0000 “INPUT DEVICE”中的开关状态R0

ADD addr 0001 0000 ×××× R0+[addr] R0

STA addr 0010 0000 ×××× R0 [addr]

OUT addr 0011 0000 ×××× [addr] BUS

JMP addr 0100 0000 ×××× addrPC

其中 IN 为单字长(8 位),其余为双字长指令,××××××××为 addr

对应的二进制地址码。

为了向 RAM 写入、读出机器指令,并能启动程序执行,还须设计三个控

制台操作微程序。

存储器读(KRD):拨动总清开关 CLR 后,控制台开关 SWB、SWA 为

“0 0”时,按 START 微动开关,可对 RAM 连续手动读操作。

存储器写(KWE):拨动总清开关 CLR 后,控制台开关 SWB、SWA 为

“0 1”时,按 START 微动开关,可对 RAM 连续手动写操作。

启动程序(RP):拨动总清开关 CLR 后,控制台开关 SWB、SWA 为“1

1”时,按 START 微动开关,即可转入到第 01 号“取址”微指令,启动程序运行。

上述三条控制台指令用两个开关 SWB、SWA 的状态来设置,其定义如下:

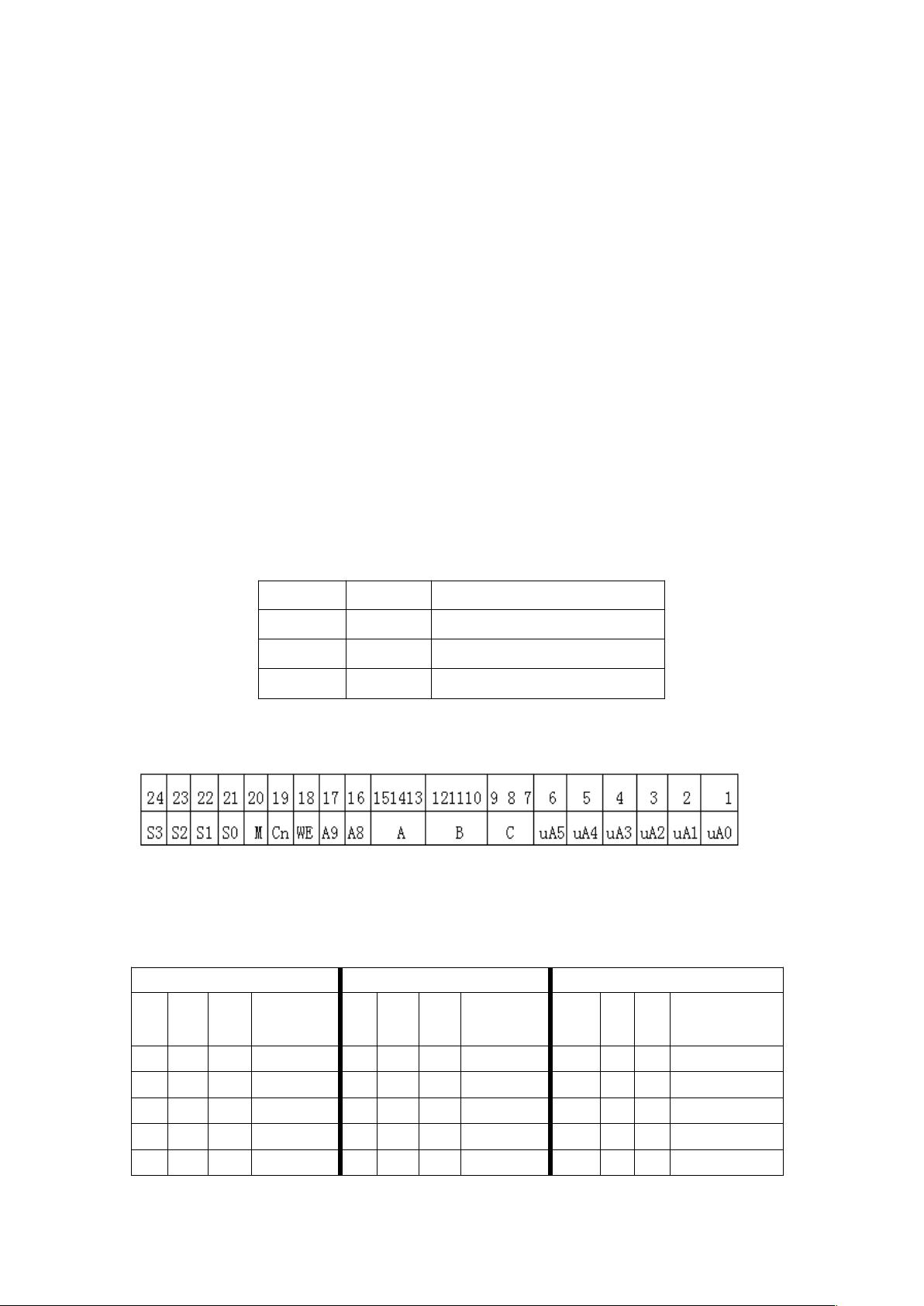

(二)在实验中使用的模型机的微指令格式如下表给定,长度共 24 位。

其中最后六位 uA0~uA5 为 6 位的下一条微指令的地址, 前面几位为直接

控制字段,直接与相应的控制门连接,A,B,C 为 3 个译码字段,分别由三个控制

位译码出多位。其含义如下:

A 字段 B 字段 C 字段

15 14 13

选择

12 11 10

选择

9 8 7

选择

0 0 0 0 0 0 0 0 0

0 0 1 LDRi 0 0 1 RS-B 0 0 1 P(1)

0 1 0 LDDR1 0 1 0 0 1 0

0 1 1 LDDR2 0 1 1 0 1 1

1 0 0 LDIR 1 0 0 1 0 0 P(4)

SWB SWA

控制台指令

0 0

读内存(KRD)

0 1

写内存(KWE)

1 1

启动程序(RP)

1 0 1 LOAD 1 0 1 ALU-B 1 0 1

1 1 0 LDAR 1 1 0 PC-B 1 1 0 LDPC

控制位含义

微程序控制器的结构与微指令的格式密切相关。

微程序控制器由控制存储器、微地址寄存器、微命令寄存器和地址转移逻

辑几部分组成。微地址寄存器和微命令寄存器两者的总长度即为一条微指令

的长度,二者合在一起称为微指令寄存器。

●控制存储器(ROM)

ROM 中存放微程序,也就是全部的微指令。 ROM 的容量取决于微指令

的 总 数 。 假 如 控 制 器 需 要 128 条 微 指 令 , 则 微 地 址 寄 存 器 长 度 为 7 位。

ROM 的字长取决于微指令长度。如果微指令为 32 位,则 ROM 的字长就是

32 位。实际应用中 ROM 可采用 EPROM 或 E2PROM、EAROM,用户写

入和修改微程序比较方便。

●微命令寄存器

微命令寄存器暂存由控制存储器中读出的当前微指令中控制字段与测试判

别字段信息,可由 8D 寄存器组成。

●微地址寄存器

微地址寄存器暂存由控制存储器读出的当前微指令的下址字段信息。它可

由带 RD、SD 强置端的 D 触发器组成。其中时钟端和 D 端配合用做 ROM 的

读出打入,用 SD 进行下址修改。

●地址转移逻辑

微指令由 ROM 读出后直接给出下一条微指令的地址,这个地址就放在微

地址寄存器中。当微程序出现分支时通过地址转移逻辑去修改微地址寄存器

内容,并按修改好的微地址读出下条微指令。地址转移逻辑是一个组合逻辑

电路,其输入是当前微指令的判别测试字段 Pi、执行部件反馈的“状态条件”

及时间因素 T4。

●控制时序信号

上图中标明了一个基本机器周期中的控制时序信号。例如用上一周期的

T4 时间按微地址寄存器内容从 ROM 中读一条微指令,经过一段时间后被读

出,用当前周期的 T1 时间打入到微指令寄存器。T2、T3 时间用来控制执行

部件进行操作。T4 时间修改微地址寄存器内容并读出下一条微指令。

二、设计步骤:

(一)、拟订指令系统

指令系统是设计计算机的依据 ,拟订指令系统将涉及基本字长、指令格式、

指令种类、寻址方式等内容。

基本字长:

程序设计平台中配置的存储器容量为256*8,可知道基本字长定为8位。

指令格式:

指令格式可有单字长和双字长指令两种,在双字长格式中,第二字节一般

定义为操作数或操作数地址。

指令格式为:

操作码OP 源操作数 目的操作数

指令类型:

模型机有单操作数指令、双操作数指令和无操作数指令。

操作码OP共四位,最多可定义16条指令。

数据的传送单位为 8 位

数据的传送范围 R—>R R—>RAM RAM—>R

寻址方式:

由于指令较短,操作数字段仅两位,为了简化硬件设计,将操作数字段和

目的操作数字段的寻址定义为不同的含义。

源操作数字段寻址方式 目的操作数寻址方式

00 R0 00 R1

01 (R0) 01 (R1)

10 I 10 I

11 D 11 D

Ri 表示操作数就在寄存器中

(Ri)表示操作数地址在寄存器中

I 指令的第二个字节为操作数或称立即寻址

(D)指令的第二个字节为操作数的地址

源操作数使用 R0 寻址

目的操作数 R1 寻址

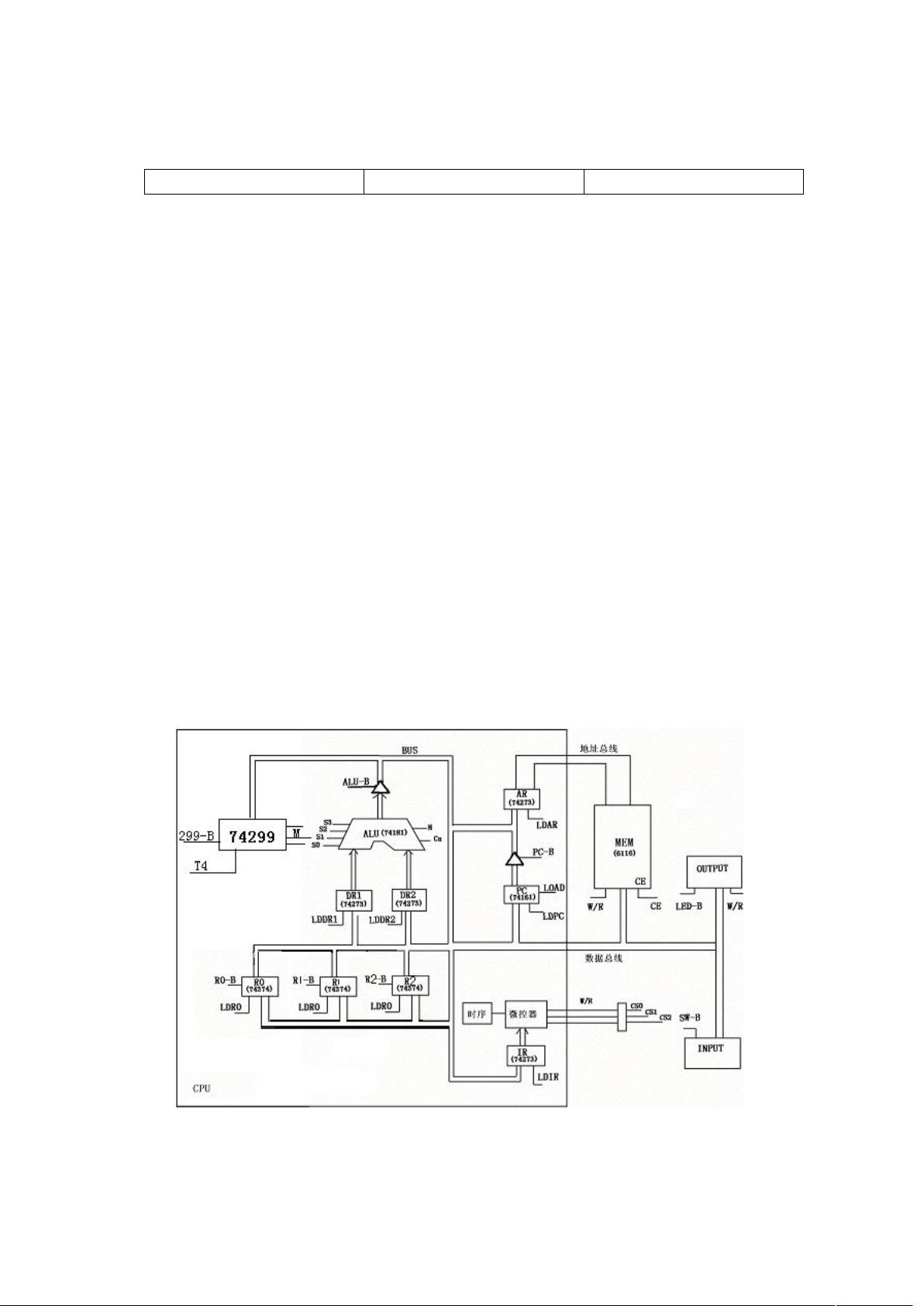

(二)、确定总体结构

根据要求设计数据通路框图:

图 2-1 数据通路结构框图

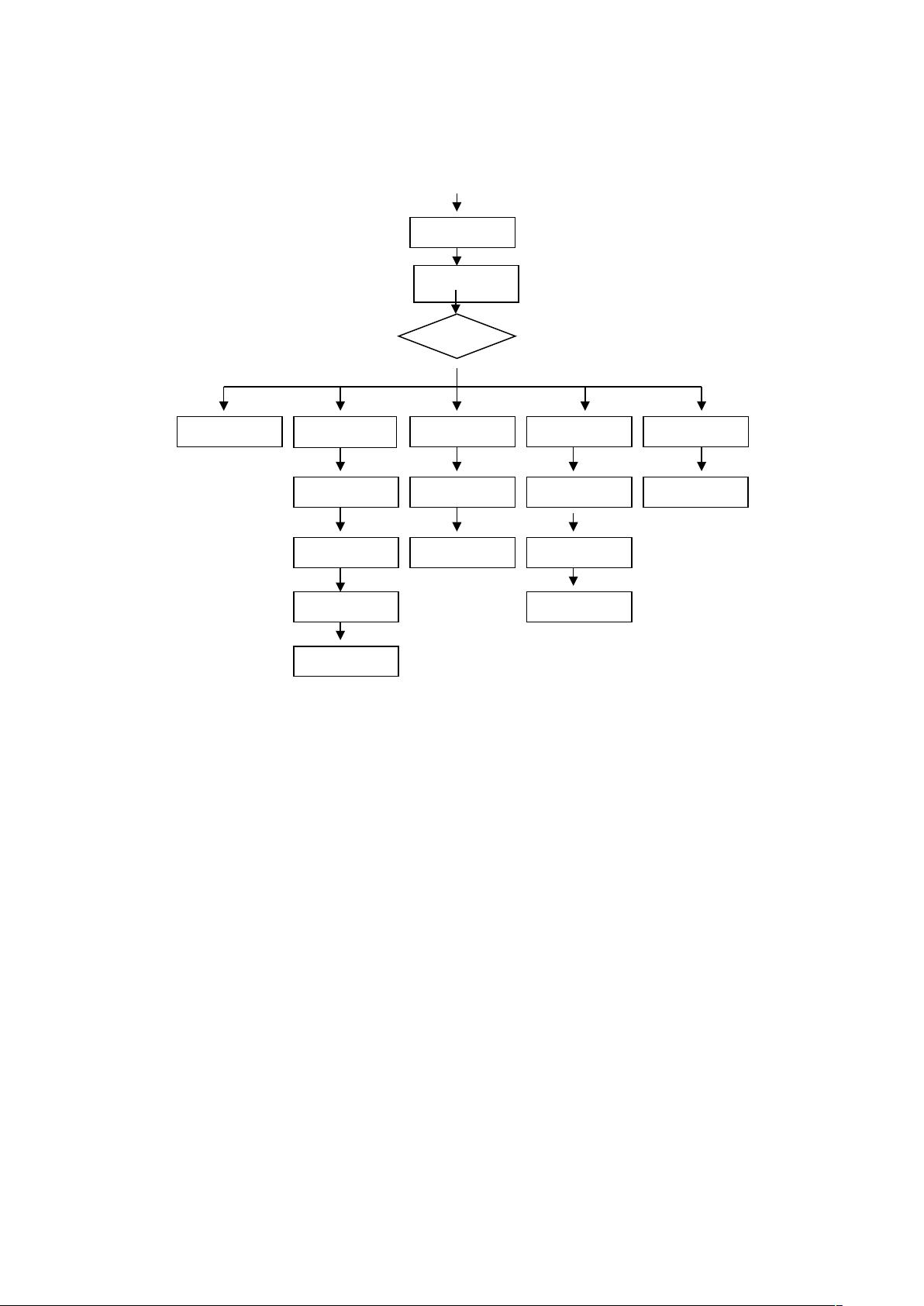

2.1 流程图

图 2-2 微程序流程图

当拟定“取指”微指令时,该微指令的判别测试字段为 P(1)测试。由于“取

指”微指令是所有微指令都使用的公用微指令,因此 P(1)的测试结果会出现

多路分支。我们使用指令寄存器的前 4 位(IR7-IR4)作为测试条件,出现 5

路分支,占用 5 个固定微地址单元。

控制台命令的微程序流程,01 为取指令微指令的地址:

PC->AR, PC+1

RAM->BUS, BUS-

>LR

P(1

)

RW->R0

(DR1)+(DR2) ->R0

R0->DR1

RAM->BUS, BUS-

>DRE

RAM->BUS, BUS-

>AR

PC->AR,

PC+1

RAM->BUS, BUS-

>LR

RAM->BUS, BUS-

>AR

PC->AR, PC+1

DR1->LED

RAM->BUS, BUS-

>AR

RAM->BUS, BUS-

>DR1

PC->AR, PC+1

RAM->BUS, BUS-

>PC

PC->AR, PC+1

IN ADD STA OUT JMP

剩余21页未读,继续阅读

pgy6x

- 粉丝: 1

- 资源: 14

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论6