没有合适的资源?快使用搜索试试~ 我知道了~

首页PCIe_CEM_SPEC_R4_V0.9_11152018_NCB.pdf

资源详情

资源评论

资源推荐

PCI Express 1

Card Electromechanical 2

Specification 3

Revision 4.0, Version 0.9 4

November 15, 2018 5

6

7

8

9

PCI Express

Card Electromechanical Specification

Revision 4.0, Version 0.9 2

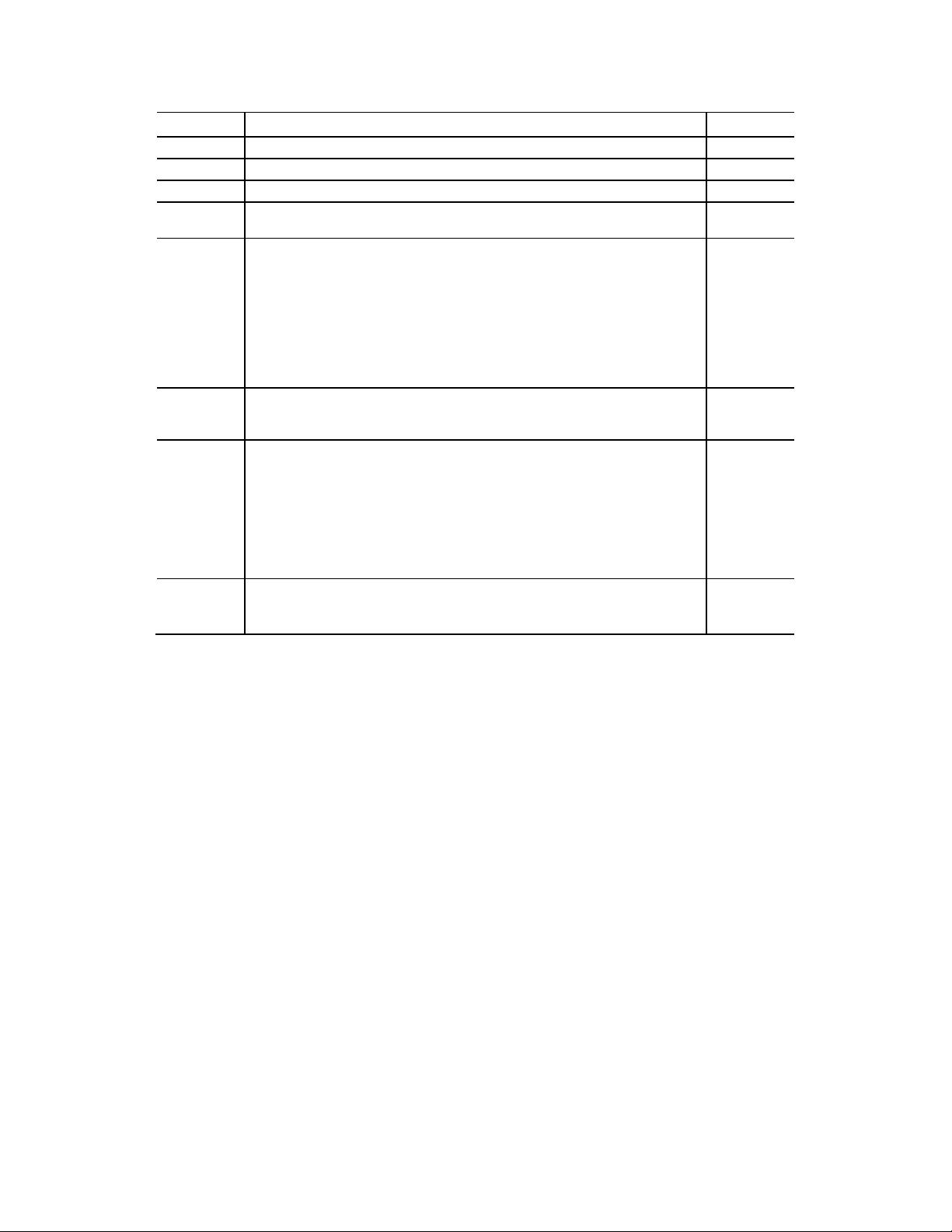

Revision

Revision History

Date

1.0 Initial release. 7/22/2002

1.0a Incorporated WG Errata C1-C7 and E1. 4/15/2003

1.1 Incorporated approved Errata and ECNs. 3/28/2005

2.0 Added support for 5.0 GT/s data rate. 4/11/2007

3.0

• Added support for 8.0 GT/s data rate and incorporated approved Errata and

ECNs. Incorporated the PCI Express x16 Graphics 150W-ATX Specification

and the PCI Express 225 W/300 W High Power Card Electromechanical

Specification.

• Re-imported all figures

• Updated Figure 6-1 and Figure 6-3

• Fixed text notes in Chapter 6 and 9 Figures (took notes out of Illustrator and

made them part of the Word file)

• Changed 306.67 MAX dimension to 326.03 MIN in Figure 9-3

7/21/2013

4.0

• Added support for 16.0 GT/s data rate and incorporated approved Errata and

ECNs.

• Significant PCB layout updates to support signal integrity

10/11/2013

4.0 r 0.7

Incorporated the following

• CEM Comment tracking for 0.7 rev of 4.0 sent 2018 Feb 14, comments

updated 03 March:

• 10.12.2017 - Cisco Comments on v0.7 r4.0 CEM, 10.02.2017 draft

• PCIe3 0_CEM_Embedding_Issue_Comm_Rev1_0

• Incorporated new drawings

• CEM Comment tracking for 0.7 rev of 4.0 sent 2018 Feb 14, comments

updated 03 March Wig

03/22/2018

4.0, 0.9

• Updated drawings for clarity

• Miscellaneous text changes

• Incorporated AMD comments

11.152018

10

11

12

PCI Express

Card Electromechanical Specification

Revision 4.0, Version 0.9 3

Contents 13

NOVEMBER 15, 2018 ................................................................................................................ 1

1. INTRODUCTION ................................................................................................................. 12

1.1. Terms and Definitions ................................................................................................. 13

1.2. Reference Documents ................................................................................................ 14

1.3. Specification Contents ................................................................................................ 15

1.4. Objectives .................................................................................................................. 15

1.5. Electrical Overview ..................................................................................................... 16

1.6. Mechanical Overview ................................................................................................. 17

1.7. 150 W Overview ......................................................................................................... 18

1.8. 225 W and 300 W Add-in Card Overview ................................................................... 19

2. AUXILIARY SIGNALS ........................................................................................................ 21

2.1. Reference Clock ......................................................................................................... 22

2.1.1. Low Voltage Swing, Differential Clocks ........................................................................... 22

2.1.2. Spread Spectrum Clocking (SSC) ................................................................................... 23

2.1.3. REFCLK AC Specifications ............................................................................................. 24

2.1.4. REFCLK Phase Jitter Specification for 2.5 GT/s, 5.0 GT/s, 8.0 GT/s and 16.0GT/s

Signaling Support ............................................................................................................ 24

2.2. PERST# Signal .......................................................................................................... 25

2.2.1. Initial Power Up (G3 to S0) .............................................................................................. 25

2.2.2. Power Management States (S0 to S3/S4 to S0) ............................................................. 26

2.2.3. Power Down 27

2.3. WAKE# Signal ............................................................................................................ 28

2.4. SMBus (Optional) ....................................................................................................... 32

2.4.1. Capacitive Load of High-power SMBus Lines ................................................................. 32

2.4.2. Minimum Current Sinking Requirements for SMBus Devices ......................................... 32

2.4.3. SMBus “Back Powering” Considerations ........................................................................ 32

2.4.4. Power-on Reset ............................................................................................................... 33

2.5. JTAG Pins (Optional) .................................................................................................. 33

2.6. PWRBRK# Signal (Optional) ...................................................................................... 34

2.7. Auxiliary Signal Parametric Specifications .................................................................. 35

2.7.1. DC Specifications ............................................................................................................ 35

2.7.2. AC Specifications ............................................................................................................ 36

3. HOT INSERTION AND HOT REMOVAL ............................................................................ 38

3.1. Scope ......................................................................................................................... 38

3.2. Presence Detect ......................................................................................................... 38

4. ELECTRICAL REQUIREMENTS ........................................................................................ 40

4.1. Power Supply Requirements ...................................................................................... 40

4.2. Power Consumption ................................................................................................... 42

4.3. Power Budgeting Capability ........................................................................................ 43

4.4. Power Supply Sequencing .......................................................................................... 43

4.5. Power Supply Decoupling........................................................................................... 44

4.6. Electrical Topologies and Link Definitions ................................................................... 44

4.6.1. Topologies 44

4.6.2. Link Definition 47

4.7. Electrical Budgets ....................................................................................................... 48

4.7.1. AC Coupling Capacitors .................................................................................................. 48

PCI Express

Card Electromechanical Specification

Revision 4.0, Version 0.9 4

4.7.2.

Insertion Loss Values (Voltage Transfer Function) ......................................................... 48

4.7.3. Jitter Values 48

4.7.4. Crosstalk 51

4.7.5. Lane-to-Lane Skew ......................................................................................................... 51

4.7.6. Transmitter Equalization .................................................................................................. 52

4.7.7. Skew within the Differential Pair ...................................................................................... 52

4.7.8. Differential Data Trace Impedance.................................................................................. 52

4.7.9. Differential Data Trace Propagation Delay ...................................................................... 53

4.7.10. Add-in Card Insertion Loss Limit for 16.0 GT/s ............................................................... 53

4.8. Eye Diagrams at the Add-in Card Interface ................................................................ 53

4.8.1. Add-in Card Transmitter Path Compliance Eye Diagram at 2.5 GT/s ............................. 54

4.8.2. Add-in Card Transmitter Path Compliance Eye Diagrams at 5.0 GT/s ........................... 55

4.8.3. Add-in Card Transmitter Path Compliance Eye Diagrams at 8.0 GT/s ........................... 57

4.8.4. Add-in Card Transmitter Path Compliance Eye Diagrams at 16.0 GT/s ......................... 57

4.8.5. Add-in Card Transmitter Path Pulse Width Jitter at 16.0 GT/s ....................................... 58

4.8.6. Add-in Card Minimum Receiver Path Sensitivity Requirements at 2.5 GT/s .................. 59

4.8.7. Add-in Card Minimum Receiver Path Sensitivity Requirements at 5.0 GT/s .................. 60

4.8.8. Add-in Card Minimum Receiver Path Sensitivity Requirements at 8.0 GT/s .................. 61

4.8.9. Add-in Card Minimum Receiver Path Sensitivity Requirements at 16.0 GT/s ................ 62

4.8.10. System Board Transmitter Path Compliance Eye Diagram at 2.5 GT/s ......................... 64

4.8.11. System Board Transmitter Path Compliance Eye Diagram at 5.0 GT/s ......................... 65

4.8.12. System Board Transmitter Path Compliance Eye Diagram at 8.0 GT/s ......................... 68

4.8.13. System Board Transmitter Path Compliance Eye Diagram at 16.0 GT/s ....................... 71

4.8.14. System Board Minimum Receiver Path Sensitivity Requirements at 2.5 GT/s ............... 73

4.8.15. System Board Minimum Receiver Path Sensitivity Requirements at 5.0 GT/s ............... 74

4.8.16. System Board Minimum Receiver Path Sensitivity Requirements at 8.0 GT/s ............... 76

4.8.17. System Board Minimum Receiver Path Sensitivity Requirements at 16.0 GT/s ............. 77

5. 150 W, 225 W, AND 300 W ADD-IN CARD POWER .......................................................... 78

5.1. 150 W Add-in Card Power-Up Sequencing ................................................................. 80

5.2. 225 W and 300 W Add-in Card Power-Up Sequencing ............................................... 82

6. CARD CONNECTOR SPECIFICATION .............................................................................. 86

6.1. Connector Pinout ........................................................................................................ 86

6.2. Connector Interface Definitions .................................................................................. 89

6.3. Signal Integrity Requirements and Test Procedures ................................................... 95

6.3.1. Signal Integrity Requirements ......................................................................................... 95

6.3.2. Signal Integrity Requirements and Test Procedures for 2.5 GT/s Support ..................... 95

6.3.3. Signal Integrity Requirements and Test Procedures for 5.0 GT/s Support ..................... 98

6.3.3.1 Test Fixture Requirements .................................................................... 100

6.3.4. Signal Integrity Requirements and Test Procedures for 8.0 GT/s Support ................... 100

6.3.4.1 Test Fixture Requirements .................................................................... 102

6.3.5. Signal Integrity Requirements and Test Procedures for 16.0 GT/s Support ................. 102

6.3.5.1 Test Fixture Requirements .................................................................... 106

6.4. Connector Environmental and Other Requirements.................................................. 109

6.4.1. Environmental Requirements ........................................................................................ 109

6.4.2. Mechanical Requirements ............................................................................................. 111

6.4.3. Current Rating Requirement ......................................................................................... 111

6.4.4. Additional Considerations .............................................................................................. 112

7. PCI EXPRESS 2 X 3 AUXILIARY POWER CONNECTOR DEFINITION .......................... 113

7.1. 6-Position Power Connector System Performance Requirements ............................ 113

7.2. 6-Position PCB Header ............................................................................................ 113

7.2.1. 6-Position R/A Thru-Hole PCB Header Assembly ........................................................ 113

7.2.2. 6-Position R/A Thru-Hole Header Recommended PCB Footprint ................................ 115

PCI Express

Card Electromechanical Specification

Revision 4.0, Version 0.9 5

7.2.3.

6-Position R/A SMT PCB Header Assembly ................................................................. 116

7.2.4. 6-Position R/A SMT Header Recommended PCB Footprint ......................................... 117

7.3. 6-Position Cable Assembly ....................................................................................... 118

7.4. Connector Mating-Unmating Keepout Area (Latch Lock Release) ............................ 119

7.5. 6-Position Power Connector System Pin Assignment ............................................... 120

7.6. Additional Considerations ......................................................................................... 121

8. PCI EXPRESS 2 X 4 AUXILIARY POWER CONNECTOR DEFINITION .......................... 122

8.1. 2 x 4 Auxiliary Power Connector Performance Requirements ................................... 124

8.2. 2 x 4 Receptacle ....................................................................................................... 124

8.2.1. Connector Drawing ........................................................................................................ 124

8.2.2. PCB Footprint 126

8.3. Cable Assembly ....................................................................................................... 127

8.4. Connector Mating-Unmating Keepout Area (Latch Lock Release) ............................ 129

8.5. 2 x 4 Auxiliary Power Connector System Pin Assignment ........................................ 130

8.6. Additional Considerations ......................................................................................... 132

9. ADD-IN CARD FORM FACTORS AND IMPLEMENTATION ........................................... 133

9.1. Add-in Card Form Factors ........................................................................................ 133

9.2. Add-in Card Layout Requirements and Recommendations for 16.0 GT/s Operation 149

9.2.1. Voiding and Planes Under Edge-fingers ....................................................................... 149

9.2.2. No Add-in Card Depopulated or Floating Edge-fingers................................................. 150

9.2.3. Edge-finger Length and Outer Layer Keepout .............................................................. 150

9.2.4. Add-in Card Adjacent Edge-finger Ground Vias ........................................................... 151

9.2.5. Joined Edge-finger Ground Vias ................................................................................... 151

9.2.6. Auxiliary Signal Conductor AC Match Termination ....................................................... 152

9.3. System Board Requirements for 16.0 GT/s Operation .............................................. 154

9.3.1. Sentry Ground Vias Adjacent to Auxiliary Signal Vias .................................................. 154

9.4. Connector and Add-in Card Locations ...................................................................... 156

9.5. Card Interoperability ................................................................................................. 165

9.6. 10 W/25 W/75 W/150 W Thermal Characterization................................................... 165

9.7. 150 W Thermal Management ................................................................................... 166

10. PCI EXPRESS 225 W/300 W ADD-IN CARD THERMAL AND ACOUSTIC MANAGEMENT

.......................................................................................................................................... 167

10.1. Inlet Temperature ..................................................................................................... 167

10.2. Card Thermal Characterization Procedure ............................................................... 168

10.3. Acoustic Management .............................................................................................. 172

10.3.1. Background and Scope ................................................................................................. 172

10.3.2. Card Acoustic Characterization Procedure ................................................................... 172

10.3.3. Acoustic Recommendations and Guidelines ................................................................. 173

11. ADAPTER ADD-IN CARD THERMAL REPORTING ........................................................ 174

11.1. Airflow Impedance (AFI) Level ............................................................................... 174

11.2. Maximum Thermal (MaxTherm) Level ................................................................... 176

11.3. Degraded Thermal (DTherm) Level ....................................................................... 178

11.4. MaxAmbient ............................................................................................................ 179

INSERTION LOSS VALUES (VOLTAGE TRANSFER FUNCTION) (INFORMATIONAL ONLY)

.......................................................................................................................................... 180

TEST CHANNEL SCATTERING PARAMETERS ................................................................... 183

8.0 GT/s Test Channels .................................................................................................... 183

剩余192页未读,继续阅读

weixin_48783600

- 粉丝: 0

- 资源: 7

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0