没有合适的资源?快使用搜索试试~ 我知道了~

首页JTAG调试原理(OPEN-JTAG开发小组)

JTAG调试原理(OPEN-JTAG开发小组)

需积分: 46 49 下载量 52 浏览量

更新于2023-03-03

评论 3

收藏 571KB PDF 举报

主要介绍ARM JTAG调试的基本原理。基本的内容包括了TAP (TEST ACCESS PORT) 和BOUNDARY-SCAN ARCHITECTURE的介绍,在此基础上,结合ARM7TDMI详细介绍了的JTAG调试原理。

资源详情

资源评论

资源推荐

OPEN-JTAG

ARM JTAG 调试原理

OPEN-JTAG 开发小组

1 前言

这篇文章主要介绍 ARM JTAG 调试的基本原理。基本的内容包括了 TAP (TEST ACCESS

PORT) 和 BOUNDARY-SCAN ARCHITECTURE 的介绍,在此基础上,结合 ARM7TDMI 详细

介绍了的 JTAG 调试原理。

这篇文章主要是总结了前段时间的一些心得体会,希望对想了解 ARM JTAG 调试的网友们

有所帮助。我个人对 ARM JTAG 的理解还不是很透彻,在文章中,难免会有偏失和不准确的地

方,希望精通 JTAG 调试原理的大侠们不要拍砖,有什么问题提出来,我一定尽力纠正。同时

也欢迎对 ARM JTAG 调试感兴趣的朋友们一起交流学习。

2 IEEE Standard 1149.1 - Test Access Port and Boundary-Scan Architecture

既然是介绍 JTAG 调试,还是让我们从 IEEE 的 JTAG 调试标准开始吧。JTAG 是 JOINT

TEST ACTION GROUP 的简称。IEEE 1149.1 标准就是由 JTAG 这个组织最初提出的,最终由

IEEE 批准并且标准化的。所以,这个 IEEE 1149.1 这个标准一般也俗称 JTAG 调试标准。

接下来的这一部分,主要简单的介绍了 TAP (TEST ACCESS PORT) 和

BOUNDARY-SCAN ARCHITECTURE 的基本构架。虽然不是很全面,但对了解 JTAG 的基本

原理来说,应该是差不离了。如果希望更全面深入的了解 JTAG 的工作原理,可以参考 IEEE

1149.1 标准。

2-1 边界扫描

在 JTAG 调试当中,边界扫描(Boundary-Scan)是一个很重要的概念。边界扫描技术的

基本思想是在靠近芯片的输入输出管脚上增加一个移位寄存器单元。因为这些移位寄存器单

元都分布在芯片的边界上(周围),所以被称为边界扫描寄存器(Boundary-Scan Register Cell)。

当芯片处于调试状态的时候,这些边界扫描寄存器可以将芯片和外围的输入输出隔离开来。

通过这些边界扫描寄存器单元,可以实现对芯片输入输出信号的观察和控制。对于芯片的输

入管脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载倒该管脚中去;对于

芯片的输出管脚,也可以通过与之相连的边界扫描寄存器“捕获”(CAPTURE)该管脚上的

输出信号。在正常的运行状态下,这些边界扫描寄存器对芯片来说是透明的,所以正常的运

行不会受到任何影响。这样,边界扫描寄存器提供了一个便捷的方式用以观测和控制所需要

调试的芯片。另外,芯片输入输出管脚上的边界扫描(移位)寄存器单元可以相互连接起来,

在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。一般的芯片都会提供几条独立的

边界扫描链,用来实现完整的测试功能。边界扫描链可以串行的输入和输出,通过相应的时

钟信号和控制信号,就可以方便的观察和控制处在调试状态下的芯片。

利用边界扫描链可以实现对芯片的输入输出进行观察和控制。下一个问题是:如何来管

理和使用这些边界扫描链?对边界扫描链的控制主要是通过 TAP (Test Access Port)Controller

来完成的。在下一个小节,我们一起来看看 TAP 是如何工作的。

2-2 TAP (TEST ACCESS PORT)

在上一节,我们已经简单介绍了边界扫描链,而且也了解了一般的芯片都会提供几条边

界扫描链,用来实现完整的测试功能。下面,我将逐步介绍如何实现扫描链的控制和访问。

TWENTYONE XUZHOUHE@HOTMAIL.COM & DUYUNHAI DUYUNHAI@HOTMAIL.COM

1

OPEN-JTAG

在 IEEE 1149.1 标准里面,寄存器被分为两大类:数据寄存器(DR-Data Register)和指令

寄存器(IR-Instruction Register)。边界扫描链属于数据寄存器中很重要的一种。边界扫描链用

来实现对芯片的输入输出的观察和控制。而指令寄存器用来实现对数据寄存器的控制,例如:

在芯片提供的所有边界扫描链中,选择一条指定的边界扫描链作为当前的目标扫描链,并作

为访问对象。下面,让我们从 TAP(Test Access Port)开始。

TAP 是一个通用的端口,通过 TAP 可以访问芯片提供的所有数据寄存器(DR)和指令

寄存器(IR)。对整个 TAP 的控制是通过 TAP Controller 来完成的。TAP 总共包括 5 个信号接

口 TCK、TMS、TDI、TDO 和 TRST :其 中 4 个是输入信号接口和另外 1 个是输出信号接口。

一般,我们见到的开发板上都有一个 JTAG 接口,该 JTAG 接口的主要信号接口就是这 5 个。

下面,我先分别介绍这个 5 个接口信号及其作用。

Test Clock Input (TCK)

TCK 为 TAP 的操作提供了一个独立的、基本的时钟信号,TAP 的所有操作都是通过

这个时钟信号来驱动的。TCK 在 IEEE 1149.1 标准里是强制要求的。

Test Mode Selection Input (TMS)

TMS 信号用来控制 TAP 状态机的转换。通过 TMS 信号,可以控制 TAP 在不同的状

态间相互转换。TMS 信号在 TCK 的上升沿有效。TMS 在 IEEE 1149.1 标准里是强制

要求的。

Test Data Input (TDI)

TDI 是数据输入的接口。所有要输入到特定寄存器的数据都是通过 TDI

接口一位一位

串行输入的(由 TCK 驱动)。TDI 在 IEEE 1149.1 标准里是强制要求的。

Test Data Output (TDO)

TDO 是数据输出的接口。所有要从特定的寄存器中输出的数据都是通过 TDO 接口一

位一位串行输出的(由 TCK 驱动)。TDO 在 IEEE 1149.1 标准里是强制要求的。

Test Reset Input (TRST)

TRST可以用来对 TAP Controller 进行复位(初始化)。不过这个信号接口在 IEEE 1149.1

标准里是可选的,并不是强制要求的。因为通过 TMS 也可以对 TAP Controller 进行复

位(初始化)。

事实上,通过 TAP 接口,对数据寄存器(DR)进行访问的一般过程是:

通过指令寄存器(IR),选定一个需要访问的数据寄存器;

把选定的数据寄存器连接到 TDI 和 TDO 之间;

由 TCK 驱动,通过 TDI,把需要的数据输入到选定的数据寄存器当中去;同时把选

定的数据寄存器中的数据通过 TDO 读出来。

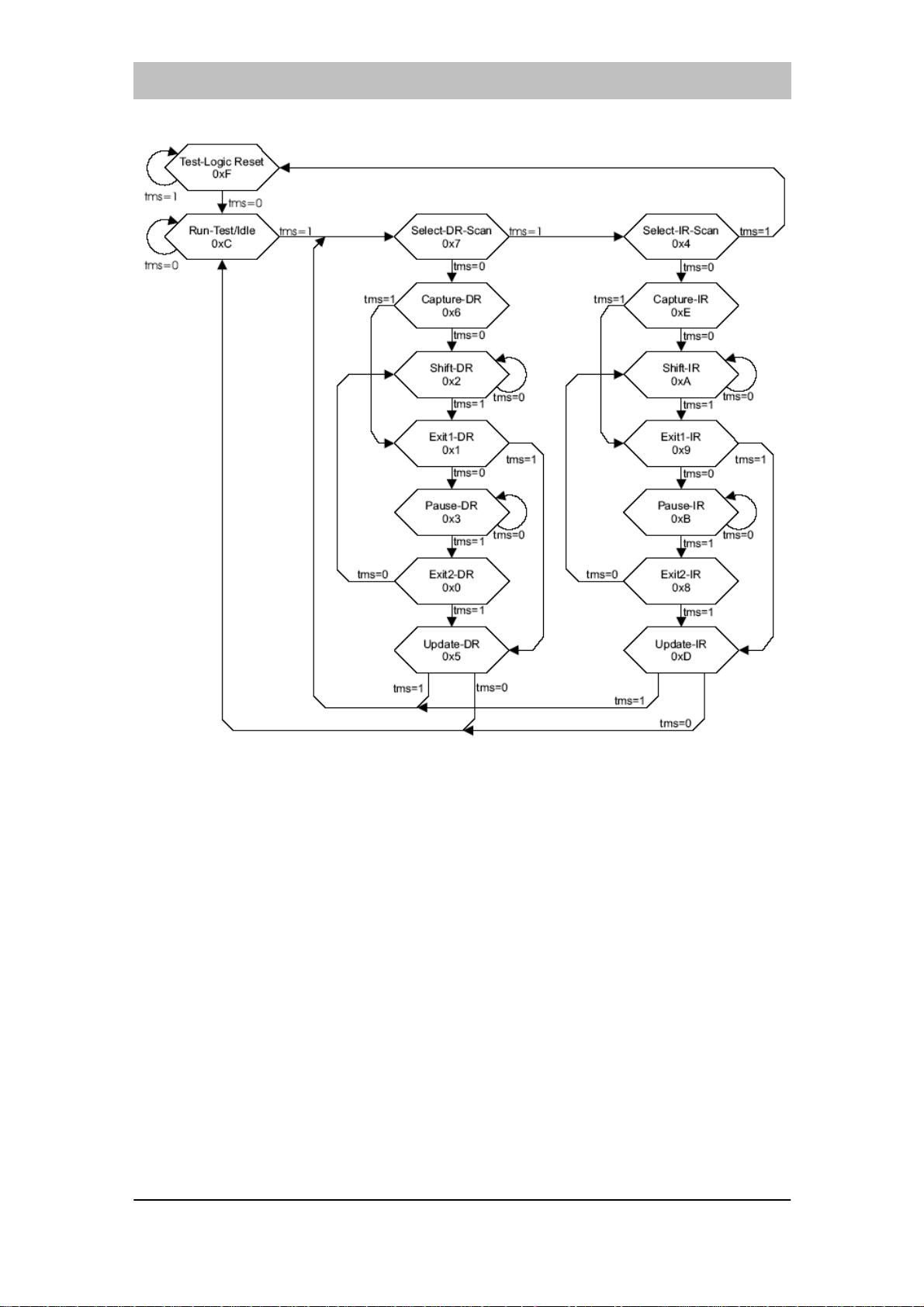

接下来,让我们一起来了解一下 TAP 的状态机。TAP 的状态机如图 1 所示,总共有 16 个

状态。在图中,每个六边形表示一个状态,六边形中标有该状态的名称和标识代码。图中的

箭头表示了 TAP Controller 内部所有可能的状态转换流程。状态的转换是由 TMS 控制的,所

以在每个箭头上有标有 tms = 0 或者 tms = 1。在 TCK 的驱动下,从当前状态到下一个状态

的转换是由 TMS 信号决定。假设 TAP Controller 的当前状态为 Select-DR-Scan,在

TCK 的驱

动下,如果 TMS = 0,TAP Controller 进入 Capture-DR 状态;如果 TMS = 1,TAP Controller

进入 Select-IR-Scan 状态。

TWENTYONE XUZHOUHE@HOTMAIL.COM & DUYUNHAI DUYUNHAI@HOTMAIL.COM

2

OPEN-JTAG

图 1. TAP Controller State Transitions

这个状态机看似很复杂,其实理解以后会发现这个状态机其实很直接、很简单。观察图

1,我们可以发现,除了 Test-Logic Reset 和 Test-Run/Idle 状态外,其他的状态有些类似。例

如 Select-DR-Scan 和 Select-IR-Scan 对应,Capture-DR 和 Capture-IR 对应,Shift-DR 和 Shift-IR

对应,等等。在这些对应的状态中,DR 表示 Data Register,IR 表示 Instruction Register。记

得我们前面说过吗,寄存器分为两大类,数据寄存器和指令寄存器。其实标识有 DR 的这些

状态是用来访问数据寄存器的,而标识有 IR 的这些状态是用来访问指令寄存器的。

在详细描述整个状态机中的每一个状态之前,首先让我们来想一想:要通过边界扫描链

来观察和控制芯片的输入和输出,需要做些什么?如果需要捕获芯片某个管脚上的输出,首

先需要把该管脚上的输出装载到边界扫描链的寄存器单元里去,然后通过 TDO 输出,这样我

们就可以从 TDO 上得到相应管脚上的输出信号。如果要在芯片的某个管脚上加载一个特定的

信号,则首先需要通过 TDI 把期望的信号移位到与相应管脚相连的边界扫描链的寄存器单元

里去,然后把该寄存器单元的值加载到相应的芯片管脚。下面,让我们一起来看看每个状态

具体表示什么意思?完成什么功能?

Test-Logic Reset

系统上电后,TAP Controller 自动进入该状态。在该状态下,测试部分的逻辑电路全部被

TWENTYONE XUZHOUHE@HOTMAIL.COM & DUYUNHAI DUYUNHAI@HOTMAIL.COM

3

OPEN-JTAG

禁用,以保证芯片核心逻辑电路的正常工作。通过 TRST 信号也可以对测试逻辑电路进

行复位,使得 TAP Controller 进入 Test-Logic Reset 状态。前面我们说过 TRST 是可选的

一个信号接口,这是因为在 TMS 上连续加 5 个 TCK 脉冲宽度的“1”信号也可以对测试

逻辑电路进行复位,使得 TAP Controller 进入 Test-Logic Reset 状态。所以,在不提供 TRST

信号的情况下,也不会产生影响。在该状态下,如果 TMS 一直保持为“1”,TAP Controller

将保持在 Test-Logic Reset 状态下;如果 TMS 由“ 1”变 为“ 0”(在 TCK 的上升沿触发),

将使 TAP Controller 进入 Run-Test/Idle 状态。

Run-Test/Idle

这个是 TAP Controller 在不同操作间的一个中间状态。这个状态下的动作取决于当前指令

寄存器中的指令。有些指令会在该状态下执行一定的操作,而有些指令在该状态下不需

要执行任何操作。在该状态下,如果 TMS 一直保持为“0”,TAP Controller 将一直保持

在 Run-Test/Idle 状态下;如果 TMS 由“ 0”变 为“ 1”(在 TCK 的上升沿触发),将 使 TAP

Controller 进入 Select-DR-Scan 状态。

Select-DR-Scan

这是一个临时的中间状态。如果 TMS 为“0” (在 TCK 的上升沿触发),

TAP Controller

进入 Capture-DR 状态,后续的系列动作都将以数据寄存器作为操作对象;如果 TMS 为

“1” (在 TCK 的上升沿触发),TAP Controller 进入 Select-IR-Scan 状态。

Capture-DR

当 TAP Controller 在这个状态中,在 TCK 的上升沿,芯片输出管脚上的信号将被“捕获”

到与之对应的数据寄存器的各个单元中去。如果 TMS 为“ 0” (在 TCK 的上升沿触发),

TAP Controller 进入 Shift-DR 状态;如果 TMS 为“1” (在 TCK 的上升沿触发),TAP

Controller 进入 Exit1-DR 状态。

Shift-DR

在这个状态中,由 TCK 驱动,每一个时钟周期,被连接在 TDI 和 TDO 之间的数据寄存

器将从 TDI 接收一位数据,同时通过 TDO 输出一位数据。如果 TMS 为“0” (在 TCK

的上升沿触发),TAP Controller 保持在 Shift-DR 状态; 如果 TMS 为“1” (在 TCK 的

上升沿触发),TAP Controller 进入到 Exit1-DR 状态。假设当前的数据寄存器的长度为 4。

如果 TMS

保持为 0,那在 4 个 TCK 时钟周期后,该数据寄存器中原来的 4 位数据(一

般是在 Capture-DR 状态中捕获的数据)将从 TDO 输出来;同时该数据寄存器中的每个

寄存器单元中将分别获得从 TDI 输入的 4 位新数据。

Update-DR

在 Update-DR 状态下,由 TCK 上升沿驱动,数据寄存器当中的数据将被加载到相应的芯

片管脚上去,用以驱动芯片。在该状态下,如果 TMS 为“0”,TAP Controller 将回到

Run-Test/Idle 状态;如果 TMS 为“1”,TAP Controller 将进入 Select-DR-Scan 状态。

Select-IR-Scan

这是一个临时的中间状态。如果 TMS 为“0” (在 TCK 的上升沿触发),TAP Controller

进入 Capture-IR 状态,后续的系列动作都将以指令寄存器作为操作对象;如果 TMS 为

“1” (在 TCK 的上升沿触发),TAP Controller 进入 Test-Logic Reset 状态。

Capture-IR

当 TAP Controller 在这个状态中,在 TCK 的上升沿,一个特定的逻辑序列将被装载到指

令寄存器中去。如果 TMS 为“ 0” (在 TCK 的上升沿触发),TAP Controller 进入 Shift-IR

状态;如果 TMS 为“1”

(在 TCK 的上升沿触发),TAP Controller 进入 Exit1-IR 状态。

Shift-IR

在这个状态中,由 TCK 驱动,每一个时钟周期,被连接在 TDI 和 TDO 之间的指令寄存

TWENTYONE XUZHOUHE@HOTMAIL.COM & DUYUNHAI DUYUNHAI@HOTMAIL.COM

4

OPEN-JTAG

器将从 TDI 接收一位数据,同时通过 TDO 输出一位数据。如果 TMS 为“0” (在 TCK

的上升沿触发),TAP Controller 保持在 Shift-IR 状态; 如果 TMS 为“1” (在 TCK 的

上升沿触发),TAP Controller 进入到 Exit1-IR 状态。假设指令寄存器的长度为 4。如果

TMS 保持为 0,那 在 4 个 TCK 时钟周期后,指令寄存器中原来的 4bit 长的特定逻辑序列

(在 Capture-IR 状态中捕获的特定逻辑序列)将从 TDO 输出来,该特定的逻辑序列可以

用来判断操作是否正确;同时指令寄存器将获得从 TDI 输入的一个 4bit 长的新指令。

Update-IR

在这个状态中,在 Shift-IR 状态下输入的新指令将被用来更新指令寄存器。

说了那么多,下面,让我们先看看指令寄存器和数据寄存器访问的一般过程,以便建立一个

直观的概念。

1. 系统上电,TAP Controller 进入 Test-Logic Reset 状态,然后依次进入:Run-Test/Idle

Select-DR-Scan Select-IR-Scan Capture-IR Shift-IR Exit1-IR Update-IR,

最后回到 Run-Test/Idle 状态。在 Capture-IR 状态中,一个特定的逻辑序列被加载到

指令寄存器当中;然后进入到 Shift-IR 状态。在 Shift-IR 状态下,通过

TCK 的驱动,

可以将一条特定的指令送到指令寄存器当中去。每条指令都将确定一条相关的数据

寄存器。然后从 Shift-IR Exit1-IR Update-IR。在 Update-IR 状态,刚才输入到指

令寄存器中的指令将用来更新指令寄存器。最后,进入到 Run-Test/Idle 状态,指令

生效,完成对指令寄存器的访问。

2. 当前可以访问的数据寄存器由指令寄存器中的当前指令决定。要访问由刚才的指令

选定的数据寄存器,需要以 Run-Test/Idle 为起点,依次进入 Select-DR-Scan

Capture-DR Shift-DR Exit1-DR Update-DR,最后回到 Run-Test/Idle 状态。在

这个过程当中,被当前指令选定的数据寄存器会被连接在 TDI 和 TDO 之间。通过

TDI 和 TDO,就可以将新的数据加载到数据寄存器当中去,同时,也可以捕获数据

寄存器中的数据。具体过程如下。在 Capture-DR 状态中,由 TCK 的驱动,芯片管脚

上的输出信号会被“捕获”到相应的边界扫描寄存器单元中去。这样,当前的数据

寄存器当中就记录了芯片相应管脚上的输出信号。接下来从 Capture-DR 进入到

Shift-DR 状态中去。在 Shift-DR 状态中,由 TCK 驱动,在每一个时钟周期内,一位

新的数据可以通过 TDI 串行输入到数据寄存器当中去,同时,数据寄存器可以通过

TDO 串行输出一位先前捕获的数据。在经过与数据寄存器长度相同的时钟周期后,

就可以完成新信号的输入和捕获数据的输出。接下来通过 Exit1-DR 状态进入到

Update-DR 状态。在 Update-DR 状态中,数据寄存器中的新数据被加载到与数据寄

存器的每个寄存器单元相连的芯片管脚上去。最后,回到 Run-Test/Idle 状态,完成

对数据寄存器的访问。

上面描述的就是通过 TAP 对数据寄存器进行访问的一般流程。会不会还是觉得很抽象?让我

们来看一个更直观的例子。现在假设,TAP Controller 现在处在 Run-Test/Idle 状态,指令寄存

器当中已经成功的写入了一条新的指令,该指令选定的是一条长度为 6 的边界扫描链。下面

让我们来看看实际如何来访问这条边界扫描链。图 2 所示的是测试芯片及其被当前指令选定

的长度为 6 的边界扫描链。由图 2 可以看出,当前选择的边界扫描链由 6 个边界扫描移位寄

存器单元组成,并且被连接在 TDI 和

TDO 之间。TCK 时钟信号与每个边界扫描移位寄存器

单元相连。每个时钟周期可以驱动边界扫描链的数据由 TDI 到 TDO 的方向移动一位,这样,

新的数据可以通过 TDI 输入一位,边界扫描链的数据可以通过 TDO 输出一位。经过 6 个时钟

周期,就可以完全更新边界扫描链里的数据,而且可以将边界扫描链里捕获的 6 位数据通过

TWENTYONE XUZHOUHE@HOTMAIL.COM & DUYUNHAI DUYUNHAI@HOTMAIL.COM

5

剩余21页未读,继续阅读

NewLsc

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0