基于基于FPGA的的DDR3六通道读写防冲突设计六通道读写防冲突设计

为了解决期货行情数据加速处理中多个通道同时访问DDR3时出现的数据读写冲突问题,实现了一种基于FPGA

的DDR3六通道读写防冲突设计,完成了对单片DDR3内存条的多通道实时访问控制需求。通过ChipScope工具采

样结果证明了设计的可行性,提高了并行处理的速度,极大程度地降低了期货行情数据处理中行情计算的时间

开销,最高通道速率可达5.0 GB/s以上,带宽利用率可达80%以上,在多通道数据读写应用中具有很高的实用价

值。

0 引言引言

基于FPGA的期货行情数据加速处理过程中,不同的消息类型采用并行处理的方式,并且每一次的处理结果需要使用内存来

缓存一次行情数据信息。行情数据信息容量巨大,片上存储难以满足需求,采用DDR3 SDRAM成为首选方法

[1]

。但由于

DDR3只有一套数据访问通道,不能满足多个通道同时访问的需求

[2]

。此前的对于SDRAM的多通道解决方案中,比如曹一

江

[3]

等设计的基于NPI总线的片外存储器,最大带宽可达743 Mb/s;樊博

[4]

等使用UI接口,DDR3通信的最大带宽可达3.8

Gb/s;张宇嘉

[5]

等设计的基于AXI4的DDR3多端口方案虽然传输速率有所提高,但由于AXI4协议本身的复杂性增加了开发使

用的难度。本文实现并验证了期货行情数据加速处理中基于FPGA的DDR3六通道UI接口读写防冲突设计,简化了DDR3多通

道读写的复杂度,随着有效数据周期的提升,最高端口速率可达5.0 GB/s以上,带宽利用率可达80%以上。

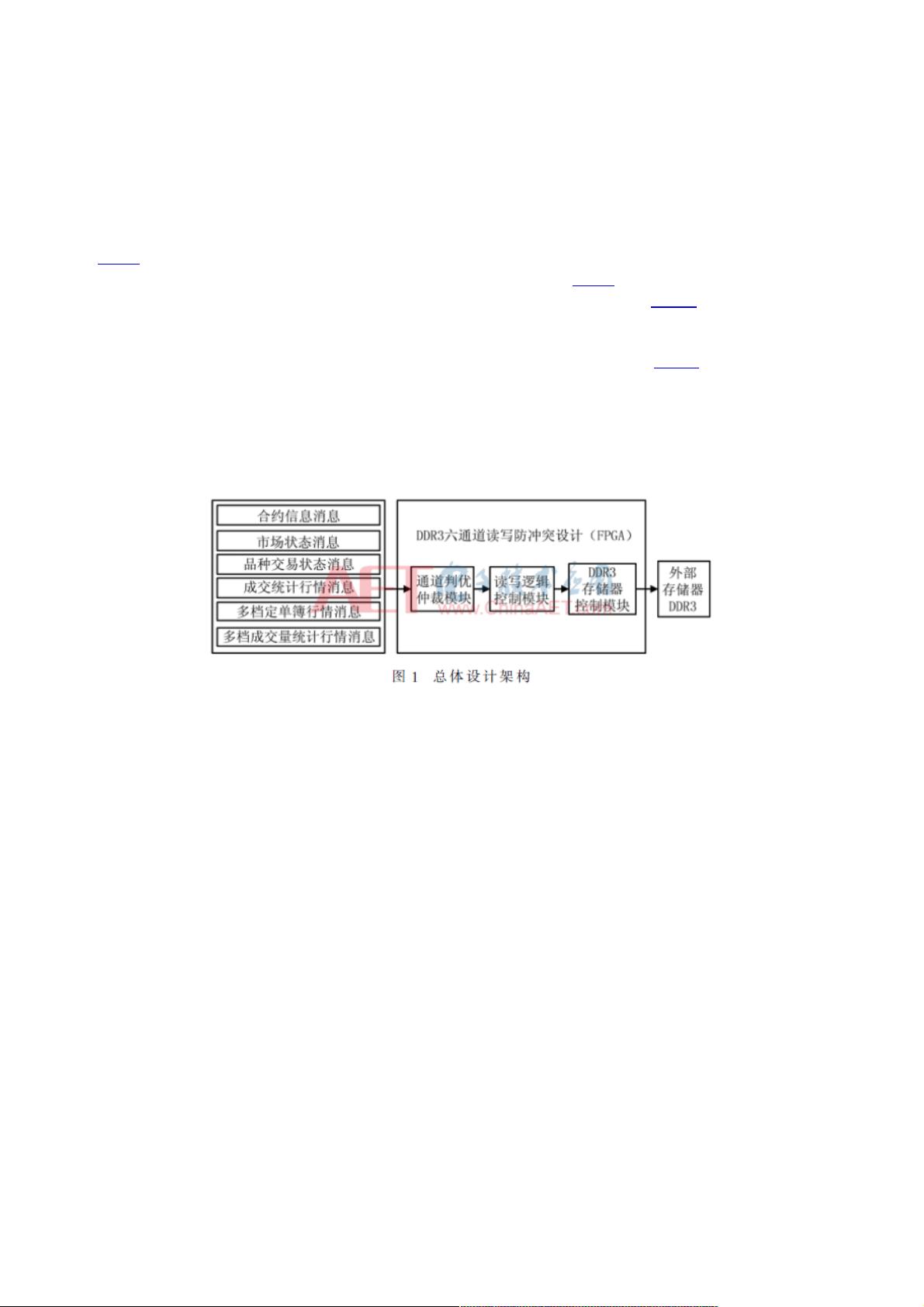

1 总体设计架构总体设计架构

本文所设计的六通道读写防冲突总体架构如图1所示,主要包括通道判优仲裁模块、读写逻辑控制模块和DDR3存储器控制

模块。

DDR3存储控制器模块采用Xilinx公司的MIG核,用户只需要通过IP核的GUI选择内存芯片并进行相关参数设置,即可完成

DDR3的配置工作

[6]

。

通道判优仲裁模块将对六路通道进行仲裁,对于同一时刻有读写请求的不同通道,该模块按照优先级的高低判定访问DDR3

的顺序,利用中断思想解决多通道读写的冲突问题。

读写逻辑控制模块控制DDR3的接口生成,根据不同操作完成对应接口的时序控制

[7]

,进而实现对DDR3的正确读写访问。

2 DDR3存储器控制模块设计存储器控制模块设计

DDR3 IP核生成的控制器逻辑框图如图2所示,采用UI接口的方式相比于AXI4接口,不需要自己组织数据,容易操作,大大

简化了DDR3的使用复杂度,为DDR3的扩展使用带来了方便

[8]

。

评论1