GNU Radio入门指南:配置安装详解

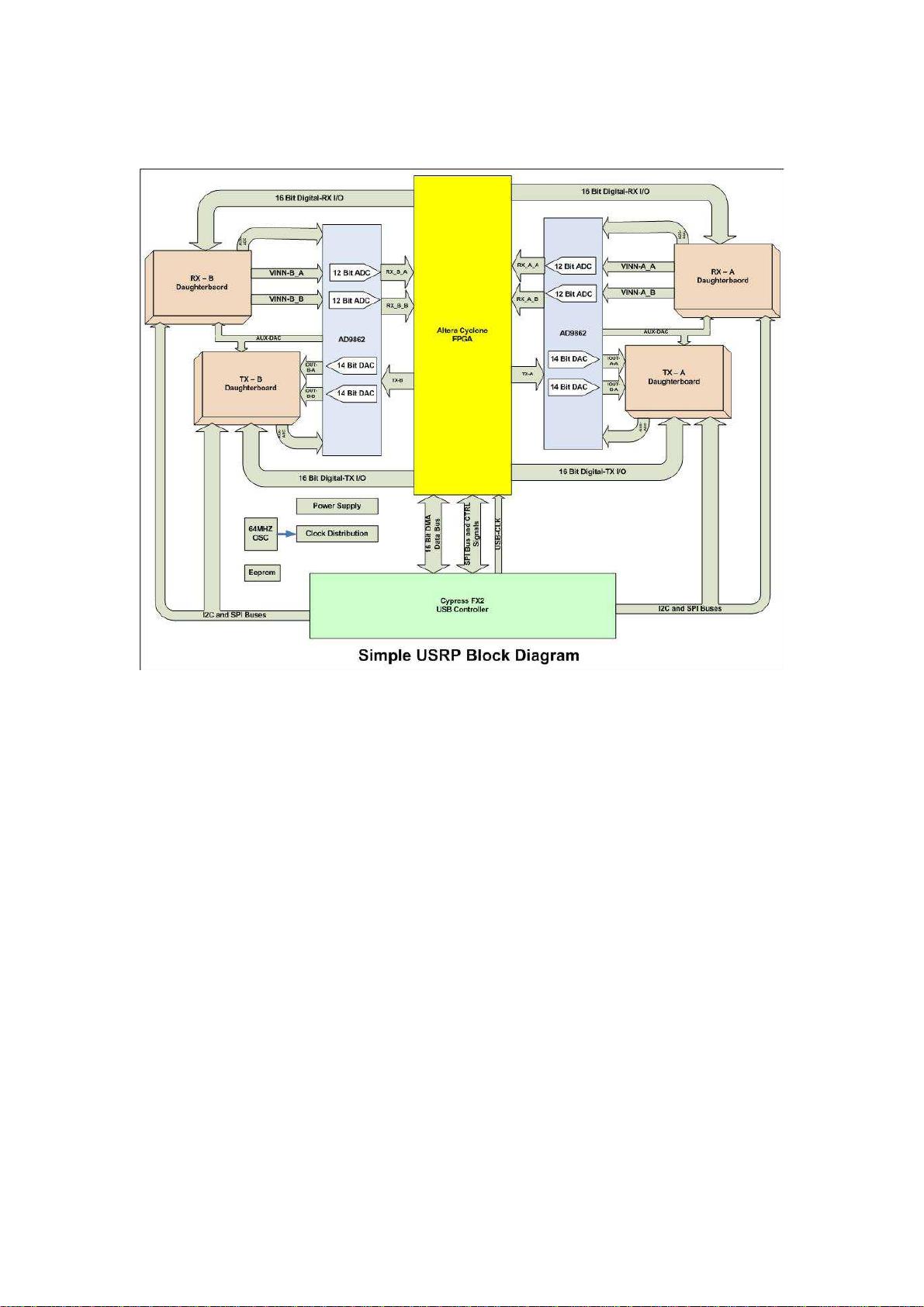

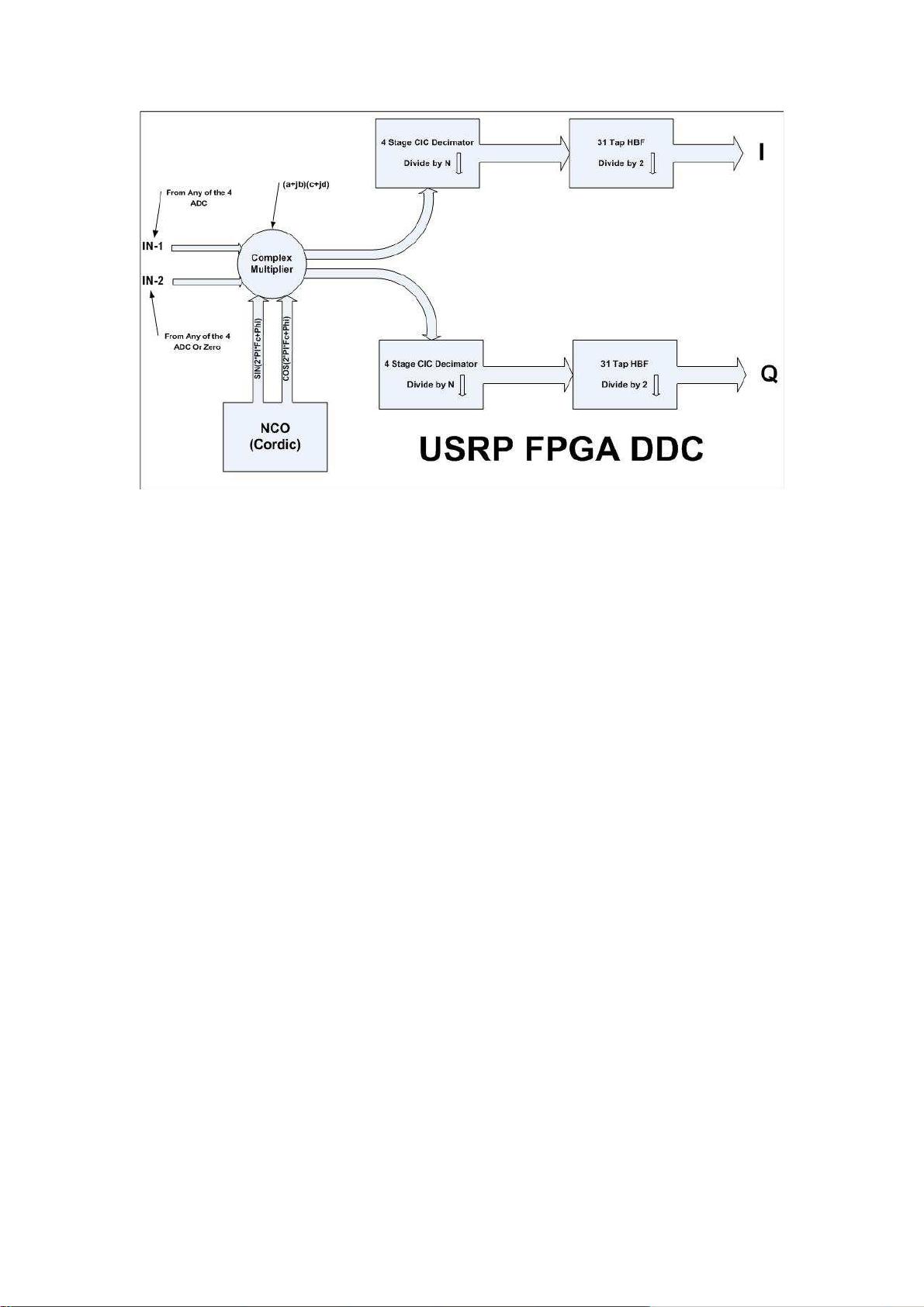

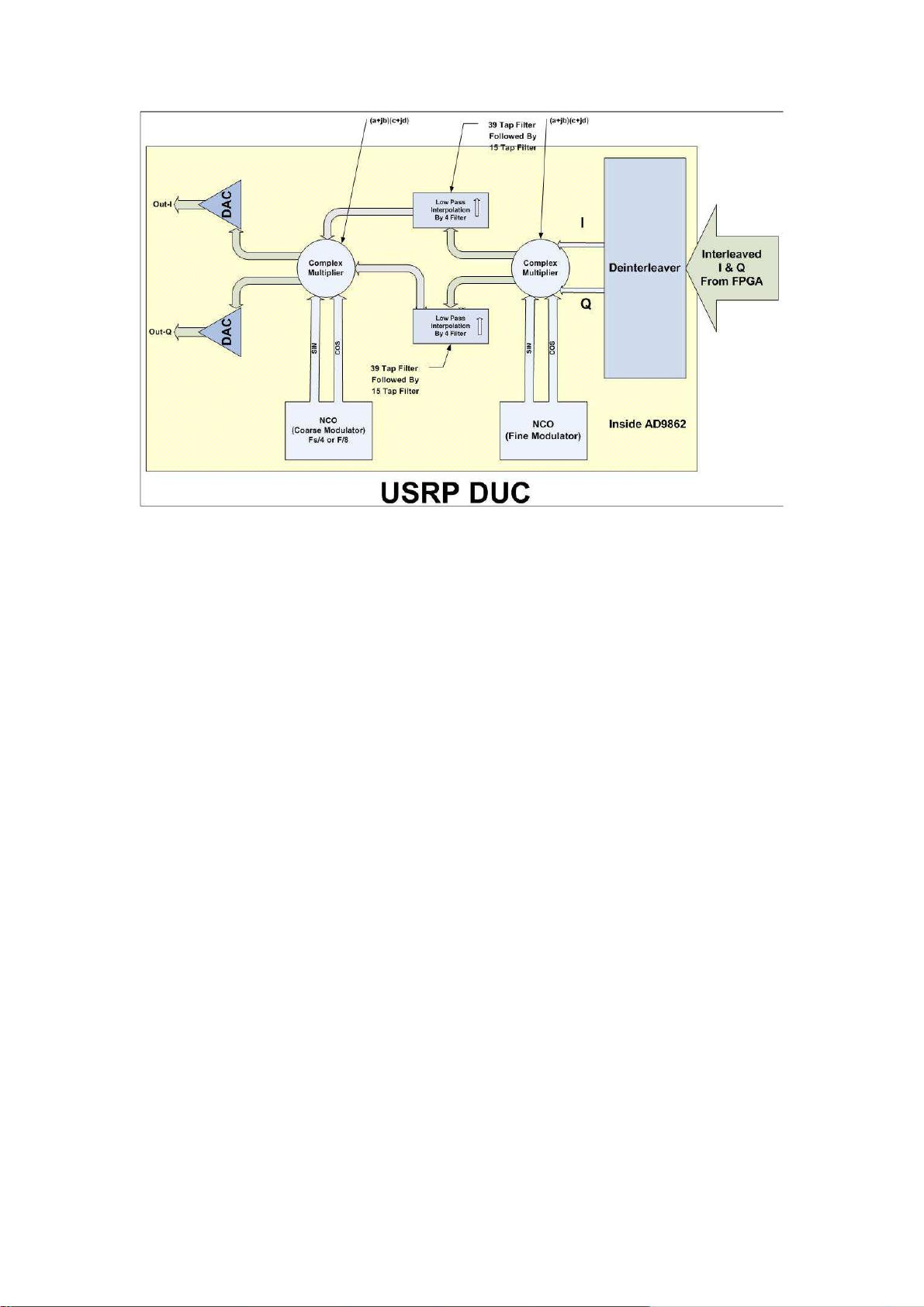

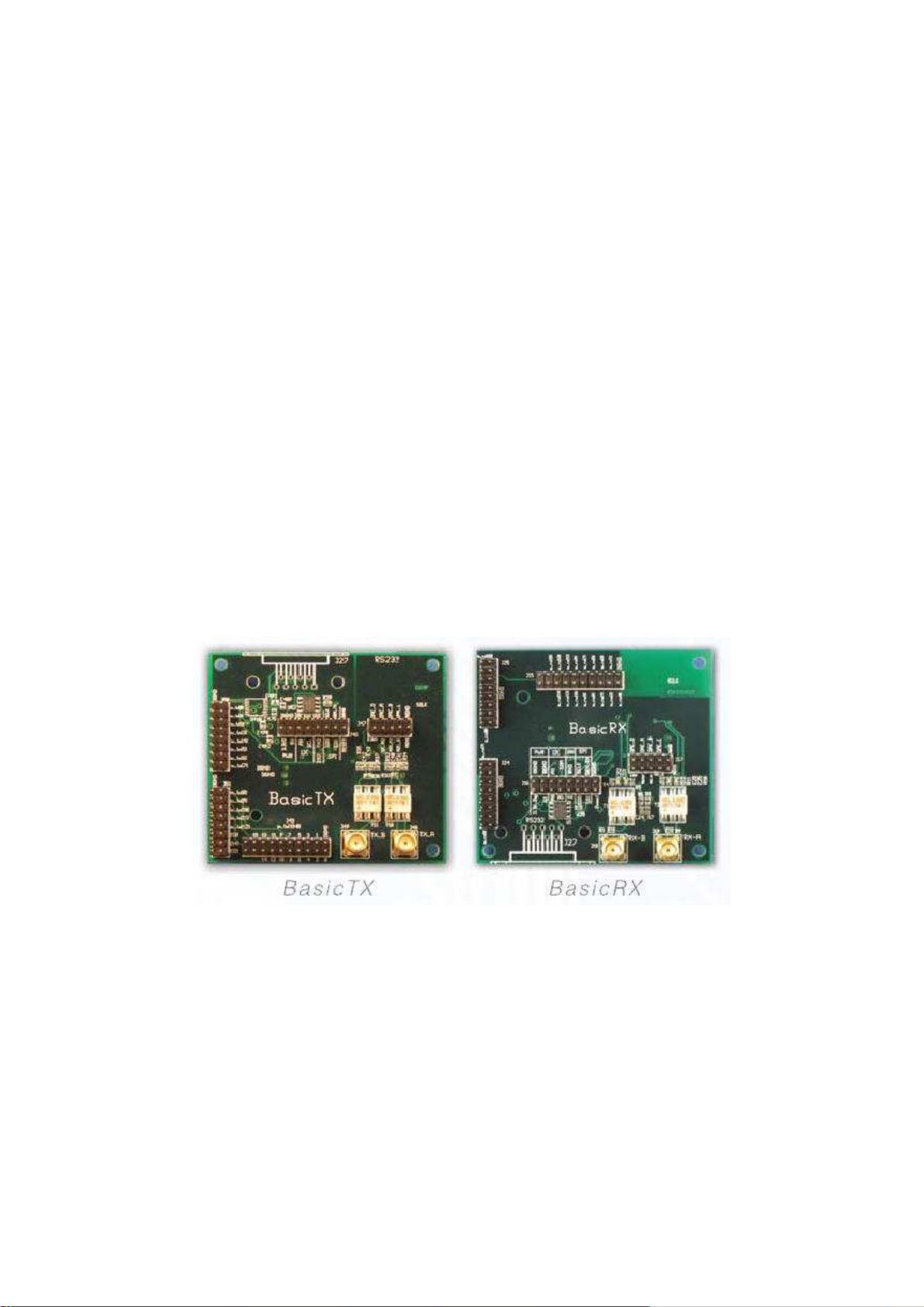

"《GNU Radio入门学校材料》是一份详细介绍了软件无线电软件平台GNU Radio及其硬件平台USRP的教程。GNU Radio是一个开源工具包,特别适合初学者和专业人士使用,因为它能与经济实惠的USRP配合,形成一个高度灵活的开发环境,让用户能够像开发小型软件一样设计无线通信设备。它以低成本和高度的灵活性在全球范围内吸引了众多用户,包括中国,如GNU Radio中国社区。

该文档的作者黄琳是中国早期GNU Radio用户的代表之一,他和他的团队在该项目上积累了丰富的实践经验。鉴于新成员在理解和使用GNU Radio时常面临的挑战,黄琳萌生了编写一本中文版教程的想法,以便让初次接触者能更快地掌握其基本操作,并激发更多人的创新思维。

这份教程涵盖了GNU Radio的基础配置、安装过程以及常见应用场景。虽然书中提到的OpenBTS部分尚未完成,但作者承诺会尽快更新。书中旨在提供一种直观的学习路径,无论是新手还是已有经验的用户都能从中获益。尽管出于业余团队的创作条件,可能存在一些错误,但作者鼓励读者通过论坛和邮件交流提供反馈,共同提升教程质量。

这是一份实用且富有价值的资源,不仅帮助用户快速上手GNU Radio,还推动了软件无线电技术在中国和全球的发展。"

457 浏览量

3165 浏览量

191 浏览量

392 浏览量

2009-06-02 上传

点击了解资源详情

lhl871107

- 粉丝: 0

最新资源

- 英数图像识别库:验证码的通用处理技术

- 全面技术项目源码合集:商业名片设计与整站开发教程

- Android万能下载器:在线下载任意格式文件

- ACAD2008 Express汉化补丁使用指南

- C语言核心概念:指针、活动记录与内存管理

- webCAMotion:网络摄像头模拟鼠标的开源程序

- Axure高效设计模板:导航条与版权页母版

- C语言实现最小生成树算法及路径自动生成

- SPM8数据预处理及分析批处理工具

- 绿色大气个人摄影相册网站模板及全技术领域源码分享

- Android全屏注册界面的设计与实现技巧

- 易通远程屏幕监控系统安装与卸载详细指南

- Ehcache复制机制详解与集群环境演示教程

- Facebook Messenger终端控制:全新Python自动化脚本

- MATLAB动态规划程序包:优化算法实践

- Android ADT-22.0.5版本发布,探索新特性