没有合适的资源?快使用搜索试试~ 我知道了~

首页altera 推荐的代码风格

资源详情

资源评论

资源推荐

© November 2008 Altera Corporation Quartus II Handbook Version 8.1 Volume 1: Design and Synthesis

6. Recommended HDL Coding Styles

Introduction

HDL coding styles can have a significant effect on the quality of results that you

achieve for programmable logic designs. Synthesis tools optimize HDL code for both

logic utilization and performance. However, sometimes the best optimizations require

human understanding of the design, and synthesis tools have no information about

the purpose or intent of the design. You are often in the best position to improve your

quality of results.

This chapter addresses HDL coding style recommendations to ensure optimal

synthesis results when targeting Altera

®

devices, including the following sections:

■ “Quartus II Language Templates” on page 6–1

■ “Using Altera Megafunctions” on page 6–2

■ “Instantiating Altera Megafunctions in HDL Code” on page 6–3

■ “Inferring Multiplier and DSP Functions from HDL Code” on page 6–6

■ “Inferring Memory Functions from HDL Code” on page 6–11

■ “Coding Guidelines for Registers and Latches” on page 6–34

■ “General Coding Guidelines” on page 6–44

■ “Designing with Low-Level Primitives” on page 6–68

f For additional guidelines about structuring your design, refer to the Design

Recommendations for Altera Devices and the Quartus II Design Assistant chapter in

volume 1 of the Quartus II Handbook. For additional hand-crafted techniques you can

use to optimize design blocks for the adaptive logic modules (ALMs) in many Altera

devices, including a collection of circuit building blocks and related discussions, refer

to the Advanced Synthesis Cookbook: A Design Guide for Stratix II and Stratix III Devices.

For style recommendations, options, or HDL attributes specific to your synthesis tool

(including Quartus

®

II Integrated Synthesis and other EDA tools), refer to the tool

vendor’s documentation or the appropriate chapter in the Synthesis section in

volume 1 of the Quartus II Handbook.

Quartus II Language Templates

The Quartus II software provides Verilog HDL, VHDL, AHDL, Tcl script, and

megafunction language templates that can help you with your design.

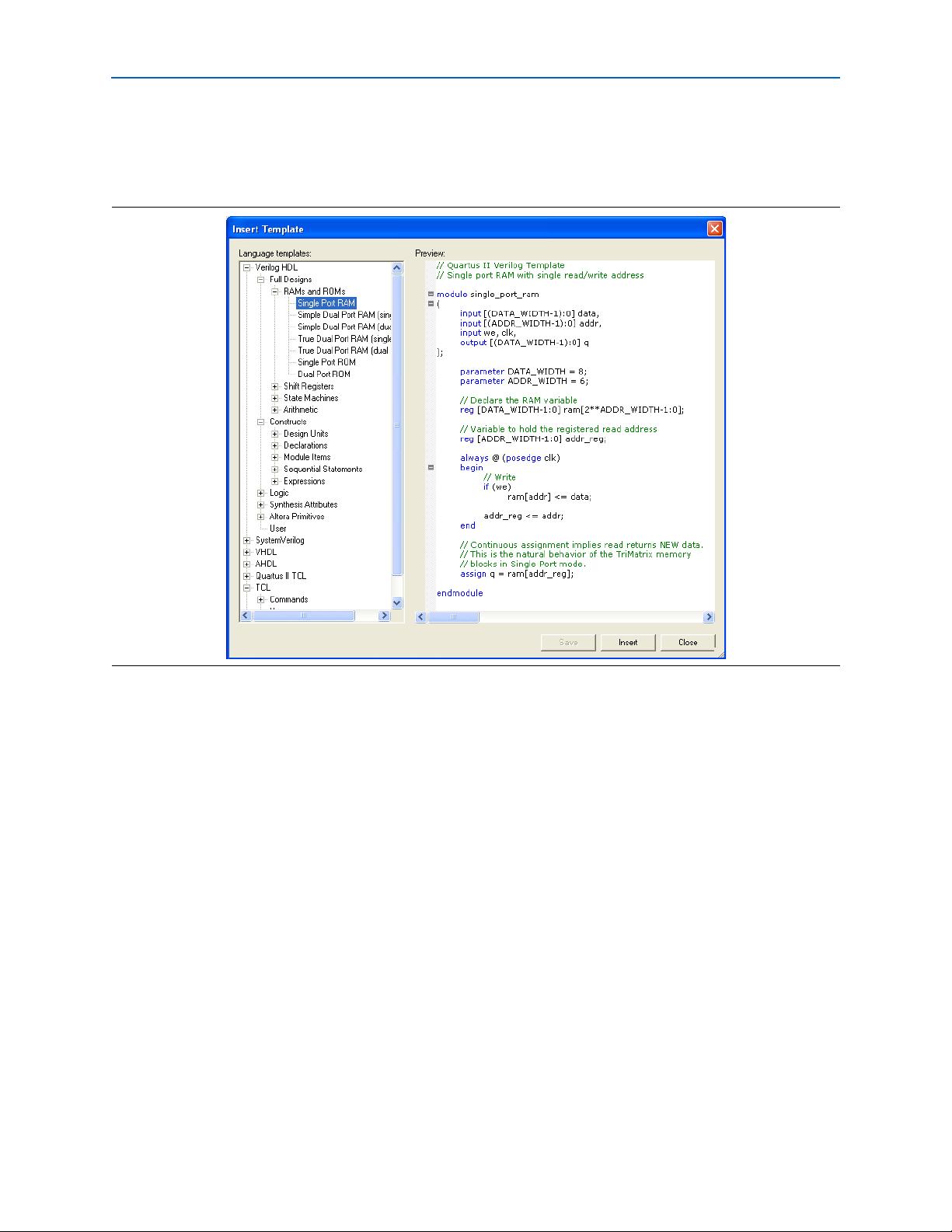

Many of the Verilog HDL and VHDL examples in this document correspond with

examples in the templates. You can easily insert examples from this document into

your HDL source code using the Insert Template dialog box in the Quartus II user

interface, shown in Figure 6–1.

QII51007-8.1.0

6–2 Chapter 6: Recommended HDL Coding Styles

Using Altera Megafunctions

Quartus II Handbook Version 8.1 Volume 1: Design and Synthesis © November 2008 Altera Corporation

To open the Insert Template dialog box when you have a file open in the Quartus II

Text Editor, on the Edit menu, click Insert Template. Alternatively, you can right-click

in the Text Editor window and choose Insert Template.

Using Altera Megafunctions

Altera provides parameterizable megafunctions that are optimized for Altera device

architectures. Using megafunctions instead of coding your own logic saves valuable

design time. Additionally, the Altera-provided megafunctions may offer more

efficient logic synthesis and device implementation. You can scale the megafunction’s

size and set various options by setting parameters. Megafunctions include the library

of parameterized modules (LPM) and Altera device-specific megafunctions.

To use megafunctions in your HDL code, you can instantiate them as described in

“Instantiating Altera Megafunctions in HDL Code” on page 6–3.

Sometimes it is preferable to make your code independent of device family or vendor.

In this case, you might not want to instantiate megafunctions directly. For some types

of logic functions, such as memories and DSP functions, you can infer a megafunction

instead of instantiating it. Synthesis tools, including Quartus II integrated synthesis,

recognize certain types of HDL code and automatically infer the appropriate

megafunction. The synthesis tool uses the Altera megafunction code when compiling

your design—even when you do not specifically instantiate the megafunction.

Synthesis tools infer megafunctions to take advantage of logic that is optimized for

Altera devices or to target dedicated architectural blocks.

Figure 6–1. Insert Template Dialog Box

Chapter 6: Recommended HDL Coding Styles 6–3

Instantiating Altera Megafunctions in HDL Code

© November 2008 Altera Corporation Quartus II Handbook Version 8.1 Volume 1: Design and Synthesis

In cases where you prefer to use generic HDL code instead of instantiating a

megafunction, follow the guidelines and coding examples in “Inferring Multiplier

and DSP Functions from HDL Code” on page 6–6 and “Inferring Memory Functions

from HDL Code” on page 6–11 to ensure your HDL code infers the appropriate Altera

megafunction.

1 You must use megafunctions to access some Altera device-specific architecture

features. You can infer or instantiate megafunctions to target some features such as

memory and DSP blocks. You must instantiate megafunctions to target certain device

and high-speed features such as LVDS drivers, PLLs, transceivers, and double-data

rate input/output (DDIO) circuitry.

For some designs, generic HDL code can provide better results than instantiating a

megafunction. Refer to the following general guidelines and examples that describe

when to use standard HDL code and when to use megafunctions:

■ For simple addition or subtraction functions, use the + or – symbol instead of an

LPM function. Instantiating an LPM function for simple arithmetic operations can

result in a less efficient result because the function is hard coded and the synthesis

algorithms cannot take advantage of basic logic optimizations.

■ For simple multiplexers and decoders, use array notation (such as out =

data[sel]) instead of an LPM function. Array notation works very well and has

simple syntax. You can use the lpm_mux function to take advantage of

architectural features such as cascade chains in APEX

™

series devices, but use the

LPM function only if you understand the device architecture in detail and want to

force a specific implementation.

■ Avoid division operations where possible. Division is an inherently slow

operation. Many designers use multiplication creatively to produce division

results.

Instantiating Altera Megafunctions in HDL Code

The following sections describe how to use megafunctions by instantiating them in

your HDL code with the following methods:

■ “Instantiating Megafunctions Using the MegaWizard Plug-In Manager”—You can

use the MegaWizard

®

Plug-In Manager to parameterize the function and create a

wrapper file.

■ “Creating a Netlist File for Other Synthesis Tools”—You can optionally create a

netlist file instead of a wrapper file.

■ “Instantiating Megafunctions Using the Port and Parameter Definition”—You can

instantiate the function directly in your HDL code.

6–4 Chapter 6: Recommended HDL Coding Styles

Instantiating Altera Megafunctions in HDL Code

Quartus II Handbook Version 8.1 Volume 1: Design and Synthesis © November 2008 Altera Corporation

Instantiating Megafunctions Using the MegaWizard Plug-In Manager

Use the MegaWizard Plug-In Manager as described in this section to create

megafunctions in the Quartus II GUI that you can instantiate in your HDL code. The

MegaWizard Plug-In Manager provides a graphical user interface to customize and

parameterize megafunctions, and ensures that you set all megafunction parameters

properly. When you finish setting parameters, you can specify which files you want to

be generated. Depending on which language you choose, the MegaWizard Plug-In

Manager instantiates the megafunction with the correct parameters and generates a

megafunction variation file (wrapper file) in Verilog HDL (.v), VHDL (.vhd), or

AHDL (.tdf), along with other supporting files.

The MegaWizard Plug-In Manager provides options to create the following files:

■ A sample instantiation template for the language of the variation file

(_inst.v|vhd|tdf).

■ Component Declaration File (.cmp) that can be used in VHDL Design Files

■ ADHL Include File (.inc) that can be used in Text Design Files (.tdf)

■ Quartus II Block Symbol File (.bsf) for schematic designs

■ Verilog HDL module declaration file that can be used when instantiating the

megafunction as a black box in a third-party synthesis tool (_bb.v).

■ If you enable the option to generate a synthesis area and timing estimation netlist,

the MegaWizard Plug-In Manager generates an additional synthesis netlist file

(_syn.v). Refer to “Creating a Netlist File for Other Synthesis Tools” on page 6–5

for details.

Table 6–1 lists and describes the files generated by the MegaWizard Plug-In Manager.

Table 6 –1. MegaWizard Plug-In Manager Generated Files (Part 1 of 2)

File Description

<output file>.v (1) Verilog HDL Variation Wrapper File—Megafunction wrapper file for instantiation in a

Verilog HDL design.

<output file>.vhd (1) VHDL Variation Wrapper File—Megafunction wrapper file for instantiation in a VHDL design.

<output file>.tdf (1) AHDL Variation Wrapper File—Megafunction wrapper file for instantiation in an AHDL design.

<output file>.inc ADHL Include File—Used in AHDL designs.

<output file>.cmp Component Declaration File—Used in VHDL designs.

<output file>.bsf Block Symbol File—Used in Quartus II Block Design Files (.bdf).

<output file>_inst.v Verilog HDL Instantiation Template—Sample Verilog HDL instantiation of the module in the

megafunction wrapper file.

<output file>_inst.vhd VHDL Instantiation Template—Sample VHDL instantiation of the entity in the megafunction

wrapper file.

<output file>_inst.tdf Text Design File Instantiation Template—Sample AHDL instantiation of the subdesign in the

megafunction wrapper file.

<output file>_bb.v Black box Verilog HDL Module Declaration—Hollow-body module declaration that can be

used in Verilog HDL designs to specify port directions when creating black boxes in

third-party synthesis tools.

Chapter 6: Recommended HDL Coding Styles 6–5

Instantiating Altera Megafunctions in HDL Code

© November 2008 Altera Corporation Quartus II Handbook Version 8.1 Volume 1: Design and Synthesis

Creating a Netlist File for Other Synthesis Tools

When you use certain megafunctions with third-party EDA synthesis tools (that is,

tools other than Quartus II integrated synthesis), you can optionally create a netlist for

area and timing estimation instead of a wrapper file.

The netlist file is a representation of the customized logic used in the Quartus II

software. The file provides the connectivity of architectural elements in the

megafunction but may not represent true functionality. This information enables

certain third-party synthesis tools to better report area and timing estimates. In

addition, synthesis tools can use the timing information to focus timing-driven

optimizations and improve the quality of results.

To generate the netlist, turn on Generate a synthesis area and timing estimation

netlist on the EDA page of the MegaWizard Plug-In Manager. The netlist file is called

<output file>_syn.v. If you use this netlist for synthesis, you must include the

megafunction wrapper file <output file>.v|vhd in your Quartus II project for

placement and routing.

Your synthesis tool may call the Quartus II software in the background to generate

this netlist, so you might not be required to perform the extra step of turning on this

option.

f For information about support for area and timing estimation netlists in your

synthesis tool, refer to the tool vendor’s documentation or the appropriate chapter in

the Synthesis section in volume 1 of the Quartus II Handbook.

Instantiating Megafunctions Using the Port and Parameter Definition

You can instantiate the megafunction directly in your Verilog HDL, VHDL, or AHDL

code by calling the megafunction and setting its parameters as you would any other

module, component, or subdesign.

f Refer to the specific megafunction in the Quartus II Help for a list of the megafunction

ports and parameters. The Quartus II Help also provides a sample VHDL component

declaration and AHDL function prototype for each megafunction.

1 Altera strongly recommends that you use the MegaWizard Plug-In Manager for

complex megafunctions such as PLLs, transceivers, and LVDS drivers. For details

about using the MegaWizard Plug-In Manager, refer to “Instantiating Megafunctions

Using the MegaWizard Plug-In Manager” on page 6–4.

<output file>_syn.v (2) Synthesis area and timing estimation netlist—Megafunction netlist used by certain third-party

synthesis tools to improve area and timing estimations.

Notes to Ta ble 6– 1 :

(1) The MegaWizard Plug-In Manager generates either the Verilog HDL, VHDL, or AHDL Variation Wrapper File, depending on the language you

select for the output file on the megafunction-selection page of the wizard.

(2) The MegaWizard Plug-In Manager generates this file only if you turn on the Generate a synthesis area and timing estimation netlist option

on the EDA page of the wizard.

Table 6 –1. MegaWizard Plug-In Manager Generated Files (Part 2 of 2)

File Description

剩余71页未读,继续阅读

tian_yi8888

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0