没有合适的资源?快使用搜索试试~ 我知道了~

首页uvm学习总结_2021.1.11

uvm学习总结_2021.1.11

需积分: 0 44 下载量 200 浏览量

更新于2023-03-03

评论 2

收藏 8.73MB DOCX 举报

关于UVM几个机制的解释。 sequence机制 简单说明:sequence机制是为了独立出“生成transaction”的这部分操作而建立的机制。 特点: 支持多种uvm_do宏命令 有优先级仲裁机制,可以控制先后发送的顺序。 virtual sequence调度sequence发送的顺序。 寄存器模型内建检查读写功能的sequence。

资源详情

资源评论

资源推荐

UVM 基础

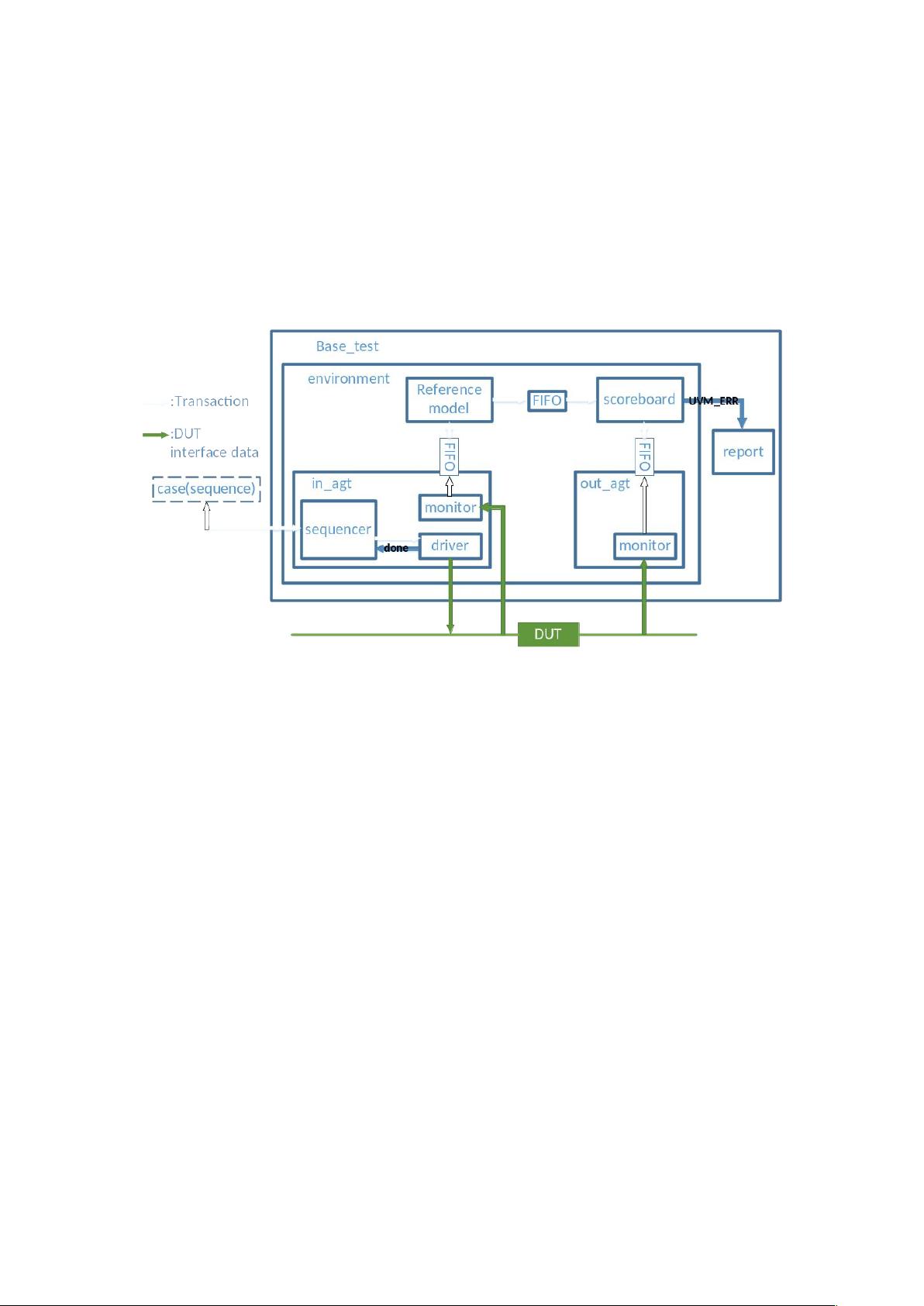

系统架构框图

这是 1 种测试用例的框图,每一种测试用例,都会生成这么一个架构。

transaction

声明、定义数据包格式,是需要测试的数据包,常用 random 函数去随机化数据用以

测试

eld_automation 注册,注册后才可以使用 uvm 中的 print、compare 等常用函数

driver

与 DUT 建立连接,使用 uvm_cong_db#机制

向 sequencer 请求 sequence,并在发送完成后,返回一个 done 给 sequencer。

将 transaction 转化成 interface 数据,进行发送

monitor

与 DUT 建立连接,使用 uvm_cong_db#机制

与 model 和 scoreboard 建立通信(TLM 机制),实现接收 transaction 功能用

`uvm_blocking_get_port#( my transaction) , 实 现 发 送 transaction 功 能 用

`uvm_analysis_port#(my transaction)

将 transaction 转化成 interface 数据,进行接收

sequencer

调度 sequence 和 driver,确保它们正常进行 transaction 的产生和发送。

agent

实例化 driver、monitor、sequencer

连接 drv 和 sequencer,drv.seq_item_port.connect(sqr.seq_item_export);

在 TLM 机制中准备好 monitor 的 ap(发送)口,准备好发送数据给 scoreboard 或

者 reference model , 实 现 接 收 transaction 功 能 用

`uvm_blocking_get_port#( my transaction) , 实 现 发 送 transaction 功 能 用

`uvm_analysis_port#(my transaction)

UVM_ACTIVE 机制,用来产生 i_agt 和 o_agt 这些可以自定义配置的 agent

reference model

接收 i_agt 发送过来的 transaction,发送 transaction 给 scoreboard,实现接收

transaction 功 能 用 `uvm_blocking_get_port#( my transaction) , 实 现 发 送

transaction 功能用 `uvm_analysis_port#(my transaction)

建立与 DUT 同样功能的模型,让 transaction 包进入模型进行工作,然后将输出发

送给 scoreboard

scoreboard

在 TLM 机制中准备好接收 monitor 和 model 的数据 port,实现接收 transaction

功能用`uvm_blocking_get_port#( my transaction),实现发送 transaction 功

能用 `uvm_analysis_port#(my transaction)

并行接收数据,然后进行 compare、report 等操作,

environment

实例化 agent、model、scoreboard

创建 TLM 中所需要用的 fo,在我的框图中是三个

连接 mdl 和 scoreboard,中间插入一个 fo,同理连接 mdl 和 i_agt,o_agt 和

scoreboard。

base_test

实例化 envrionment

打印最终验证结果

sequence(case)

`uvm_do(transaction),产生随机化数据的数据包 transaction

raise_objection ,drop_objection,uvm 的 objection 机制,用以启动和结束整

个平台

使 用 default_sequence 机 制 , 实 例 化 seq , 连 接 seq ( sequence ) 和

sqr(sequencer)

UVM 树形结构

get_parent 得到父节点的路径

get_child(string name) 得到子节点

UVM eld automation

宏

`uvm_object_utils_begin(my_transaction)

`uvm_eld_int(……)

`uvm_eld_real

`uvm_object_utils_end

常用函数

copy

compare

pack_bytes

unpack_bytes

UVM TLM

TLM :transaction level modeling

基本操作:

put

get

transport

基本端口:

PORT

EXPORT

IMP

特殊端口:

analysis_port/analysis_export

特殊点一:默认一对多通信。(普通的 port 是默认一对一通信)

特殊点二:没有阻塞和非阻塞的概念。(普通的 port 是分阻塞和非阻塞的概念)

特殊点三:只有 write 一个操作(普通的 port 有 put、try_put、can_put 等操作)

UVM_cong_db#

用于验证平台间的通信

`uvm_cong_db#()

层次优先

同一层次时间优先

check_cong_usage

剩余63页未读,继续阅读

影子才是本体

- 粉丝: 102

- 资源: 3

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 数据结构1800题含完整答案详解.doc

- 医疗企业薪酬系统设计与管理方案.pptx

- 界面与表面技术界面理论与表面技术要点PPT学习教案.pptx

- Java集合排序及java集合类详解(Collection、List、Map、Set)讲解.pdf

- 网页浏览器的开发 (2).pdf

- 路由器原理与设计讲稿6-交换网络.pptx

- 火电厂锅炉过热汽温控制系统设计.doc

- 企业识别CIS系统手册[收集].pdf

- 物业管理基础知识.pptx

- 第4章财务预测.pptx

- 《集成电路工艺设计及器件特性分析》——实验教学计算机仿真系.pptx

- 局域网内共享文件提示没有访问权限的问题借鉴.pdf

- 第5章网络营销策略.pptx

- 固井质量测井原理PPT教案.pptx

- 毕业实习总结6篇.doc

- UGNX建模基础篇草图模块PPT学习教案.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0