没有合适的资源?快使用搜索试试~ 我知道了~

首页MT53E512M32D2-LPDDR4 2GB.pdf

资源详情

资源评论

资源推荐

LPDDR4X SDRAM

MT53E512M32D2, MT53E1G32D4, MT53E2G32D8

Introduction

This product supports both LPDDR4 (V

DDQ

= 1.1V)

and LPDDR4X (V

DDQ

= 0.6V) operations. Only

LPDDR4X specification is available in this data sheet.

Refer to LPDDR4 SDRAM data sheet (document num-

ber: CCM005-554574167-10520) for LPDDR4 specifi-

cation.

Features

• Ultra-low-voltage core and I/O power supplies

–V

DD1

= 1.70–1.95V; 1.8V nominal

–V

DD2

= 1.06–1.17V; 1.1V nominal

–V

DDQ

= 0.57–0.65V; 0.6V nominal

• Frequency range

– 2133–10 MHz (data rate range: 4266–20 Mb/s/

pin)

•16n prefetch DDR architecture

• 8 internal banks per channel for concurrent opera-

tion

• Single-data-rate CMD/ADR entry

• Bidirectional/differential data strobe per byte lane

• Programmable READ and WRITE latencies (RL/WL)

• Programmable and on-the-fly burst lengths (BL =

16, 32)

• Directed per-bank refresh for concurrent bank op-

eration and ease of command scheduling

• Up to 8.53 GB/s per die (×16) , Up to 4.62 GB/s per

die (×8)

• On-chip temperature sensor to control self refresh

rate

• Partial-array self refresh (PASR)

• Selectable output drive strength (DS)

• Clock-stop capability

• RoHS-compliant, “green” packaging

• Programmable V

SS

(ODT) termination

Options Marking

•V

DD1

/V

DD2

/V

DDQ

: 1.8V/1.1V/0.6V E

• Array configuration

– 512 Meg × 32 (2 channels × 16 I/O) 512M32

– 1 Giga × 32 (2 channels × 16 I/O) 1G32

– 2 Giga × 32 (2 channels × 16 I/O) 2G32

• Device configuration

– 512M16 × 2 die in package D2

– 512M16 × 4 die in package D4

– 1024M8 × 8 die in package D8

• FBGA “green” package

– 200-ball WFBGA (10.0mm × 14.5mm) NP

– 200-ball VFBGA (10.0mm × 14.5mm) NQ/QD

• Speed grade, cycle time

– 467ps

@ RL = 36/40 (Normal latency)

@ RL = 40/44 (Byte mode latency)

-046

– 535ps

@ RL = 32/36 (Normal latency)

@ RL = 36/40 (Byte mode latency)

-053

• Operating temperature range

– –25°C to +85°C WT

• Revision :E

Micron Confidential and Proprietary Preliminary

‡

200b: x32 LPDDR4X SDRAM

Introduction

CCM005-554574167-10510

200b_j_z11n_ddp_qdp_8dp_lpddr4x.pdf – Rev. C 11/17 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2017 Micron Technology, Inc. All rights reserved.

‡Products and specifications discussed herein are for evaluation and reference purposes only and are subject to change by

Micron without notice. Products are only warranted by Micron to meet Micron’s production data sheet specifications.

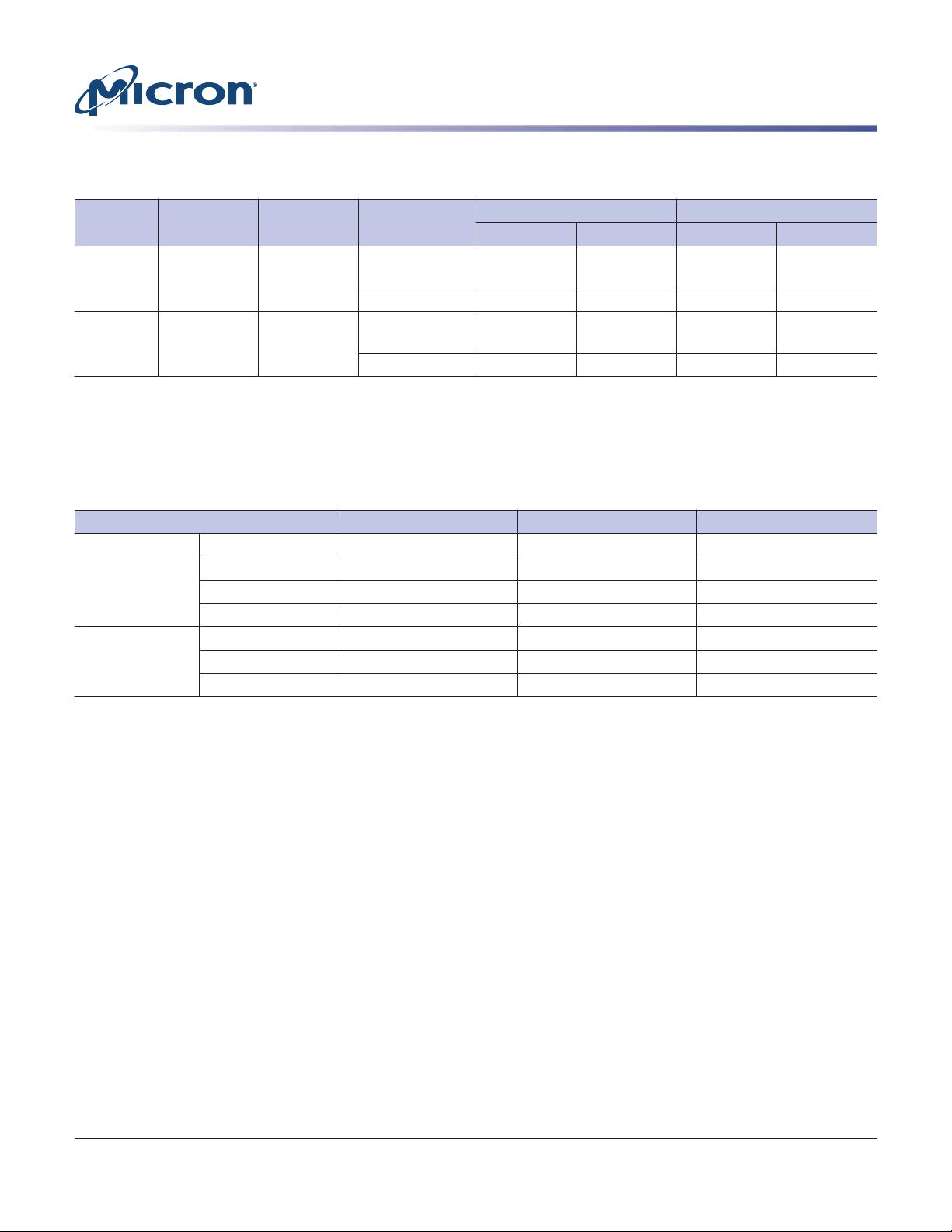

Table 1: Key Timing Parameters

Speed

Grade

Clock Rate

(MHz)

Data Rate

(Mb/s/pin)

Array

Configuration

WRITE Latency READ Latency

Set A Set B DBI Disabled DBI Enabled

-046 2133 4266 512 Meg × 32,

1 Giga × 32

18 34 36 40

2 Giga × 32 18 34 40 44

-053 1866 3733 512 Meg × 32,

1 Giga × 32

16 30 32 36

2 Giga × 32 16 30 36 40

SDRAM Addressing

The table below shows 8Gb single channel die configuration used in the package.

Table 2: Device Configuration

512M32 (16Gb/Package) 1G32 (32Gb/Package) 2G32 (64Gb/Package)

2

Die configuration Channel A, Rank 0 ×16 mode × 1 die ×16 mode × 1 die ×8 mode × 2 dies

Channel A, Rank 1 – ×16 mode × 1 die ×8 mode × 2 dies

Channel B, Rank 0 ×16 mode × 1 die ×16 mode × 1 die ×8 mode × 2 dies

Channel B, Rank 1 – ×16 mode × 1 die ×8 mode × 2 dies

Die addressing Bank address BA[2:0] BA[2:0] BA[2:0]

Row addresses R[15:0] R[15:0] R[16:0]

Column addresses C[9:0] C[9:0] C[9:0]

Notes:

1. Refer to Package Block Diagrams section and Monolithic Device Addressing section.

2. Refer to Byte Mode section for further information about 2G32 (64Gb) configuration.

Micron Confidential and Proprietary Preliminary

200b: x32 LPDDR4X SDRAM

Introduction

CCM005-554574167-10510

200b_j_z11n_ddp_qdp_8dp_lpddr4x.pdf – Rev. C 11/17 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2017 Micron Technology, Inc. All rights reserved.

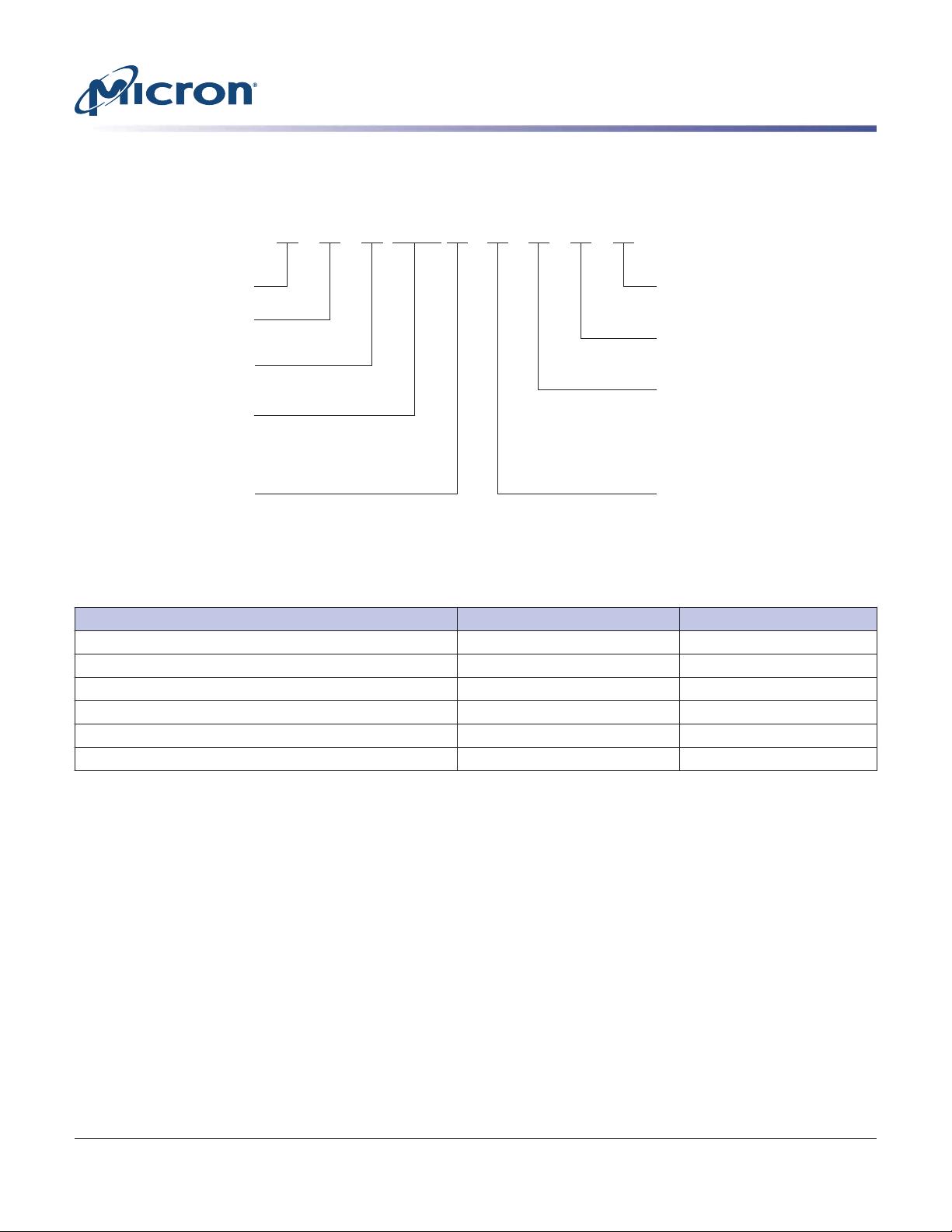

Part Number Ordering Information

Figure 1: Part Number Chart

MT 53 E 512M32 D2 NP -046 WT :E

Micron Technology

Product Family

53 = Mobile LPDDR4 SDRAM

Operating Voltage

E = 1.1V V

DD2

/ 0.6V and 1.1V V

DDQ

Configuration

512M32 = 512 Meg x 32

Design Revision

:E = Fifth generation

Operating Temperature

WT = –25°C to +85°C

Cycle Time

1G32 = 1 Giga x 32

2G32 = 2 Giga x 32

Addressing

D2 = LPDDR4, 2 die

D4 = LPDDR4, 4 die

D8 = LPDDR4, 8 die

Package Codes

NP = 200-ball WFBGA

NQ/QD = 200-ball VFBGA

-046 = 467ps,

t

CK

RL = 36/40 (Normal latency)

RL = 40/44 (Byte mode latency)

-053 = 535ps,

t

CK

RL = 32/36 (Normal latency)

RL = 36/40 (Byte mode latency)

Table 3: Part Number List

Part Number Total Density Data Rate

MT53E512M32D2NP-046 WT:E 2GB (16Gb) 4266 Mbps/pin

MT53E512M32D2NP-053 WT:E 2GB (16Gb) 3733 Mbps/pin

MT53E1G32D4NQ-046 WT:E 4GB (32Gb) 4266 Mbps/pin

MT53E1G32D4NQ-053 WT:E 4GB (32Gb) 3733 Mbps/pin

MT53E2G32D8QD-046 WT:E 8GB (64Gb) 4266 Mbps/pin

MT53E2G32D8QD-053 WT:E 8GB (64Gb) 3733 Mbps/pin

FBGA Part Marking Decoder

Due to space limitations, FBGA-packaged components have an abbreviated part marking that is different from the

part number. Micron’s FBGA part marking decoder is available at www.micron.com/decoder.

Micron Confidential and Proprietary Preliminary

200b: x32 LPDDR4X SDRAM

Introduction

CCM005-554574167-10510

200b_j_z11n_ddp_qdp_8dp_lpddr4x.pdf – Rev. C 11/17 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2017 Micron Technology, Inc. All rights reserved.

Contents

General Description ....................................................................................................................................... 17

General Notes ............................................................................................................................................ 17

Package Block Diagrams ................................................................................................................................. 18

Ball Assignments and Descriptions ................................................................................................................. 21

Package Dimensions ....................................................................................................................................... 24

MR0, MR[6:5], MR8, MR13, MR24 Definition ................................................................................................... 27

I

DD

Parameters ............................................................................................................................................... 28

Functional Description ................................................................................................................................... 30

Monolithic Device Addressing ......................................................................................................................... 30

Simplified Bus Interface State Diagram ............................................................................................................ 33

Power-Up and Initialization ............................................................................................................................ 34

Voltage Ramp ............................................................................................................................................. 35

Reset Initialization with Stable Power .......................................................................................................... 37

Power-Off Sequence ....................................................................................................................................... 38

Controlled Power-Off .................................................................................................................................. 38

Uncontrolled Power-Off .............................................................................................................................. 38

Mode Registers ............................................................................................................................................... 39

Mode Register Assignments and Definitions ................................................................................................ 39

Commands and Timing .................................................................................................................................. 65

Truth Tables ................................................................................................................................................... 65

ACTIVATE Command ..................................................................................................................................... 67

Read and Write Access Modes ......................................................................................................................... 69

Preamble and Postamble ................................................................................................................................ 69

Burst READ Operation .................................................................................................................................... 73

Read Timing ............................................................................................................................................... 75

t

LZ(DQS),

t

LZ(DQ),

t

HZ(DQS),

t

HZ(DQ) Calculation ..................................................................................... 75

t

LZ(DQS) and

t

HZ(DQS) Calculation for ATE (Automatic Test Equipment) .................................................... 76

t

LZ(DQ) and

t

HZ(DQ) Calculation for ATE (Automatic Test Equipment) ........................................................ 77

Burst WRITE Operation .................................................................................................................................. 79

Write Timing .............................................................................................................................................. 82

t

WPRE Calculation for ATE (Automatic Test Equipment) .............................................................................. 83

t

WPST Calculation for ATE (Automatic Test Equipment) ............................................................................... 83

MASK WRITE Operation ................................................................................................................................. 84

Mask Write Timing Constraints for BL16 ...................................................................................................... 86

Data Mask and Data Bus Inversion (DBI [DC]) Function ................................................................................... 88

WRITE and MASKED WRITE Operation DQS Control (WDQS Control) ............................................................. 92

WDQS Control Mode 1 – Read-Based Control .............................................................................................. 92

WDQS Control Mode 2 – WDQS_On/Off ...................................................................................................... 92

Preamble and Postamble Behavior .................................................................................................................. 96

Preamble, Postamble Behavior in READ-to-READ Operations ...................................................................... 96

READ-to-READ Operations – Seamless ........................................................................................................ 97

READ-to-READ Operations – Consecutive ................................................................................................... 98

WRITE-to-WRITE Operations – Seamless ................................................................................................... 105

WRITE-to-WRITE Operations – Consecutive ............................................................................................... 108

PRECHARGE Operation ................................................................................................................................. 112

Burst READ Operation Followed by Precharge ............................................................................................ 112

Burst WRITE Followed by Precharge ........................................................................................................... 113

Auto Precharge .............................................................................................................................................. 114

Burst READ With Auto Precharge ............................................................................................................... 114

Burst WRITE With Auto Precharge .............................................................................................................. 115

Micron Confidential and Proprietary Preliminary

200b: x32 LPDDR4X SDRAM

Introduction

CCM005-554574167-10510

200b_j_z11n_ddp_qdp_8dp_lpddr4x.pdf – Rev. C 11/17 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2017 Micron Technology, Inc. All rights reserved.

RAS Lock Function .................................................................................................................................... 119

Delay Time From WRITE-to-READ with Auto Precharge .............................................................................. 120

REFRESH Command ..................................................................................................................................... 121

Burst READ Operation Followed by Per Bank Refresh .................................................................................. 127

Refresh Requirement ..................................................................................................................................... 128

SELF REFRESH Operation .............................................................................................................................. 129

Self Refresh Entry and Exit ......................................................................................................................... 129

Power-Down Entry and Exit During Self Refresh ......................................................................................... 130

Command Input Timing After Power-Down Exit ......................................................................................... 131

Self Refresh Abort ...................................................................................................................................... 132

MRR, MRW, MPC Commands During

t

XSR,

t

RFC ........................................................................................ 132

Power-Down Mode ........................................................................................................................................ 135

Power-Down Entry and Exit ....................................................................................................................... 135

Input Clock Stop and Frequency Change ........................................................................................................ 145

Clock Frequency Change – CKE LOW ......................................................................................................... 145

Clock Stop – CKE LOW ............................................................................................................................... 145

Clock Frequency Change – CKE HIGH ........................................................................................................ 145

Clock Stop – CKE HIGH ............................................................................................................................. 146

MODE REGISTER READ Operation ................................................................................................................ 147

MRR After a READ and WRITE Command .................................................................................................. 148

MRR After Power-Down Exit ...................................................................................................................... 150

MODE REGISTER WRITE ............................................................................................................................... 151

Mode Register Write States ......................................................................................................................... 152

V

REF

Current Generator (VRCG) ..................................................................................................................... 153

V

REF

Training ................................................................................................................................................. 155

V

REF(CA)

Training ........................................................................................................................................ 155

V

REF(DQ)

Training ....................................................................................................................................... 160

Command Bus Training ................................................................................................................................. 165

Command Bus Training Mode .................................................................................................................... 165

Training Sequence for Single-Rank Systems ................................................................................................ 166

Training Sequence for Multiple-Rank Systems ............................................................................................ 167

Relation Between CA Input Pin and DQ Output Pin ..................................................................................... 168

Write Leveling ............................................................................................................................................... 172

Mode Register Write-WR Leveling Mode ..................................................................................................... 172

Write Leveling Procedure ........................................................................................................................... 172

Input Clock Frequency Stop and Change .................................................................................................... 173

MULTIPURPOSE Operation ........................................................................................................................... 176

Read DQ Calibration Training ........................................................................................................................ 181

Read DQ Calibration Training Procedure .................................................................................................... 181

Read DQ Calibration Training Example ...................................................................................................... 183

MPC[READ DQ CALIBRATION] After Power-Down Exit ............................................................................... 184

Write Training ............................................................................................................................................... 184

Internal Interval Timer .............................................................................................................................. 190

DQS Interval Oscillator Matching Error ...................................................................................................... 192

OSC Count Readout Time .......................................................................................................................... 193

Thermal Offset .............................................................................................................................................. 195

Temperature Sensor ...................................................................................................................................... 195

ZQ Calibration ............................................................................................................................................... 196

ZQCAL Reset ............................................................................................................................................. 197

Multichannel Considerations ..................................................................................................................... 198

ZQ External Resistor, Tolerance, and Capacitive Loading ............................................................................. 199

Frequency Set Points ..................................................................................................................................... 200

Micron Confidential and Proprietary Preliminary

200b: x32 LPDDR4X SDRAM

Introduction

CCM005-554574167-10510

200b_j_z11n_ddp_qdp_8dp_lpddr4x.pdf – Rev. C 11/17 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2017 Micron Technology, Inc. All rights reserved.

剩余304页未读,继续阅读

qq_39844434

- 粉丝: 2

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- stc12c5a60s2 例程

- Android通过全局变量传递数据

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0