没有合适的资源?快使用搜索试试~ 我知道了~

首页Apollo3_MCU_Data_Sheet_v0_6_open.pdf

Apollo3_MCU_Data_Sheet_v0_6_open.pdf

需积分: 46 17 下载量 87 浏览量

更新于2023-03-03

评论

收藏 7.85MB PDF 举报

Apollo3 MCU datasheet!Apollo3 MCU datasheet!Apollo3 MCU datasheet!

资源详情

资源评论

资源推荐

Apollo3 Blue Datasheet

DS-A3-0p6 Page 1 of 879 2018 Ambiq Micro, Inc.

All rights reserved.

Apollo3 Datasheet

Doc. ID: DS-A3-0p6

Revision 0.6

March 2018

IMPORTANT NOTICE:

This datasheet is released under NDA only. Content herein is

accurate to the extent possible, but is preliminary and certain

content may not be fully validated.

Apollo3 Blue Datasheet

Ultra-Low Power MCU Family

DS-A3-0p6 Page 2 of 879 2018 Ambiq Micro, Inc.

All rights reserved.

Ambiq Micro

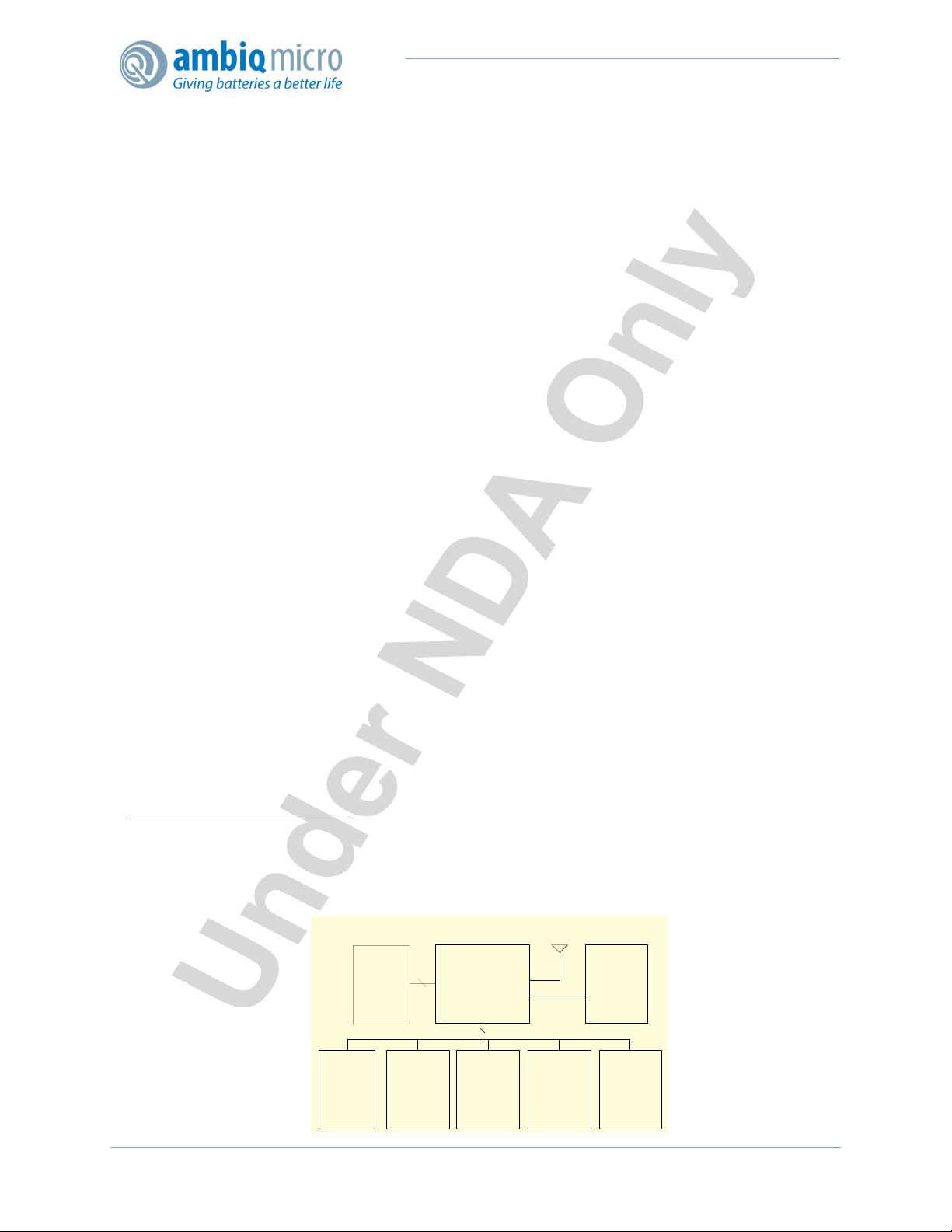

Apollo3

MCU

Host

Processor

(optional)

SPI/I

2

C

Slave

Port

SPI/I

2

C Master,

UART

GPS / WiFi

Magnetometer

with Digital

Output

Gyroscope

with Digital

Output

Accelerometer

with Digital

Output

Typical Application Circuit for the Apollo3 MCU

External Flash

Multi-bit

SPI

Display

Features

Ultra-low supply current:

- 6 µA/MHz executing from flash at 3.3 V

- 6 µA/MHz executing from RAM at 3.3 V

- 1 µA deep sleep mode (BLE Off) with RTC at 3.3 V

High-performance ARM Cortex-M4Processor

- 48 MHz nominal clock frequency, with 96 MHz high perfor-

mance Burst Mode

- Floating point unit

- Memory protection unit

- Wake-up interrupt controller with 32 interrupts

Integrated Bluetooth

1

5 low-energy module

- RF sensitivity: -95 dBm

- TX: 3 mA @ 0 dBm, RX: 3 mA

- Tx output power: -20 dBm to +4 dBm

Ultra-low power memory:

- Up to 1 MB of flash memory for code/data

- Up to 384 KB of low leakage RAM for code/data

- 16 kB 2-way Associative/Direct-Mapped Cache

Ultra-low power interface for off-chip sensors:

- 14 bit ADC at up to 1.2 MS/s, 15 selectable input channels

available

- Voltage Comparator

- Temperature sensor with +/-3ºCaccuracy

ISO7816 Secure interface

Flexible serial peripherals:

- 1x 2/4/8-bit SPI master interface

-6x I

2

C/SPI masters for peripheral communication

-I

2

C/SPI slave for host communications

- 2x UART modules with 32-location Tx and Rx FIFOs

- PDM for mono and stereo audio microphone

-1x I

2

S slave for PDM audio pass-through

Rich set of clock sources:

- 32.768 kHz XTAL oscillator

- Low frequency RC oscillator – 1.024 kHz

- High frequency RC oscillator – 48/96 MHz

- RTC based on Ambiq’s AM08X5/18X5 families

Wide operating range: 1.755-3.63 V, –40 to 85°C

1. The Bluetooth® word mark and logos are registered trade-

marks owned by the Bluetooth SIG, Inc. and any use of such

marks is under license. Other trademarks and trade names

are those of their respective owners.

Compact package option:

- 3.37 x 3.25 mm(0.35mm) 65-pin CSP with 37 GPIO

- 5 x 5 mm (0.5mm) 81-pin BGA with 50 GPIO

Applications

Description

The Apollo3 MCU Family is an ultra-low power, highly integrated

microcontroller designed for battery-powered devices including

wearable electronics, activity & fitness monitors, and wireless

sensors. By combining ultra-low power sensor conversion

electronics with the powerful ARM Cortex-M4 processor with

Floating Point Unit, the Apollo3 Blue MCU enables complex

sensor processing tasks to be completed with unprecedented

battery life. Weeks, months, and years of battery life are

achievable while doing complex context detection, gesture

recognition, and activity monitoring. The Apollo3 Blue MCU takes

full advantage of Ambiq Micro’s patented Subthreshold Power

Optimized Technology (SPOT) Platform, setting a new industry

benchmark in low power design.

The Apollo3 Blue MCU builds upon the industry’s best power

management efficiency of the Apollo2 MCU Family to deliver a

totally integrated Bluetooth low energy connectivity solution. The

device offers Bluetooth 5 ready radio and integrates 1 MB of flash

memory and 384 KB of RAM to accommodate radio and sensor

overhead while leaving space for application code. This

microcontroller also includes several masters and one slave SPI

and I2C ports and two UART ports for communicating with sensors

including accelerometers, gyroscopes, and magnetometers. .

- Wearable electronics

including smart watches

- Motion and tracking devices

- Wireless sensors - Home automation

- Activity and fitness moni-

tors

- Light control applications

- Consumer electronics - Wireless mice and keyboards

- Beacons - Alarms and security system

- Remote sensing - Toys

Apollo3 Blue Datasheet

DS-A3-0p6 Page 3 of 879 2018 Ambiq Micro, Inc.

All rights reserved.

Table of Content

1. Apollo3 Blue MCU Package Pins ..................................................................................... 47

1.1 Pin Configuration ....................................................................................................... 47

1.2 Pin Connections ......................................................................................................... 48

2. System Core ....................................................................................................................... 66

3. MCU Core Details ............................................................................................................. 68

3.1 Interrupts .................................................................................................................... 68

3.2 Memory Map ............................................................................................................. 71

3.3 Memory Protection Unit (MPU) ................................................................................ 73

3.4 System Busses ............................................................................................................ 73

3.5 Power Management ................................................................................................... 74

3.5.1 Cortex-M4 Power Modes .................................................................................. 74

3.5.2 System Power Modes ........................................................................................ 75

3.5.3 Power Control ................................................................................................... 77

3.6 Debug Interfaces ........................................................................................................ 87

3.6.1 Debugger Attachment ....................................................................................... 87

3.6.2 Instrumentation Trace Macrocell (ITM) ........................................................... 87

3.6.3 Trace Port Interface Unit (TPIU) ...................................................................... 87

3.6.4 Faulting Address Trapping Hardware ............................................................... 87

3.7 ITM Registers ............................................................................................................ 87

3.7.1 Register Memory Map ...................................................................................... 88

3.7.2 ITM Registers ................................................................................................... 90

3.8 MCUCTRL Registers .............................................................................................. 115

3.8.1 Register Memory Map .................................................................................... 116

3.8.2 MCUCTRL Registers ..................................................................................... 118

3.9 Memory Subsystem ................................................................................................. 141

3.9.1 Features ........................................................................................................... 142

3.9.2 Functional Overview ....................................................................................... 143

3.9.3 Flash Cache ..................................................................................................... 144

3.9.4 SRAM Interface .............................................................................................. 158

4. Security ............................................................................................................................ 160

4.1 Functional Overview ................................................................................................ 160

4.2 Secure Boot .............................................................................................................. 160

4.3 Secure OTA ............................................................................................................. 161

4.4 Secure Key Storage .................................................................................................. 161

4.5 External Flash Inline Encrypt/Decrypt .................................................................... 161

4.6 SECURITY Registers .............................................................................................. 162

4.6.1 Register Memory Map .................................................................................... 162

4.6.2 SECURITY Registers ..................................................................................... 163

4.7 ................................................................................................................................. 168

5. DMA ................................................................................................................................ 169

5.1 Functional Overview ................................................................................................ 169

5.1.1 General Usage ................................................................................................. 169

5.1.2 Auto Power Down .......................................................................................... 170

5.1.3 Priority ............................................................................................................ 170

Apollo3 Blue Datasheet

DS-A3-0p6 Page 4 of 879 2018 Ambiq Micro, Inc.

All rights reserved.

5.1.4 Hardware Handshake / Hardware Triggering ................................................. 170

6. BLE Module .................................................................................................................... 171

6.1 Functional Overview ................................................................................................ 171

6.1.1 Introduction ..................................................................................................... 171

6.1.2 Main Features ................................................................................................. 171

6.2 Functional Description ............................................................................................. 172

6.2.1 Data Transfers ................................................................................................. 172

6.3 BLEIF Registers ...................................................................................................... 173

6.4 BLEIF Registers ...................................................................................................... 173

6.4.1 Register Memory Map .................................................................................... 174

6.4.2 BLEIF Registers ............................................................................................. 176

7. MSPI Master Module ....................................................................................................... 209

7.1 Functional Overview ................................................................................................ 209

7.2 Configuration ........................................................................................................... 210

7.3 PIO Operations ........................................................................................................ 210

7.3.1 Paired-Quad Device Operation (QUADCMD) ............................................... 211

7.4 DMA Operations ...................................................................................................... 212

7.5 Execute in Place (XIP) Operations .......................................................................... 213

7.5.1 Optimized XIP Addressing ............................................................................ 213

7.5.2 Micron XIP Support ........................................................................................ 213

7.6 Command Queueing (CQ) ....................................................................................... 214

7.6.1 Command Queue Data Format ....................................................................... 214

7.6.2 CQ Interrupts .................................................................................................. 215

7.6.3 Pausing CQ Operations ................................................................................... 215

7.6.4 Using the CQ Index registers .......................................................................... 217

7.6.5 MSPI and IOM Intercommunication .............................................................. 217

7.7 Data Scrambling ...................................................................................................... 218

7.8 Auto Power Down ................................................................................................... 218

7.9 Pad Configuration and Enables ................................................................................ 218

7.9.1 Internal Pin Muxing Options ......................................................................... 219

7.9.2 MSPI Pin Timing Board/Package Considerations .......................................... 219

7.10 MSPI Registers ...................................................................................................... 220

7.10.1 Register Memory Map .................................................................................. 221

7.10.2 MSPI Registers ............................................................................................. 222

8. I2C/SPI Master Module ................................................................................................... 250

8.1 Functional Overview ................................................................................................ 250

8.2 Interface Clock Generation ...................................................................................... 250

8.3 Command Operation ................................................................................................ 251

8.4 FIFO ......................................................................................................................... 253

8.5 I2C Interface ............................................................................................................ 253

8.5.1 Bus Not Busy .................................................................................................. 254

8.5.2 Start Data Transfer .......................................................................................... 254

8.5.3 Stop Data Transfer .......................................................................................... 254

8.5.4 Data Valid ....................................................................................................... 254

8.5.5 Acknowledge .................................................................................................. 254

8.5.6 I2C Slave Addressing ..................................................................................... 255

Apollo3 Blue Datasheet

DS-A3-0p6 Page 5 of 879 2018 Ambiq Micro, Inc.

All rights reserved.

8.5.7 I2C Offset Address Transmission ................................................................... 255

8.5.8 I2C Normal Write Operation .......................................................................... 256

8.5.9 I2C Normal Read Operation ........................................................................... 256

8.5.10 I2C Raw Write Operation ............................................................................. 257

8.5.11 I2C Raw Read Operation .............................................................................. 257

8.5.12 Holding the Interface with CONT ................................................................ 257

8.5.13 I2C Multi-master Arbitration ........................................................................ 257

8.6 SPI Operations ......................................................................................................... 258

8.6.1 SPI Configuration ........................................................................................... 258

8.6.2 SPI Slave Addressing ...................................................................................... 258

8.6.3 SPI Normal Write ........................................................................................... 258

8.6.4 SPI Normal Read ............................................................................................ 259

8.6.5 SPI Raw Write ................................................................................................ 259

8.6.6 SPI Raw Read ................................................................................................. 260

8.6.7 SPI 3-wire Mode ............................................................................................. 260

8.6.8 Complex SPI Operations ................................................................................ 260

8.6.9 SPI Polarity and Phase .................................................................................... 261

8.7 Repeating a Command ............................................................................................. 261

8.8 Bit Orientation ......................................................................................................... 262

8.9 Full Duplex Operations ............................................................................................ 262

8.10 SPI Flow Control ................................................................................................... 262

8.11 Pre-read Control ..................................................................................................... 264

8.12 Minimizing Power ................................................................................................. 265

8.13 IOM Registers ........................................................................................................ 265

8.13.1 Register Memory Map .................................................................................. 266

8.13.2 IOM Registers ............................................................................................... 271

9. I2C/SPI Slave Module ..................................................................................................... 308

9.1 Functional Overview ................................................................................................ 308

9.2 Local RAM Allocation ............................................................................................ 308

9.3 Direct Area Functions .............................................................................................. 309

9.4 FIFO Area Functions ............................................................................................... 312

9.5 Rearranging the FIFO .............................................................................................. 313

9.6 Interface Interrupts ................................................................................................... 314

9.7 Command Completion Interrupts ............................................................................ 315

9.8 Host Address Space and Registers ........................................................................... 315

9.9 I2C Interface ............................................................................................................ 315

9.9.1 Bus Not Busy .................................................................................................. 316

9.9.2 Start Data Transfer .......................................................................................... 316

9.9.3 Stop Data Transfer .......................................................................................... 316

9.9.4 Data Valid ....................................................................................................... 316

9.9.5 Acknowledge .................................................................................................. 316

9.9.6 Address Operation .......................................................................................... 317

9.9.7 Offset Address Transmission .......................................................................... 317

9.9.8 Write Operation .............................................................................................. 318

9.9.9 Read Operation ............................................................................................... 318

9.9.10 General Address Detection ........................................................................... 319

剩余878页未读,继续阅读

richardwu7809

- 粉丝: 0

- 资源: 4

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0