TMS320F28335中文数据手册:DSP开发速查

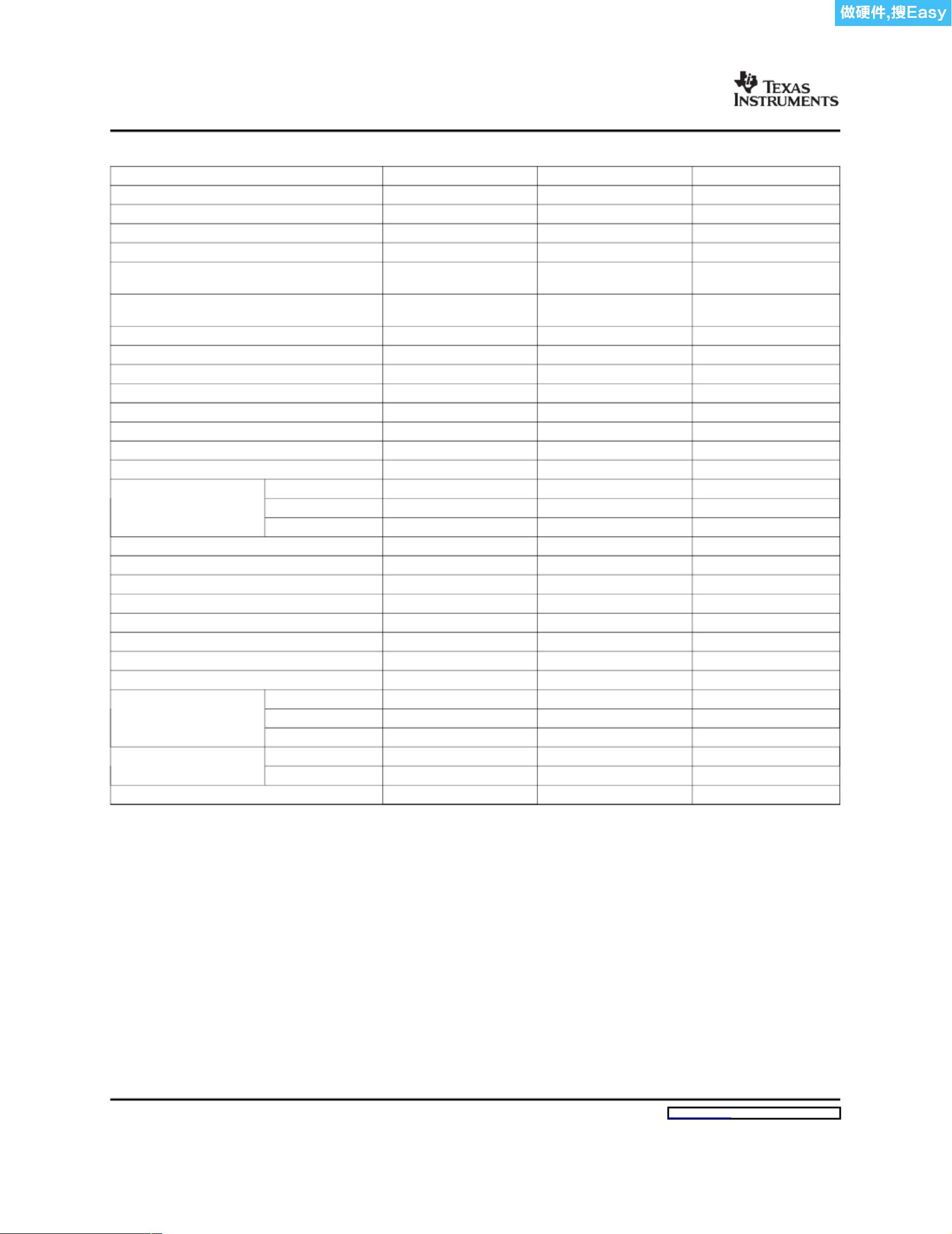

TMS320F28335中文数据手册是一份详细的文档,专门针对TI公司生产的数字信号控制器(DSC)系列,包括TMS320F28335、TMS320F28334和TMS320F28332,以及与其类似型号如TMS320F28235、TMS320F28234和TMS320F28232。该手册提供了这些器件的深入介绍,旨在帮助工程师在产品开发早期阶段了解其特性,并加速研发过程。

手册的核心内容包括:

1. **修订历史**:记录了手册版本的更新情况,以便跟踪重要更改。

2. **产品特点**:介绍了TMS320F2833x系列的主要功能和优势,如高速处理能力、高级内存架构等。

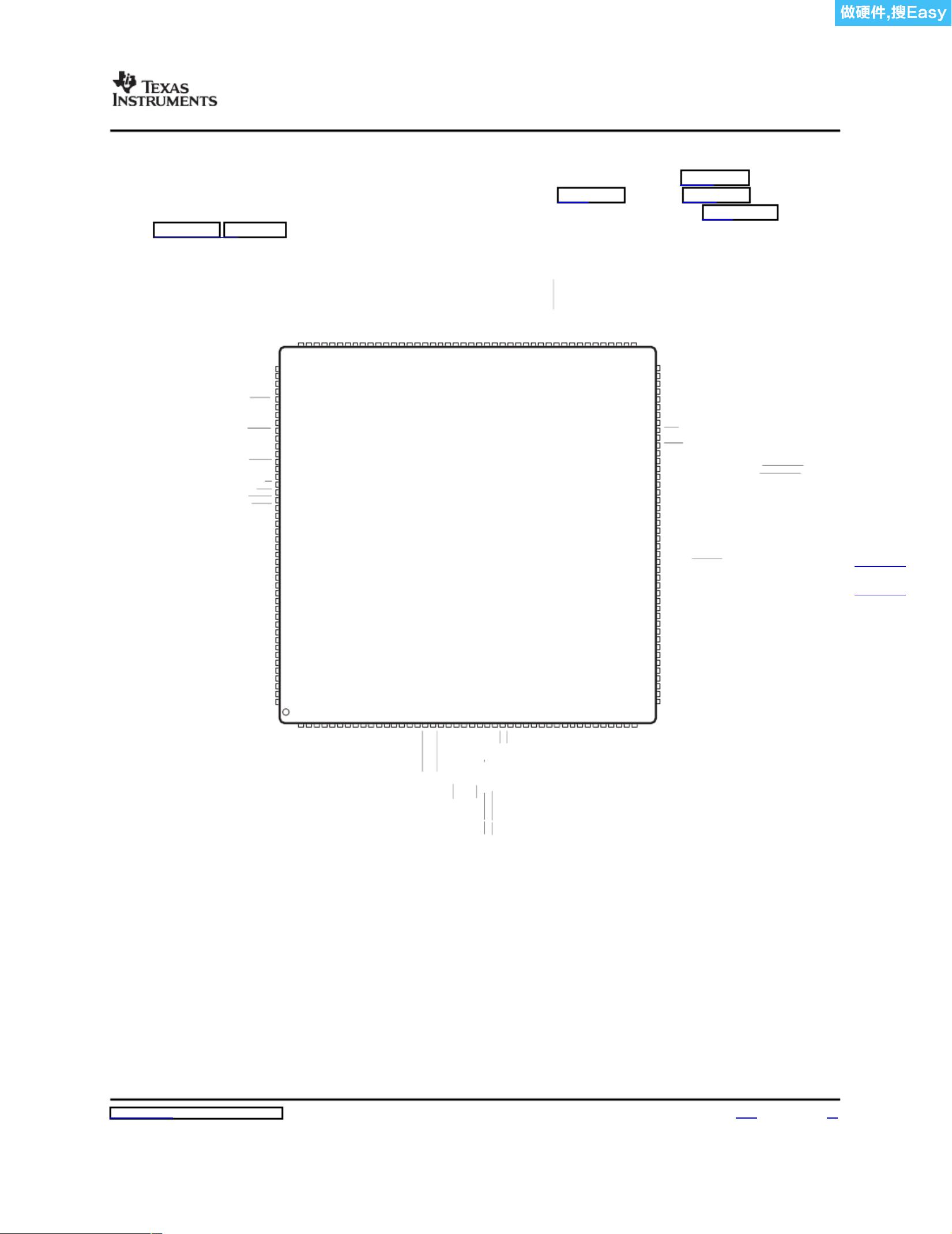

3. **引脚分配**:详细说明了各个引脚的功能和连接定义,对于硬件设计至关重要。

4. **信号说明**:阐述了各种内部和外部信号的作用,有助于理解和配置信号路径。

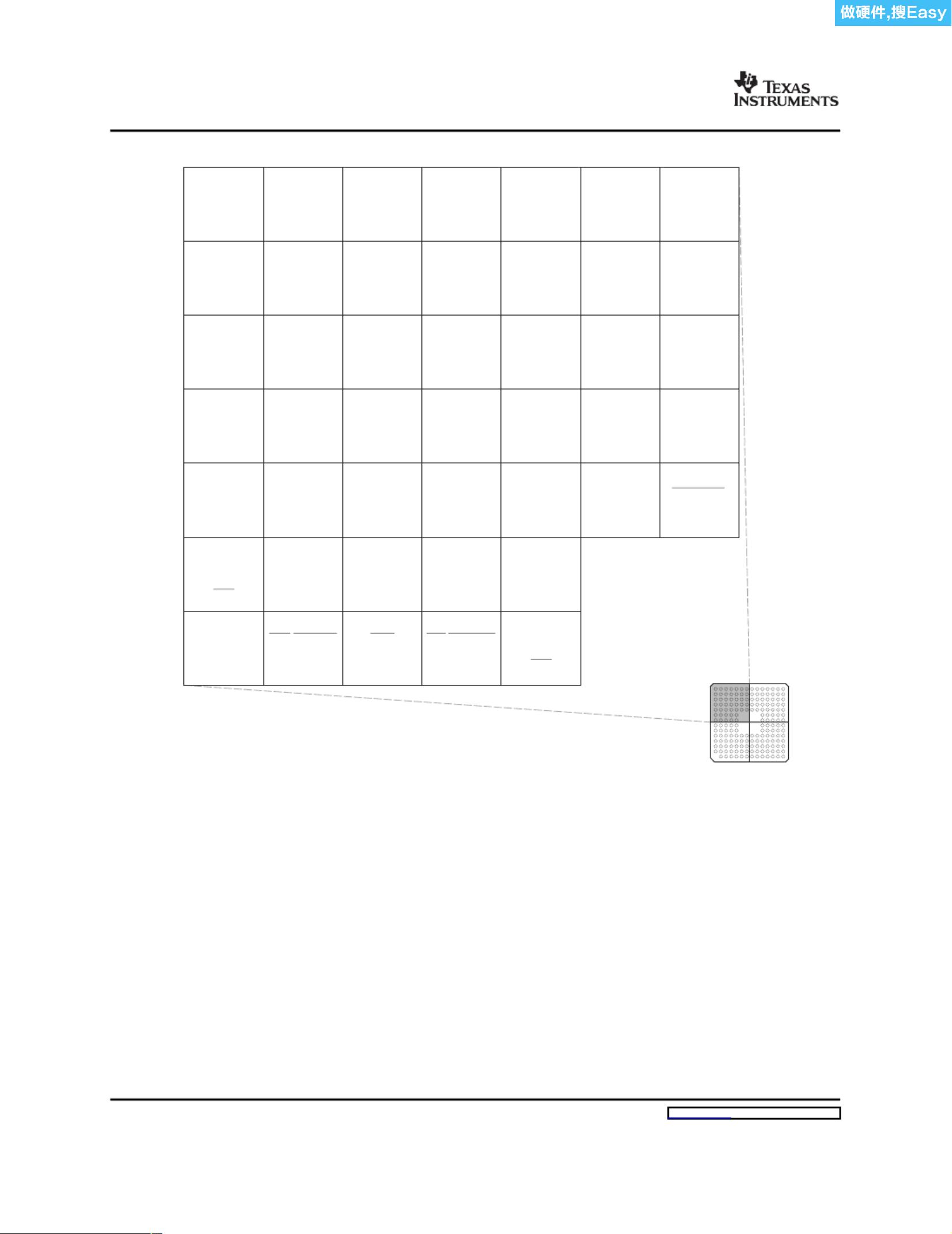

5. **存储器映射图**:展示了处理器内部存储器的布局,便于理解数据存取机制。

6. **C28x CPU**:讲解了中央处理器的基本架构和特性。

7. **内存总线和哈佛总线结构**:解释了数据和指令的传输方式,优化了数据访问性能。

8. **外设总线**:涉及了与外设通信的接口,如实时JTAG与分析、GPIO多路复用器等。

9. **实时中断管理**:涵盖了外设中断扩展、外部中断和看门狗功能,强调了中断处理的重要性。

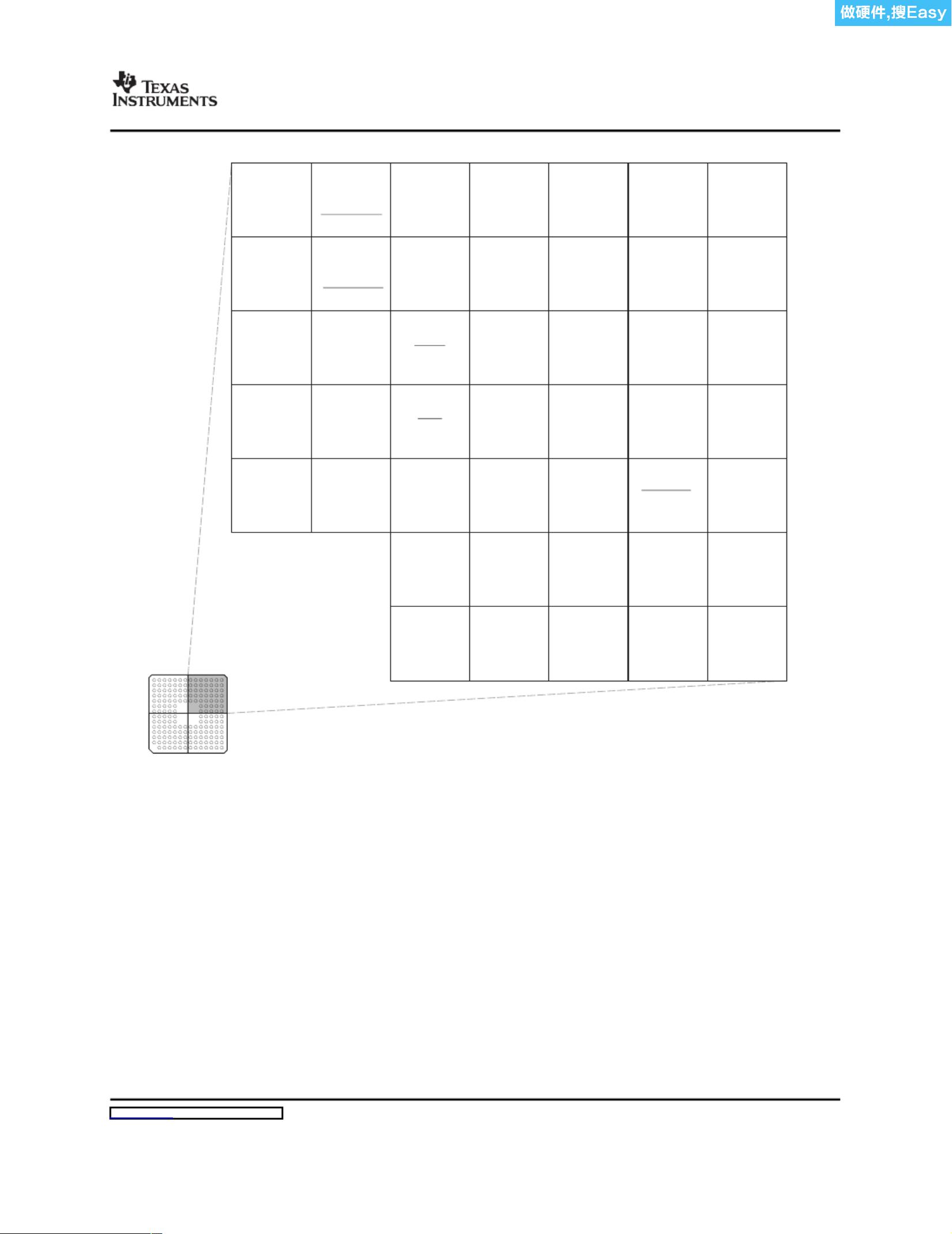

10. **振荡器和PLL**:描述了时钟系统,确保系统的稳定性和精度。

11. **低功耗模式**:讨论了不同电源管理模式,适用于能源效率要求高的应用。

12. **外设帧**:PFNs控制了设备间的同步,用于实现高效数据交换。

13. **系统控制**:涵盖了系统启动、复位、安全机制等核心控制系统管理。

14. **OSC和PLL模块**:重点介绍了晶振和锁相环的设置和调整方法。

通过这份中文数据手册,用户能够快速掌握TMS320F28335的设计要点,缩短产品开发周期,提高产品质量。值得注意的是,手册中提到的产品特性、规格可能会随着产品的改进而有所变更,因此,在实际应用中需确保参考最新版本的信息。

942 浏览量

4488 浏览量

2710 浏览量

153 浏览量

456 浏览量

1500 浏览量

180 浏览量

301 浏览量

1474 浏览量

qq_26523309

- 粉丝: 1

- 资源: 1

最新资源

- 西瓜答题工具利用OCR识别题目并快速搜索答案计算选项权重

- df-api-docs:直接货运服务的公共API

- TA-Report-DOC

- android一款简约导航控件

- drymail:使发送电子邮件变得简单而 DRY — 对于 Python 3

- Vangala:这是Vangala家庭的详细信息

- jsp+ssm+mysql实现的零食商城系统源码+数据库文件+项目开发文档(60+页)

- programming-with-data::snake: 从头开始学习 Python 和 Pandas

- daniellivingston:

- com.osram.lightify.zigbee

- HL-project

- SiteBootstrapSimples

- 减速器轴的危险截面计算.rar

- CIMarchHackathon

- THREEp.js:three.js插件,可生成几乎无限的带有极坐标球坐标函数的时变几何形状的缓冲区几何形状

- phantom:带有 Bootstrap 的 Jekyll 的极简、响应式投资组合主题