没有合适的资源?快使用搜索试试~ 我知道了~

首页Cadence SigXplorer 中兴 仿真 教程

Cadence SigXplorer 中兴 仿真 教程

找了好久才找到, 对初学Cadence仿真非常有用,我就是从这个入门的.

资源详情

资源评论

资源推荐

目录

前 言.............................................................................................................................................................................3

第一章 高速设计与 PCB 仿真流程 ...........................................................................................................................4

1.1 高速信号与高速设计 ..................................................................................................................................... 4

1.1.1

高速信号的确定

........................................................................................................................................

5

1.1.2

边缘速率引发高速问题

............................................................................................................................

5

1.1.3

传输线效应

................................................................................................................................................

6

1.2 高速 PCB 仿真的重要意义 ............................................................................................................................ 9

1.2.1

板级

SI

仿真的重要意义

...........................................................................................................................

9

1.2.2

系统级

SI

仿真的重要意义

...................................................................................................................

10

1.3 高速 PCB 仿真设计基本流程 .................................................................................................................... 12

1.3.1 PCB

仿真设计的一般流程:

.................................................................................................................

12

1.3.2

基于

CADENCE Allegro

工具的板极仿真设计的流程

.......................................................................

13

第二章 仿真设置 .........................................................................................................................................................16

2.1 打开 BRD 文件 ............................................................................................................................................... 16

2.2 调用并运行设置向导 ..................................................................................................................................... 17

2.2.1

编辑叠层参数和线宽以适应信号线阻抗

................................................................................................19

2.2.2

输入

DC

网络电平

....................................................................................................................................22

2.2.3

分立器件和插座器件的标号归类设置

....................................................................................................23

2.2.4

器件赋上相应的模型

................................................................................................................................24

2.2.5

使用

SI Audit

进行核查

............................................................................................................................32

2.3 设置 IO 管脚的测试条件和逻辑门限值 ....................................................................................................... 32

2.4 差分驱动器的设置 ......................................................................................................................................... 34

2.5 仿真分析参数设置 ......................................................................................................................................... 36

第三章 提取和建立拓朴进行仿真 .............................................................................................................................45

3.1 自动提取拓扑 ................................................................................................................................................. 45

3.1.1

通过

Signal Analysis

提取拓朴

.................................................................................................................46

3.1.2

在

PCB SI

的

Constraint Manager

中抽取拓扑

........................................................................................47

第 1 页 共 116 页

《EDA 工具手册》仿真分册 EDA 平台

3.2 改变 SIGXPLORER 中的电路参数................................................................................................................... 49

3.3 SIGXPLORER 中的仿真参数设置:................................................................................................................. 51

3.4 SIGXPLORER 中的仿真过程:......................................................................................................................... 54

3.5 SIGWAV E 的使用简介 ...................................................................................................................................... 59

3.6 手工建立和调整拓扑 ..................................................................................................................................... 61

3.6.1

手工建立和调整拓朴的作用

....................................................................................................................61

3.6.2

手工建立和调整拓朴的过程

....................................................................................................................61

3.7 仿真不同的参数值 ......................................................................................................................................... 65

第四章 时序仿真 .........................................................................................................................................................68

4.1 时序(TIMING)的一些参数 ............................................................................................................................ 68

4.2 传统的时钟同步系统仿真的过程.................................................................................................................. 72

4.2.1

共同时钟同步系统的时序计算

................................................................................................................72

4.2.2

共同时钟同步系统的仿真过程

................................................................................................................73

4.3 源同步接口仿真过程 ..................................................................................................................................... 79

4.3.1

源同步时序公式

........................................................................................................................................79

4.3.2

源同步时序仿真过程

................................................................................................................................81

4.4 时钟信号的说明 ............................................................................................................................................. 83

第五章 设置约束及赋予 PCB....................................................................................................................................85

5.1 启动约束条件设置界面.................................................................................................................................. 85

5.2 加约束的步骤 ................................................................................................................................................. 86

5.3 各个约束标签栏的作用.................................................................................................................................. 86

5.4 将约束加到 PCB 文件上 ................................................................................................................................ 91

第六章 后仿真过程及参数设置 .................................................................................................................................93

6.1 后仿真前的几个准备步骤.............................................................................................................................. 93

6.2 针对目的一的后仿真 ..................................................................................................................................... 93

第 2 页 共 116 页

《EDA 工具手册》仿真分册 EDA 平台

6.3 针对目的二的后仿真 ..................................................................................................................................... 94

6.3.1

进行仿真设置

............................................................................................................................................95

6.3.2

进行反射仿真验证

....................................................................................................................................97

第七章 点到多点的仿真和多板间仿真 ................................................................................................................... 100

7.1 点到多点的拓扑仿真 ................................................................................................................................... 100

7.2 多板间的仿真 ............................................................................................................................................... 102

7.2.1

多板的拓朴拆分

...................................................................................................................................... 104

7.2.2

创建一个连接两板的

Design Link.......................................................................................................... 106

7.2.3

仿真通过

Design Link

连接的网络

..........................................................................................................111

第 3 页 共 116 页

《EDA 工具手册》仿真分册 EDA 平台

前 言

Cadence 软件是我们公司统一使用的原理图设计、PCB 设计、高速仿真的 EDA 工具。进行仿真

工作需要有很多方面的知识,须对高速设计的理论有较全面的认识,并对具体的单板原理有一定的

了解,还需具备仿真库的相关知识等。

在这个分册中仅对仿真软件的使用进行较详细的阐述,还介绍高速设计的一些相关理论,仿真

过程是基于 Allegro SPB 15.2 的 PCB SI 模块进行的。

其他知识,如仿真库的知识、约束管理器等请参阅专门的使用手册。

在此非常感谢网络南研 EDA 和本部 EDA 对此手册的支持。

第 4 页 共 116 页

《EDA 工具手册》仿真分册 EDA 平台

第一章 高速设计与 PCB 仿真流程

本章介绍高速 PCB 仿真设计的基础知识和重要意义,并介绍基于 Cadence 的 Allegro SPB15.2 的 PCB 仿真流

程。

1.1 高速信号与高速设计

随着通信系统中逻辑及系统时钟频率的迅速提高和信号边沿不断变陡,PCB 的走线和板层特性对系统电气性能

的影响也越发显著。对于低频设计,走线和板层的影响要求不高甚至可以完全忽略不计。当频率超过 50MHz 时,PCB

走线则必须以传输线考虑,而在评定系统性能时也必须考虑 PCB 板材的电参数影响。当系统时钟频率达到 120MHz

及更高时,就只能使用高速电路设计方法,否则基于传统方法设计的 PCB 将无法工作。因此,高速电路设计技术

已经成为电子系统设计师必须采取的设计手段,只有通过使用高速电路设计师的设计技术,才能实现设计过程的

可控性。高速系统的设计必须面对互连延迟引起的时序问题以及串扰、传输线效应等信号完整性问题。

通常认为如果数字逻辑电路的频率达到或者超过 45MHZ~50MHZ,而且工作在这个频率之上的电路占整个电

子系统的一定份量(比如说1/3),就称为高速电路。

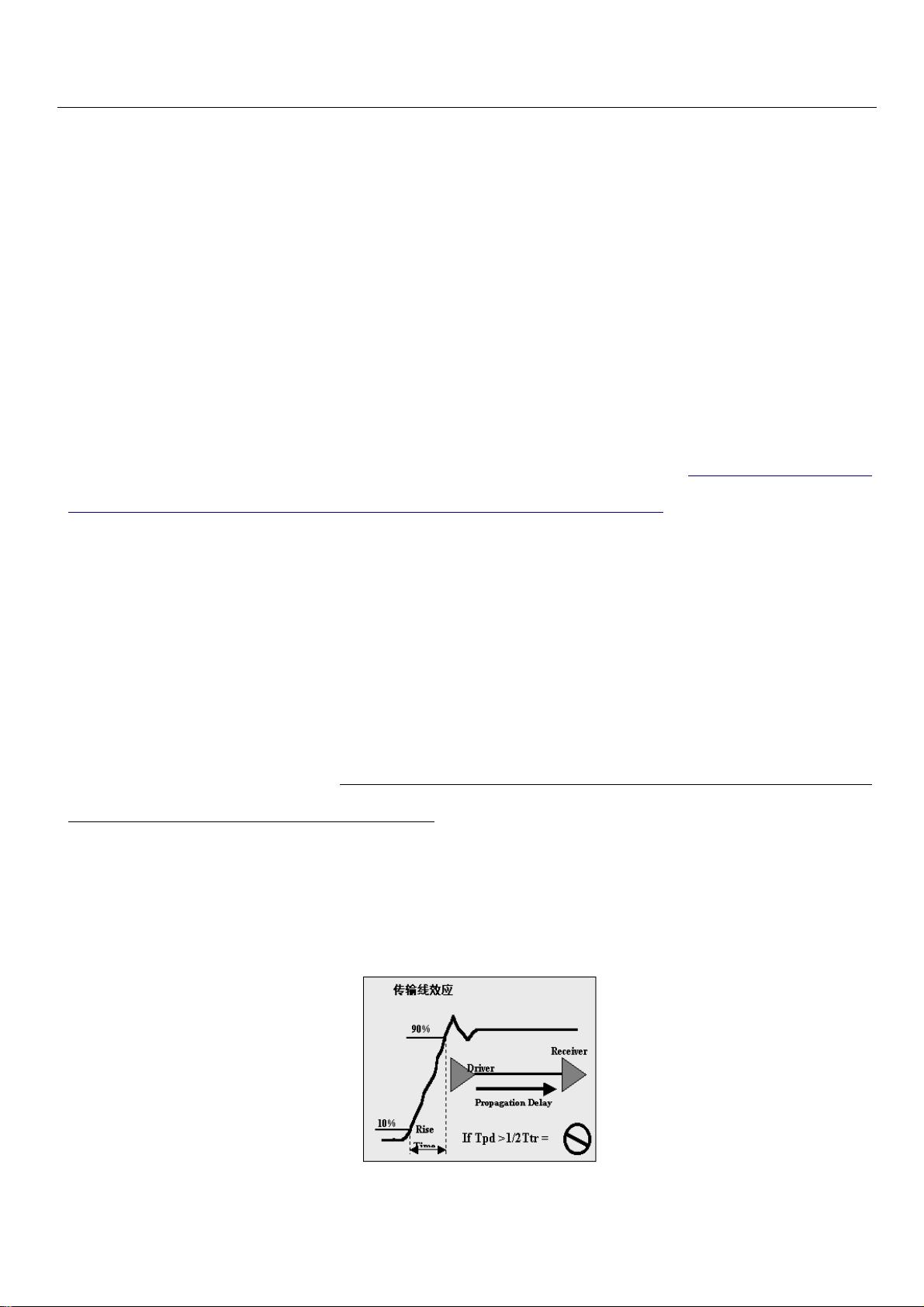

实际上,信号边沿的谐波频率比信号本身的频率高,是信号快速变化的上升沿与下降沿(或称信号的跳变)

引发了信号传输的非预期结果。因此,通常约定如果线传播延时大于 1/2 数字信号驱动端的上升时间,则认为此类

信号是高速信号并产生传输线效应,见图 1-1 所示。

信号的传递发生在信号状态改变的瞬间,如上升或下降时间。信号从驱动端到接收端经过一段固定的延迟时

间,如果传输延迟时间小于 1/2 的上升或下降时间,那么来自接收端的反射信号将在信号改变状态之前到达驱动端。

反之,反射信号将在信号改变状态之后到达驱动端,如果反射信号很强,叠加的波形就有可能会改变逻辑状态。

图 1-1 传输线效应

剩余115页未读,继续阅读

hufeng12345

- 粉丝: 1

- 资源: 6

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论27