没有合适的资源?快使用搜索试试~ 我知道了~

首页VCS-verilog compiled simulator

VCS-verilog compiled simulator

ic design 学习的必备说明,VCS-verilog compiled simulator是synopsys公司的产品.其仿真速度相当快,而且支持多种调用方式;使用的步骤和modelsim类似,都要先做编译,在调用仿真. Vcs包括两种调试界面:Text-based:Command Line Interface(CLI) 和 GUI-based(VirSim);仿真主要的两个步骤是编译,运行: >vcs design.v

资源详情

资源评论

资源推荐

© November 2008 Altera Corporation Quartus II Handbook Version 8.1 Volume 3: Verification

3. Synopsys VCS Support

Introduction

This chapter is an overview about using the Synopsys VCS software to simulate

designs that target Altera

®

FPGAs. It provides a step-by-step explanation of how to

perform register transfer level (RTL) functional simulations, post-synthesis

simulations, and gate-level timing simulations using the VCS software.

This chapter discusses the following topics:

■ “Software Requirements”

■ “Using the VCS Software in the Quartus II Design Flow” on page 3–2

■ “Common VCS Software Compiler Options” on page 3–10

■ “Using VirSim” on page 3–11

■ “Debugging Support Command-Line Interface” on page 3–11

■ “Simulating Designs that Include Transceivers” on page 3–12

■ “Transport Delays” on page 3–14

■ “Using NativeLink with the VCS Software” on page 3–15

■ “Generating a Timing .vcd File for PowerPlay” on page 3–19

■ “Scripting Support” on page 3–19

Software Requirements

To simulate your design using the Synopsys VCS software, you must first set up the

Altera libraries. These libraries are installed with the Quartus

®

II software.

Table 3–1 shows the compatibility between versions of the Quartus II software and

the Synopsys VCS software.

f For more information about installing the software and the directories created during

the Quartus II software installation, refer to the Quartus II Installation and Licensing for

Windows or the Quartus II Installation and Licensing for UNIX and Linux Workstation

manuals.

Table 3–1. Supported Quartus II and VCS Software Version Compatibility

Synopsys Altera

VCS software version Y-2006-06-SP1 Quartus II software version 8.1

VCS software version Y-2006.06-SP1 Quartus II software version 7.2 and 8.0

VCS software version 2006.06 Quartus II software version 7.1

VCS software version 2005.06-SP2 Quartus II software version 7.0 and 6.1

VCS software version 2005.06-SP1 Quartus II software version 6.0

VCS software version 7.2 Quartus II software version 5.1

VCS software version 7.2 Quartus II software version 5.0

VCS software version 7.1.1 Quartus II software version 4.2

QII53002-8.1.0

3–2 Chapter 3: Synopsys VCS Support

Using the VCS Software in the Quartus II Design Flow

Quartus II Handbook Version 8.1 Volume 3: Verification © November 2008 Altera Corporation

Using the VCS Software in the Quartus II Design Flow

You can perform the following types of simulations using VCS:

■ RTL Functional Simulation

■ Post-synthesis Simulation

■ Gate-level timing Simulation

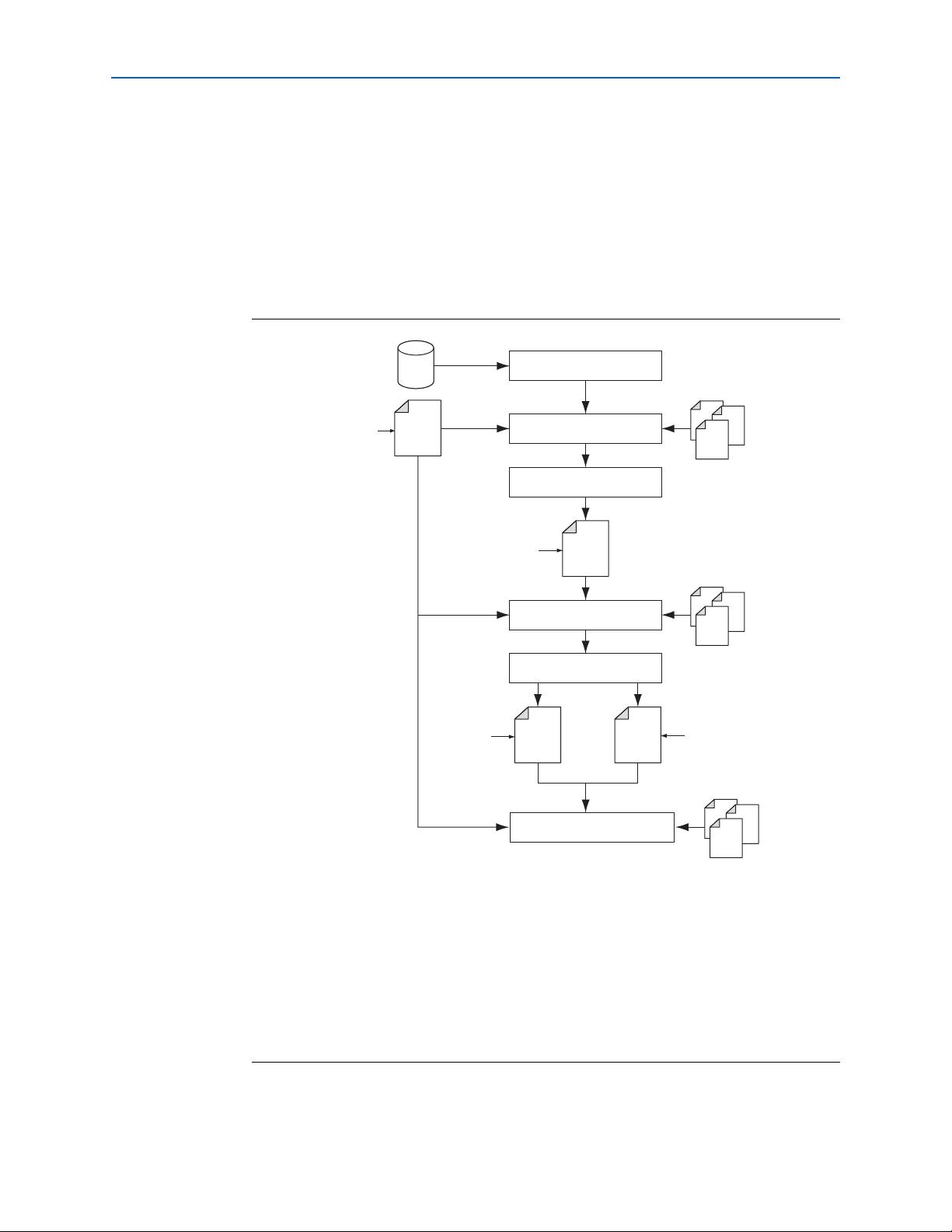

Figure 3–1 shows the VCS and Quartus II software design flow.

Figure 3–1. Altera Design Flow with the VCS and Quartus II Software (Note 1), (2), (3), (4)

Notes to Figure 3–1:

(1) RTL functional simulation is performed before a gate-level timing simulation or post-synthesis simulation. RTL

functional simulation verifies the functionality of the design before synthesis and place-and-route. If you are

performing a functional simulation through NativeLink, you must complete analysis and elaboration first.

(2) A post-synthesis simulation verifies the functionality of a design after synthesis has been performed.

(3) Gate-level timing simulation is a post place-and-route simulation to verify the operation of the design after the timing

delays have been calculated.

(4) All these simulation libraries are located at <quartus installation directory>\eda\sim_lib.

.vo

Design Entry

RTL Functional Simulation (1)

Synthesis

Post-Synthesis Simulation (2)

Verilog Output

File and VHDL

Output File

.sdo

Place-and-Route

.v

Gate-Level Timing Simulation (3)

Gate-Level

Simulation

Library Files

Post-Synthesis

Simulation

Library Files

Functional

Simulation

Library Files

.vo

Verilog Output

File and VHDL

Output File

Standard Delay

Format Output

File

Testbench

ALTERA IP

(4)

.v

(4)

.v

(4)

.v

Chapter 3: Synopsys VCS Support 3–3

Using the VCS Software in the Quartus II Design Flow

© November 2008 Altera Corporation Quartus II Handbook Version 8.1 Volume 3: Verification

Compile Libraries Using the Altera Simulation Library Compiler

The Altera Simulation Library Compiler offers the option to compile Verilog HDL and

VHDL simulation libraries for all Altera devices and supported third-party

simulators. You can use this option to compile all libraries required by RTL and

gate-level simulation.

When you perform simulation using third-party simulation tools, such as ModelSim

and NC-Sim, the user-compiled libraries are kept either into the directory you have

set or into the default directory after compilation. When you perform the simulation

using these simulators, you can use or re-use the user-compiled libraries and avoid

the overhead associated with redundant library compilations.

However, if you use the Synopsys VCS software to perform simulation after running

the Altera Simulation Library Compiler, the compiled libraries are generated, but it

removes the option files (simlib_comp.vcs). You can then include your design and

test bench files into the option files and invoke it with the VCS command.

Before using this option, ensure the appropriate simulation tools are already installed

with the paths either specified in the Quartus II Tools menu, point to Options and

click EDA Tool Options, or in the search path.

To use this utility, you must use the following command:

quartus_sh --simlib_comp [options] r

The options can include:

-family <device>

-tool <simulation tool name>

-language <language>

-directory <directory>

-log <filename>

-suppress_messages

Device family, tool, and language are required options; the other options are optional,

as shown in Example 3–1.

Example 3–2 shows the utility-generated the option file (simlib_comp.vcs) and the

option file:

Example 3–1.

quartus_sh --simlib_comp -family stratixii -tool vcs -language verilog

Example 3–2.

+cli+1 -line -timescale=1ps/1ps \

-v /apps/quartus/8.1/quartus/eda/sim_lib/altera_primitives.v \

-v /apps/quartus/8.1/quartus/eda/sim_lib/220model.v \

-v /apps/quartus/8.1/quartus/eda/sim_lib/sgate.v \

-v /apps/quartus/8.1/quartus/eda/sim_lib/altera_mf.v \

-v /apps/quartus/8.1/quartus/eda/sim_lib/stratixii_atoms.v \

+incdir+/apps/quartus/8.1/quartus/eda/sim_lib

3–4 Chapter 3: Synopsys VCS Support

Using the VCS Software in the Quartus II Design Flow

Quartus II Handbook Version 8.1 Volume 3: Verification © November 2008 Altera Corporation

If you manually run simulation using the Synopsys VCS simulator, you must include

your design file and test bench file into the option file, as shown in Example 3–3:

To compile all of the libraries, design, and test bench files, type the following

command:

vcs -work -f simlib_comp.vcs r

This utility is not available in the user interface; it is only available from the Quartus II

Help, using the command quartus_sh. For more information about its options and

how to define them, you can type the command:

quartus_sh --help=simlib_comp r

RTL Functional Simulations

RTL functional simulations verify the functionality of the design before synthesis,

placement, and routing. These simulations are independent of any Altera FPGA

architecture implementation. After the HDL designs are verified to be functionally

correct, the next step is to synthesize the design and use the Quartus II software to

place-and-route the design in an Altera device.

To functionally simulate an Altera FPGA design in the VCS software that uses Altera

intellectual property (IP) megafunctions, or library of parameterized modules (LPM)

functions, you must include certain libraries during the compilation. Table 3–2

summarizes the Verilog HDL library files that are required to compile LPM functions

and Altera megafunctions.

Example 3–3.

+cli+1 -line -timescale=1ps/1ps design_file.v test_bench_file.vt\

-v /apps/quartus/8.1/quartus/eda/sim_lib/altera_primitives.v \

-v /apps/quartus/8.1/quartus/eda/sim_lib/220model.v \

-v /apps/quartus/8.1/quartus/eda/sim_lib/sgate.v \

-v /apps/quartus/8.1/quartus/eda/sim_lib/altera_mf.v \

-v /apps/quartus/8.1/quartus/eda/sim_lib/stratixiii_atoms.v \

+incdir+/apps/quartus/8.1/quartus/eda/sim_lib

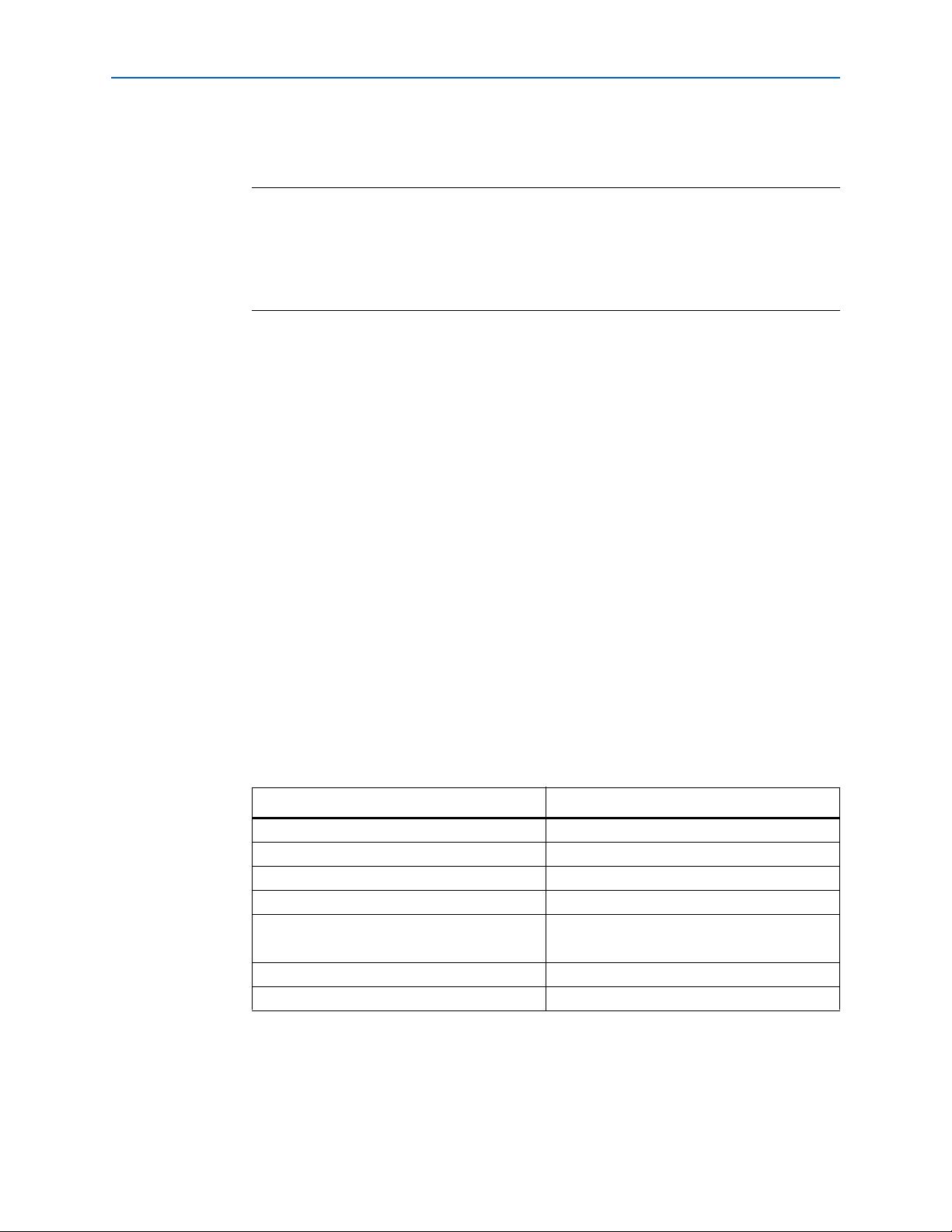

Table 3–2. Altera Verilog HDL Functional/Behavioral Simulation Library Files

Library Name Verilog HDL Libraries

altgx stratixiv_hssi_atoms.v

LPM 220model.v

altera_mf altera_mf.v

altgxb stratixgx_mf.v (1)

alt2gxb stratixiigx_hssi_atoms.v (1)

arriagx_hssi_atoms.v (1)

sgate sgate.v

altera altera_primitives.v

Note to Tab le 3–2 :

(1) The stratixgx_mf.v, stratixiigx_hssi_atoms.v, arriagx_hssi_atoms.v, and stratixiv_hssi_atoms.v library files

require the LPM and SGATE libraries.

Chapter 3: Synopsys VCS Support 3–5

Using the VCS Software in the Quartus II Design Flow

© November 2008 Altera Corporation Quartus II Handbook Version 8.1 Volume 3: Verification

The library files in Table 3–2 are installed with the Quartus II software. These files are

found in the <path to Quartus II installation>\eda\sim_lib directory.

The following is a VCS command for performing an RTL functional simulation with

one of the libraries in Table 3–2:

vcs -R <testbench>.v <design name>.v –v <library file1>.v \

-v <library file 2>.v r

Megafunctions Requiring Atom Libraries

The following Altera megafunctions require gate-level libraries to perform a

functional simulation in a third-party simulator:

■ ALTCLKBUF

■ ALTCLKCTRL

■ ALTDQ

■ ALTDQS

■ ALTDDIO_IN

■ ALTDDIO_OUT

■ ALTDDIO_BIDIR

■ ALTUFM_NONE

■ ALTUFM_PARALLEL

■ ALTUFM_SPI

■ ALTMEMMULT

■ ALTREMOTE_UPDATE

The gate-level library files are located in <path to Quartus II installation>eda/sim_lib

directory (Table 3–3 on page 3–6).

RTL Functional Simulation with Altera Memory Blocks

The VCS software supports functional simulation of complex Altera memory blocks

such as lpm_ram_dp and altsyncram. You can create these memory blocks with the

Quartus II MegaWizard

®

Plug-In Manager, which can be initialized with power-up

data via a Hexadecimal (Intel-Format) File (.hex) or Memory Initialization File (.mif).

The lpm_file parameter included in the file generated by the MegaWizard Plug-In

Manager points to the path of the .hex or .mif file that is used to initialize the memory

block. You can create a .hex or .mif file with the Quartus II software.

Post-Synthesis Simulation

A post-synthesis simulation verifies the functionality of a design after synthesis has

been performed. You can create a post-synthesis netlist in the Quartus II software and

use this netlist to perform a post-synthesis simulation in the VCS software. When the

post-synthesis version of the design has been verified, the next step is to

place-and-route the design in the target architecture using the Quartus II software.

剩余21页未读,继续阅读

l050544117

- 粉丝: 1

- 资源: 6

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论6