Candence 仿真手册 SI PI EMI

1.1.2 边缘速率引发高速问题

EDA设计工程师发现 SI问题的起因不仅仅是高速设计。真正的原因不是系统时钟速率的提高,

而是驱动器上升和下降时间的缩短。随着芯片制造工艺技术的进步及 IC制造商转向采用 0.25微米

或更小工艺,他们所生产的标准元件的裸片尺寸越来越小;边缘速率越来越快,最终会导致 PCB

设计中高速问题的产生,而传统的高速分析是不考虑这类问题的。

此外,当 IC制造商转向可在更小面积上封装更多功能的高密度器件时,需要开发新型的封装技术。

现在, BGA、CSP和 MCM等封装技术都可根据设计要求,在小型封装内提供更多的引脚和更少的

封装寄生参数。尽管这些新型器件体积极小,但它们也有其自身的问题。例如,互连线较长。

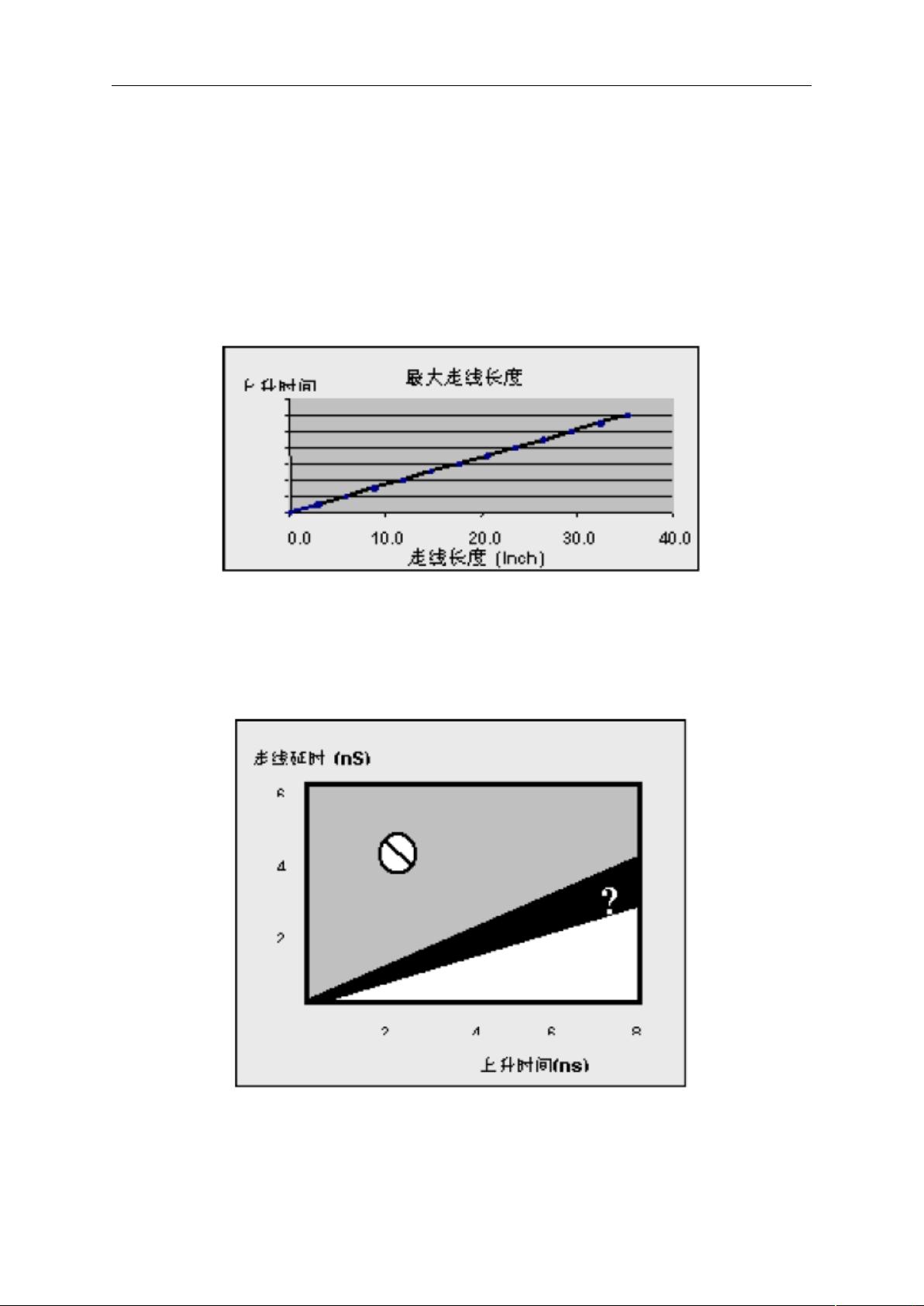

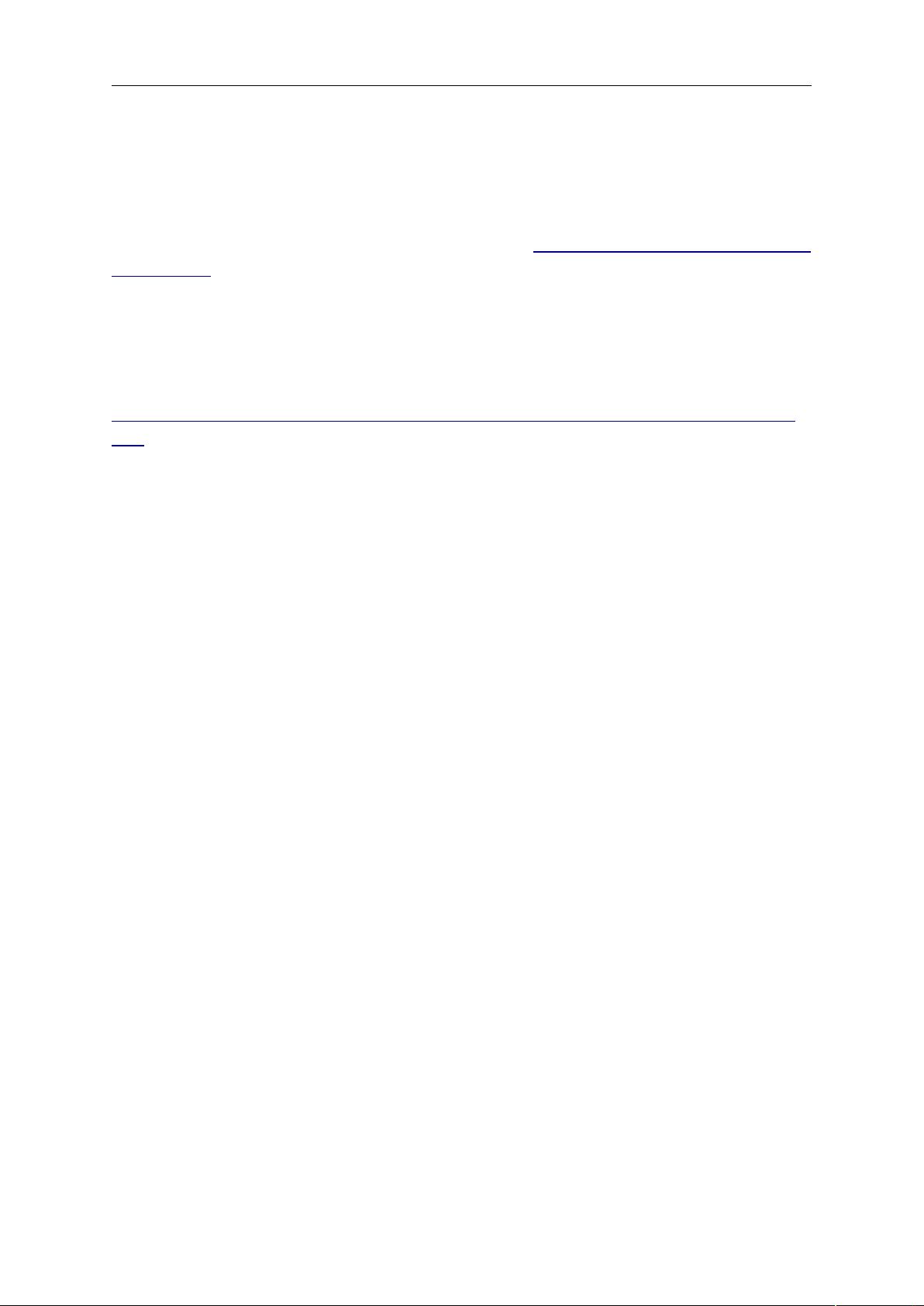

即便不考虑系统时钟速率,高的上升时间和更长的走线长度也让电路板设计工程师面临着严峻的

挑战。只要传输线长度引起的延迟超过驱动器上升/下降时间有效长度的六分之一,就会引起传输

线问题。例如,若上升时间为 1 ns,走线边缘速率为每英寸 2ns,只要走线长度超过 1英寸,就会

发生传输线问题。众所周知,走线长度小于 1英寸的电路板极为少见。因此,采用上升时间为 1ns

的设计肯定会出现高速设计问题。随着新型 IC工艺的出现,情况会变得越来越糟。因为上升时间

将很快发展到 1ns以下。实际上,大约每隔三年晶体管门长度就会缩短,而其相应的开关速率会增

长约 30%。

SI问题的表现方式很多。当边缘速率上升时,时序问题首先暴露出来。传输线效应造成的阻尼

振荡 (Ringing)、正尖峰(overshoot)和负尖峰 (undershoot)有可能超过规定的噪音容限。在低速系统

中,互连延迟和阻尼振荡可以忽略不计,因为在这种系统中信号有足够的时间达到稳定。但是当

边缘速率加快,系统时钟速率上升时,信号在器件之间的传输时间以及同步准备时间都缩短了。

当边缘速率低于 1ns时,串扰问题也出现了。通常串扰问题出现在高边缘速率、高密度的电路

板上,其成因是走线之间的耦合。亚纳秒级边缘速率会引起高频谐振,很容易耦合到邻近的互连

线中,从而造成串扰,拥有大量高速互连的电路板特别容易产生此类问题。

当高速器件的边缘速率低于 0.5ns时,电源系统稳定性和 EMI等问题也随之产生。来自大容量数据

总线的数据交换速率特别快,当它在电源层中产生足以影响信号的强波纹时,就会产生电源稳定

性问题。高速信号也可能产生辐射,EMI因而也成为要关注的另一个设计问题。

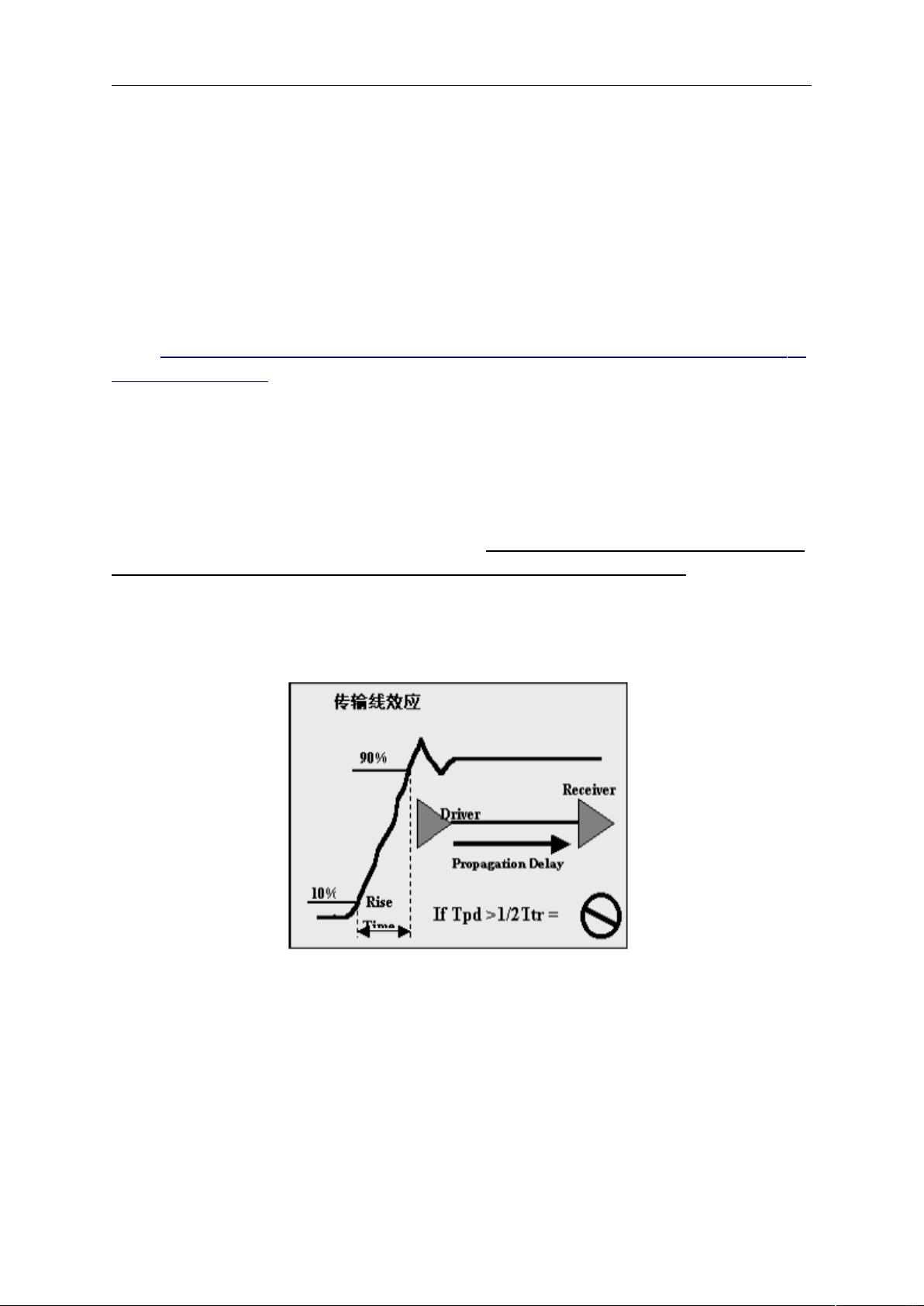

1.1.3 传输线效应

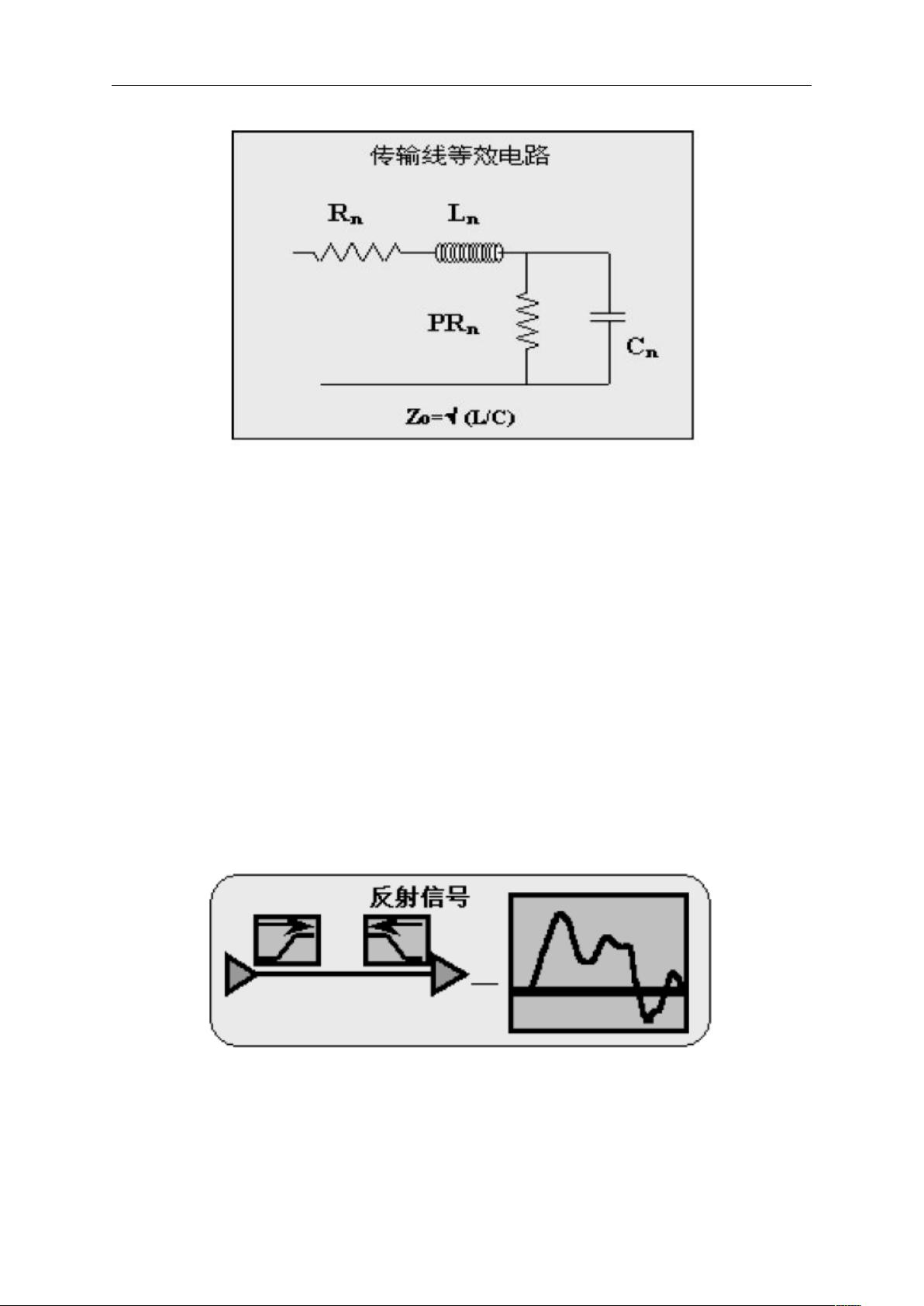

PCB板上的走线可等效为下图所示的串联和并联的电容、电阻和电感结构。串联电阻的典型值

0.25-0.55 ohms/foot,因为绝缘层的缘故,并联电阻阻值通常很高。将寄生电阻、电容和电感加到

实际的 PCB连线中之后,连线上的最终阻抗称为特征阻抗 Zo。线径越宽,距电源 /地越近,或隔

离层的介电常数越高,特征阻抗就越小。如果传输线和接收端的阻抗不匹配,那么输出的电流信

号和信号最终的稳定状态将不同,这就引起信号在接收端产生反射,这个反射信号将传回信号发

射端并再次反射回来。随着能量的减弱反射信号的幅度将减小,直到信号的电压和电流达到稳定。

这种效应被称为振荡,信号的振荡在信号的上升沿和下降沿经常可以看到。

注:关于传输线的等效电路请参照电气篇中的“相关计算”。

评论5