基于基于FPGA的深度学习目标检测系统的设计与实现的深度学习目标检测系统的设计与实现

针对当前深度学习目标检测算法计算复杂度高和内存需求大等问题,设计并实现了一种基于FPGA的深度学习目

标检测系统。设计对应YOLOv2-Tiny目标检测算法的硬件加速器,对加速器各模块的处理时延建模,给出卷积

计算模块的详细设计。实验结果表明,与CPU相比,CPU+FPGA的异构系统是双核ARM-A9能效的67.5

倍,Xeon的94.6倍;速度是双核ARM-A9的84.4倍,Xeon的5.5倍左右。并且,当前设计在性能上超过之前的工

作。

0 引言引言

近年来,以卷积神经网络(Convolutional Neural Network,DNN)为代表的深度学习算法在许多计算机视觉任务上取得了巨

大突破,如图像分类、目标检测、画质增强等

[1-2]

。然而,随着识别率的提高,深度学习算法的计算复杂度和内存需求也急剧

增加,当前的通用处理器无法满足其计算需求。主流的解决方法是采用图形处理器(Graphics Processing Unit,GPU)、专用

集成电路(Application Specific Integrated Circuit,ASIC)芯片或现场可编程门阵列(Field-Programmable Gate Array,FPGA)

来提升计算性能。GPU采用单指令流多数据流架构,想要充分发挥计算性能,需要大批量数据,并且由于高并行度导致的高

功耗,很难应用于对功耗有严格限制的场合

[3]

。ASIC对于具体应用可以获得最佳性能和能效,但是研发周期长,需要对市场

有长久的预见性。FPGA作为一种高性能、低功耗的可编程芯片,可以使用硬件描述语言来设计数字电路,以形成对应算法的

加速电路结构。与GPU相比,FPGA低功耗、低延时,适用于小批量流式应用

[4]

。与ASIC相比,FPGA可以通过配置重新改变

硬件结构,对具体应用定制硬件,适用于深度学习这种日新月异、不断改变的场景。

本文首先介绍深度学习中的YOLOv2-Tiny目标检测算法

[5]

,然后设计对应的硬件加速器,并且就加速器中各模块的处理时

延进行简单建模,给出卷积模块的详细设计,最后,在Xilinx公司的Zedboard开发板上进行评估。

1 YOLOv2-Tiny模型简介模型简介

YOLOv2-Tiny目标检测算法由以下3步组成:

(1)对任意分辨率的RGB图像,将各像素除以255转化到[0,1]区间,按原图长宽比缩放至416×416,不足处填充0.5。

(2)将步骤(1)得到的416×416×3大小的数组输入YOLOv2-Tiny网络检测,检测后输出13×13×425大小的数组。对于

13×13×425数组的理解:将416×416的图像划分为13×13的网格。针对每个网格,预测5个边框,每个边框包含85维特征(共

5×85=425维)。85维特征由3部分组成:对应边框中包含的80类物体的概率(80维),边框中心的相对偏移以及相对长宽比的预

测(4维),边框是否包含物体的可信度(1维)。

(3)处理步骤(2)中得到的13×13×425大小的数组,得到边框的中心和长宽。根据各边框覆盖度、可信度和物体的预测概率

等,对13×13×5个边框进行处理,得到最有可能包含某物体的边框。根据原图的长宽比,将得到的边框调整到原图尺度,即得

到物体的位置与类别信息。

YOLOv2-Tiny由16层组成,涉及3种层:卷积层(9层)、最大池化层(6层)以及最后的检测层(最后1层)。其中,卷积层起到特

征提取的作用,池化层用于抽样和缩小特征图规模。将步骤(1)称为图像的预处理,步骤(3)称为图像的后处理(后处理包含检测

层的处理)。

1.1 卷积层卷积层

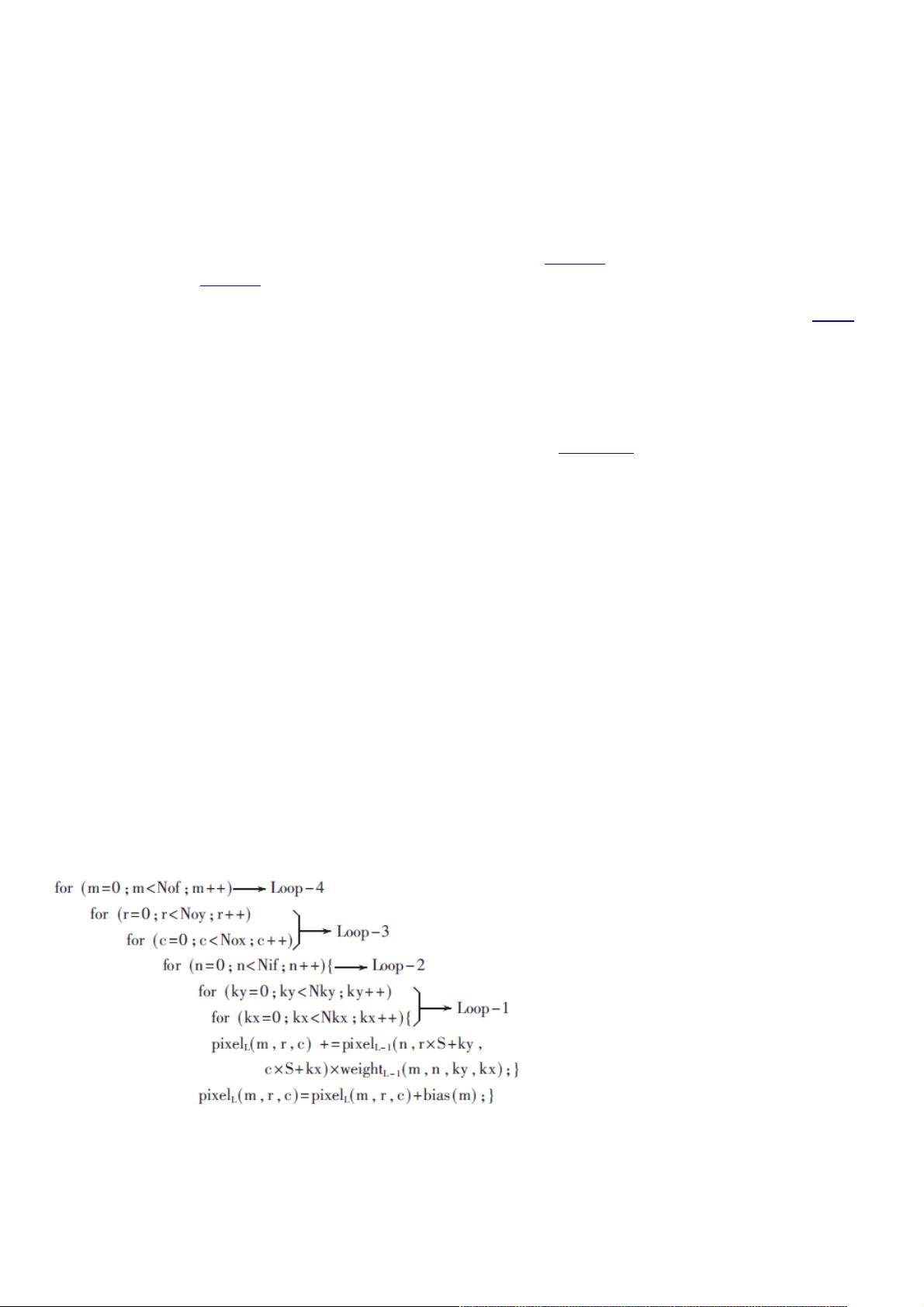

对输入特征图以对应的卷积核进行卷积来实现特征提取,伪代码如下:

其中(Noy,Nox)、Nof、Nif、(Nky,Nkx)、S分别代表输出特征图、输出特征图数、输入特征图数、卷积核大小和步长。

pixelL(m,r,c)代表输出特征图m中r行c列的像素。

1.2 池化层池化层

对输入特征图降采样,缩小特征图的规模,一般跟在卷积层后。YOLOv2-Tiny采用最大池化层,最大池化层伪代码如下所

示:

评论0