<01111>

<10100>

<11101>

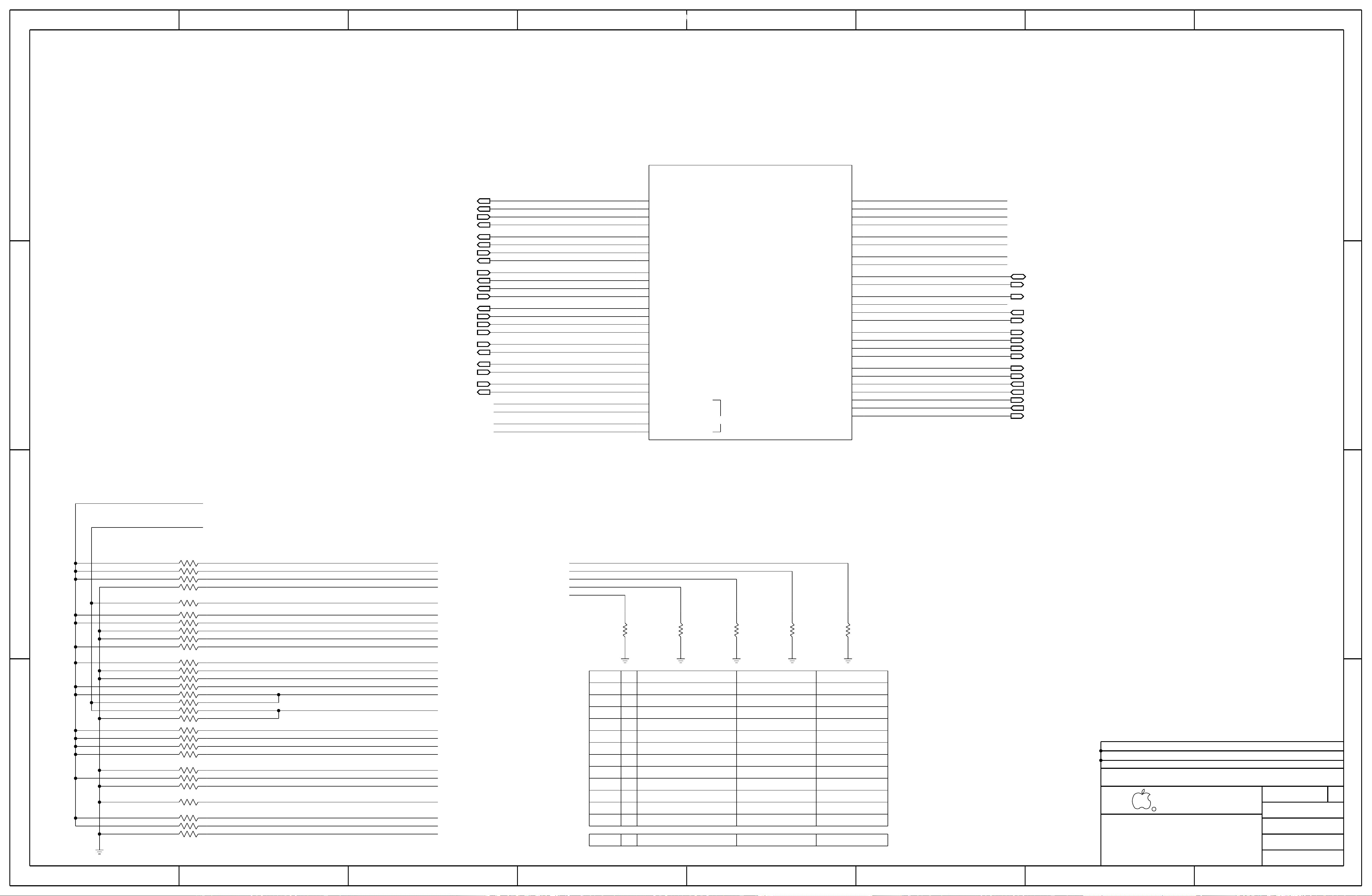

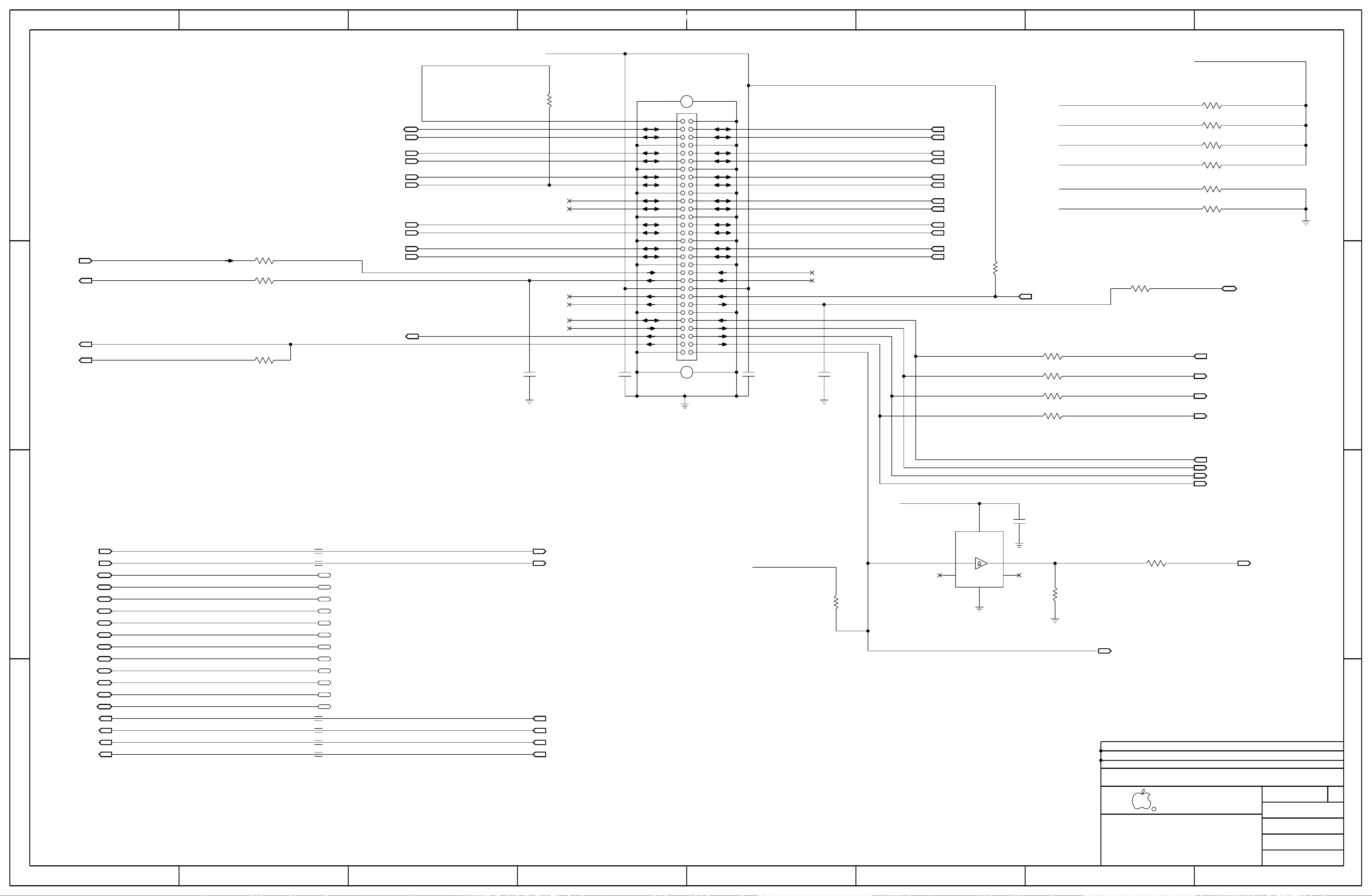

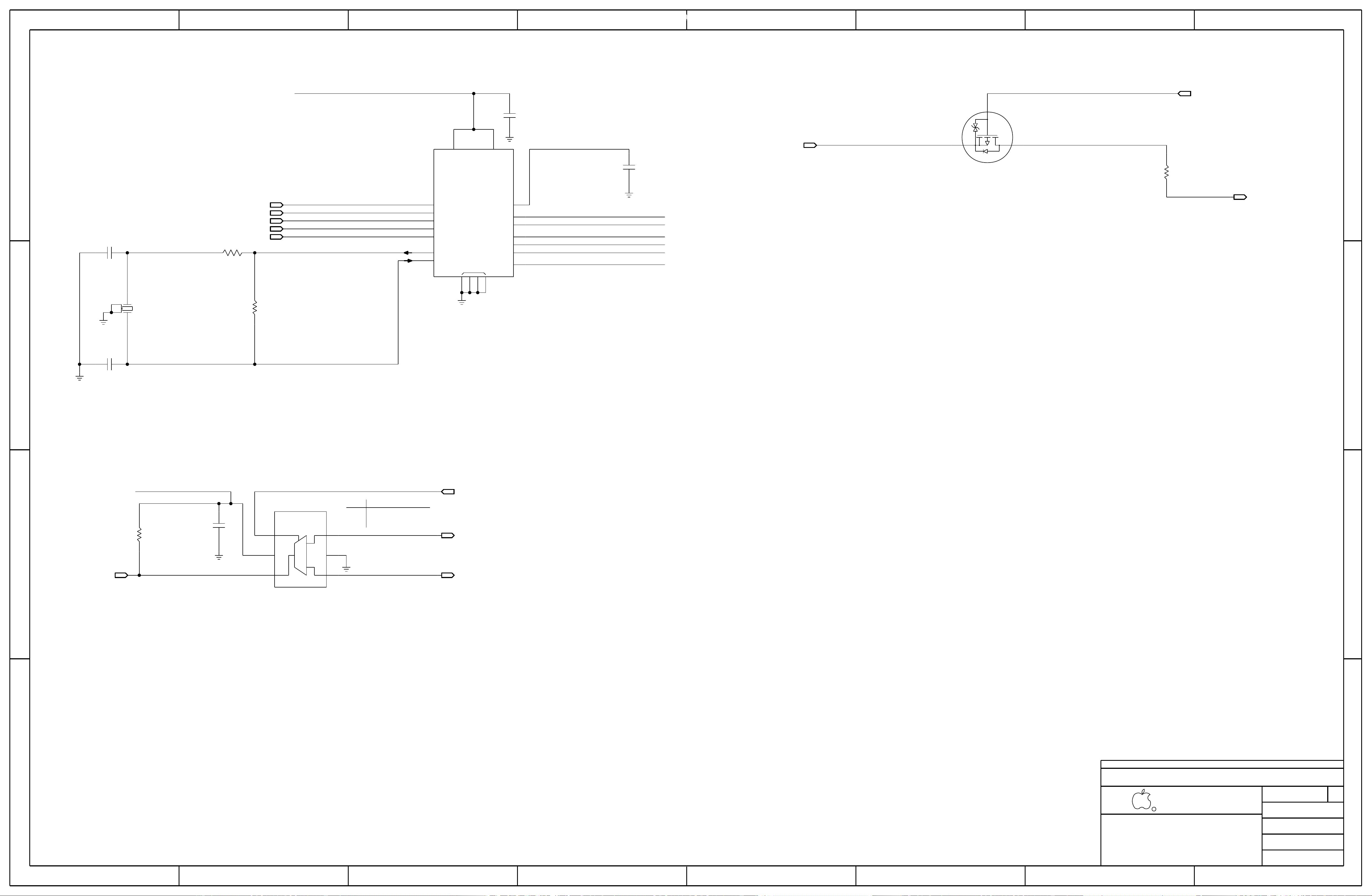

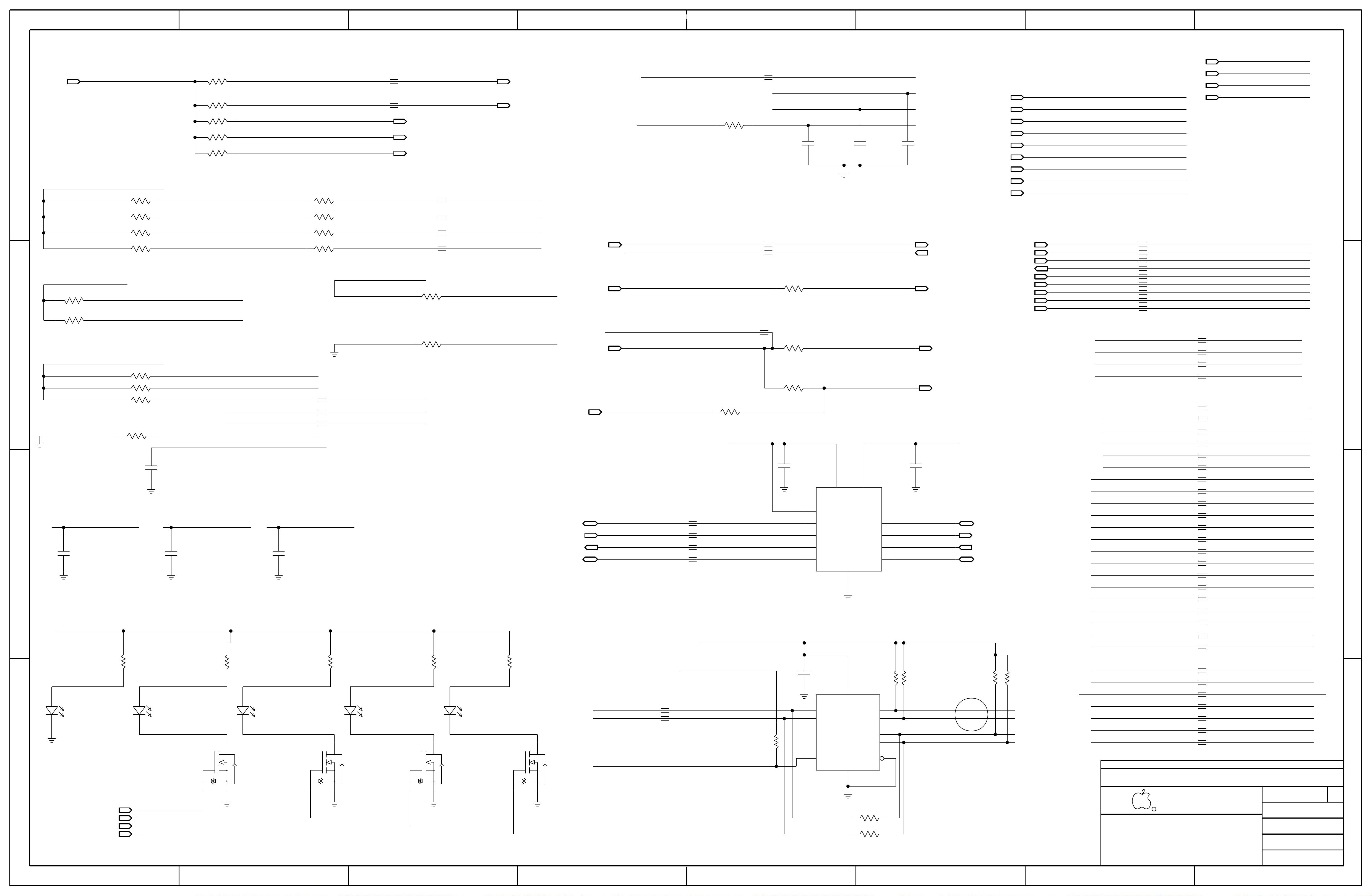

DESIGN: X502/MLB

(STRAP)

(1.8V)

(1.8V)

(1.8V)

(STRAP)

ALL GPP_F* PINS ARE 1.8V ONLY!

CODE

<11100>

<11110>

<11111>

<10111>

LAST CHANGE: Wed Oct 28 12:50:22 2015

<10101>

<11000>

<11001>

<11010>

<10110>

<11011>

DRIVEN PUSH PULL FROM SWITCHED RAIL.

PCH INTERNAL PULL-UPS ARE TO VCCGPPD = 3.3V.

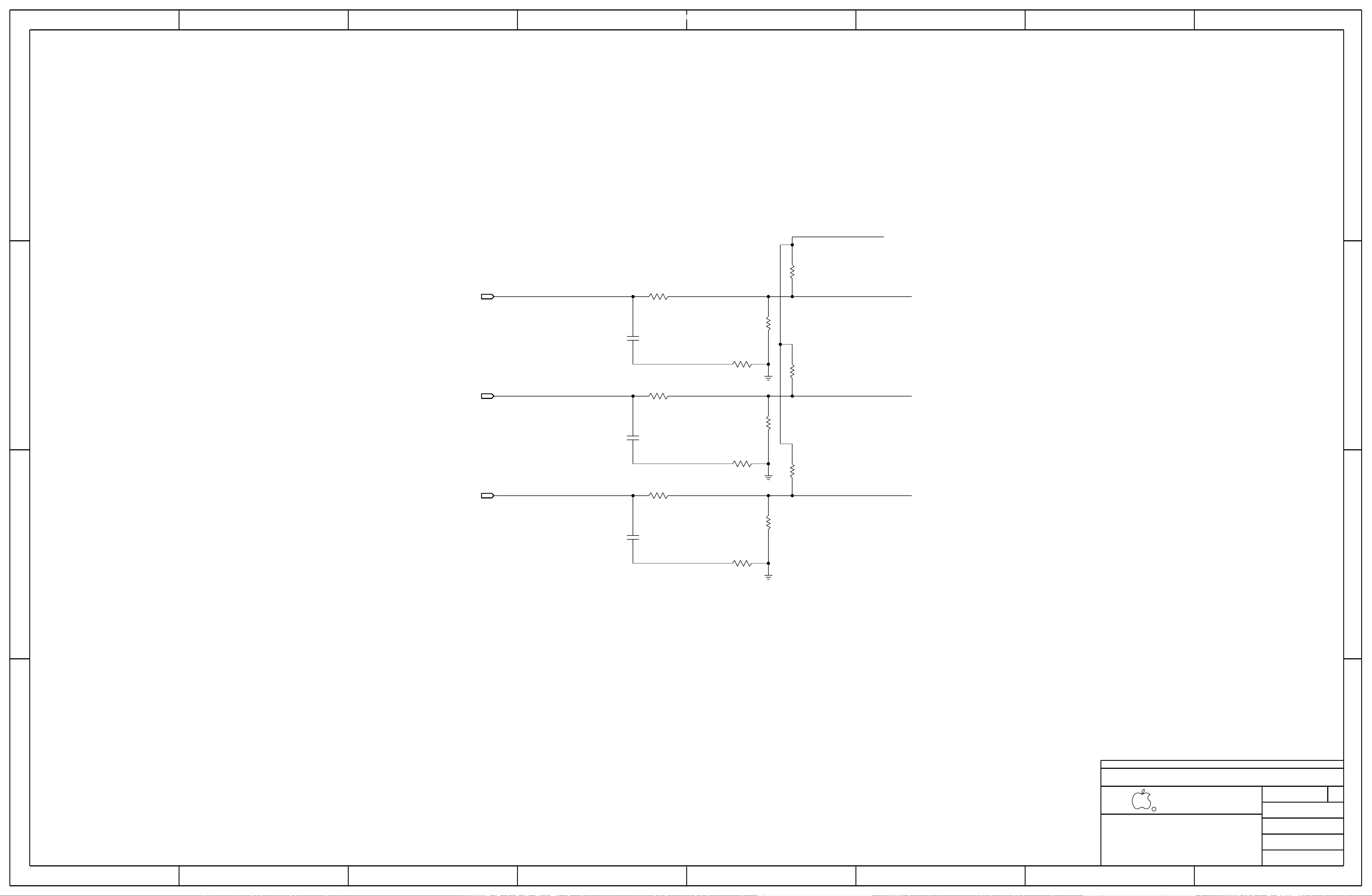

MLB ID STRAPS.

16 OF 119

PD_AUD_SPI_MISO

PU_AUD_SPI_CS_L

NC_I2C_UPC_SDA

NC_MLB_DEV_L

PD_AUD_SPI_CLK

NC_I2C_UPC_SCL

NC_PCH_GPP_D1

102

NC_SPKR_ID1

19

NC_PCH_GPP_D3

102

NC_PCH_GPP_D4

102

PD_AP_DEV_WAKE

BT_I2S_SYNC_1V8

19

PCH_SSD_SOC_UART_R2D

PCH_SSD_SOC_UART_D2R

TBT_T_CIO_PLUG_EVENT_L

TBT_X_CIO_PLUG_EVENT_L

PU_AUD_SPI_MOSI

PU_SOC_UART_RTS_L

BT_I2S_R2D_1V8

19

BT_I2S_CLK_1V8

19

DDI1_MUX_SEL

DDI2_MUX_SEL

BT_I2S_D2R_1V8

19

PCH_SSD_SOC_UART_R2D

16 19

PD_SOC_UART_CTS_L

16 19

PD_AP_DEV_WAKE

16 19

TBT_X_CIO_PLUG_EVENT_L

16 28

TBT_T_CIO_PLUG_EVENT_L

16 94

PD_AUD_SPI_CLK

16 19

PU_AUD_SPI_MOSI

16 19

PD_AUD_SPI_MISO

16 19

PU_AUD_SPI_CS_L

16 19

PU_SOC_UART_RTS_L

16 19

PD_SOC_UART_CTS_L

PCH_SSD_SOC_UART_D2R

16 19

PP3V3_SUS

8 13 14 15 101

PP3V3_S0

5 13 14 19 94 101

16 OF 145

9.0.0

051-00515

dvt-fab09-0

TPAD_SPI_CS_L

TPAD_SPI_CLK

TPAD_SPI_MISO

TPAD_SPI_MOSI

TBT_T_PCI_RESET_L

MLB_BOARD_ID3

TBT_X_PCI_RESET_L

TBT_T_CIO_PWR_EN

AP_RESET_L

SPIROM_USE_MLB

TBT_T_USB_PWR_EN

MLB_BOARD_ID2

MLB_BOARD_ID1

MLB_BOARD_ID4

LCD_IRQ_L

PCH_BT_UART_D2R

SSD_RESET_L

MLB_BOARD_ID4

MLB_BOARD_ID0

MLB_BOARD_ID3

MLB_BOARD_ID2

MLB_BOARD_ID1

MLB_BOARD_ID0

TPAD_SPI_IF_EN

TPAD_SPI_INT_L

AUD_PWR_EN

PCH_BT_UART_RTS_L

PCH_BT_UART_R2D

TBT_POC_RESET

PCH_BT_UART_CTS_L

AP_S0IX_WAKE_L

AP_S0IX_WAKE_SEL

SPIROM_USE_MLB

PCH_BT_UART_CTS_L

LCD_IRQ_L

TBT_POC_RESET

AP_S0IX_WAKE_L

AP_S0IX_WAKE_SEL

TPAD_SPI_CS_L

AUD_PWR_EN

TPAD_SPI_INT_L

TPAD_SPI_MOSI

TPAD_SPI_MISO

TPAD_SPI_CLK

PCH_BT_UART_RTS_L

PCH_BT_UART_R2D

PCH_BT_UART_D2R

TPAD_SPI_IF_EN

BOM_COST_GROUP=CPU & CHIPSET

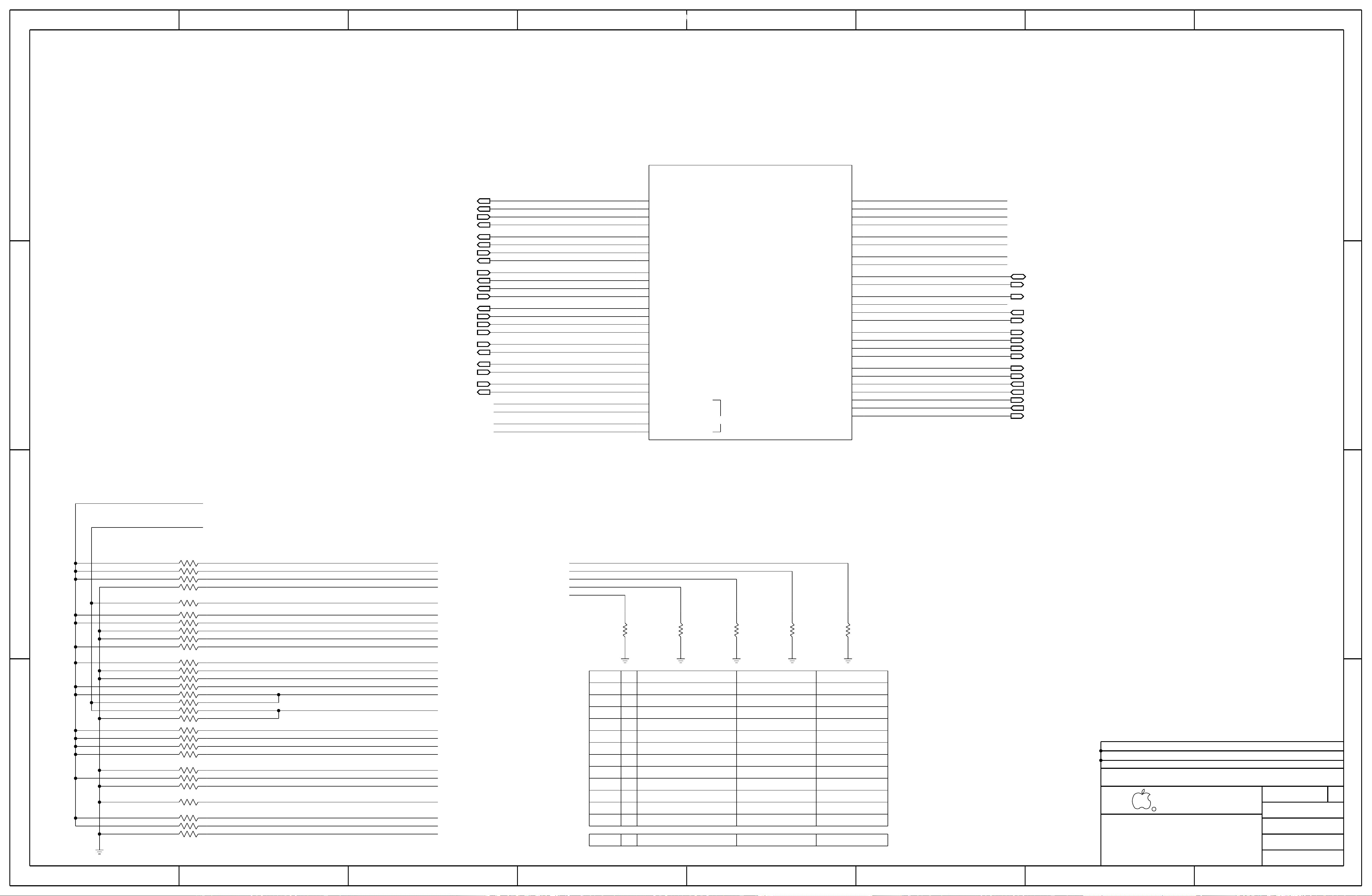

PCH SPI/UART/GPIO

SYNC_MASTER=J130_MLB SYNC_DATE=12/08/2015

BOARD_ID:00 RES,MF,1/20W/1K OHM,5,0201,SMD117S0006

BOARD_ID:11R1693,R1691,R16903117S0006 RES,MF,1/20W/1K OHM,5,0201,SMD

BOARD_ID:16R1694117S0006 1 RES,MF,1/20W/1K OHM,5,0201,SMD

BOARD_ID:10R1693,R16912117S0006 RES,MF,1/20W/1K OHM,5,0201,SMD

BOARD_ID:1R16901117S0006 RES,MF,1/20W/1K OHM,5,0201,SMD

BOARD_ID:2RES,MF,1/20W/1K OHM,5,0201,SMD R1691117S0006 1

BOARD_ID:9R1693,R16902117S0006 RES,MF,1/20W/1K OHM,5,0201,SMD

BOARD_ID:52 R1692,R1690117S0006 RES,MF,1/20W/1K OHM,5,0201,SMD

RES,MF,1/20W/1K OHM,5,0201,SMD BOARD_ID:32 R1691,R1690117S0006

RES,MF,1/20W/1K OHM,5,0201,SMD BOARD_ID:4R1692117S0006 1

BOARD_ID:8117S0006 RES,MF,1/20W/1K OHM,5,0201,SMD1 R1693

RES,MF,1/20W/1K OHM,5,0201,SMD BOARD_ID:73 R1692,R1691,R1690117S0006

R1692,R1691 BOARD_ID:62117S0006 RES,MF,1/20W/1K OHM,5,0201,SMD

10K

MF 201

NOSTUFF

5% 1/20W

R1676

1 2

100K

1/20W 201MF5%

NOSTUFF

R1675

1 2

100K

201MF1/20W5% NOSTUFF

R1674

1 2

100K

1/20W5% MF 201

R1673

1 2

1/20W5% 201

100K

MF

R1669

1 2

1K

MF

201

5%

1/20W

OMIT_TABLE

R1694

1

2

1K

MF

201

5%

1/20W

OMIT_TABLE

R1693

1

2

1/20W

1K

MF

201

5%

OMIT_TABLE

R1692

1

2

1K

MF

201

5%

1/20W

OMIT_TABLE

R1691

1

2

1K

MF

201

5%

1/20W

OMIT_TABLE

R1690

1

2

1/20W5% 201MF

100K

R1672

1 2

47K

1/20W5% 201MF

R1642

1 2

47K

1/20W5% 201MF

R1641

1 2

5% 201MF

47K

1/20W

R1640

1 2

47K

1/20W5% 201MF

R1643

1 2

19

43 16

1/20W5% 201MF

100K

R1671

1 2

5% 201MF

100K

1/20W

R1668

1 2

1/20W5% 201MF

100K

R1667

1 2

1/20W5% 201MF

100K

R1666

1 2

1/20W5% MF

100K

201

R1665

1 2

1/20W5% 201MF

47K

R1664

1 2

1/20W5% 201MF

47K

R1663

1 2

47K

5% 1/20W 201MF

R1662

1 2

47K

2015% 1/20W MF

R1661

1 2

150K

5% MF 2011/20W

R1660

1 2

47K

MF5% 2011/20W

R1659

1 2

47K

5% 201MF1/20W

R1658

1 2

MF

47K

5% 2011/20W

R1657

1 2

47K

5% 1/20W MF 201

R1655

1 2

MF

1K

1/20W5% 201

R1656

1 2

1/20W 201MF

47K

5%

R1654

1 2

1/20W5% 201

47K

MF

R1653

1 2

2011/20W5% MF

100K

R1652

1 2

201MF

100K

5% 1/20W

R1650

1 2

19

61 16

43 16

19

28

28

59 16

104 80 16

19

19

94

94

19 16

36 35 19

94 28 16

104 91 19

19 16

19 16

19 16

19 16

94 16

28 16

18 16

18 16

35 16

35 16

35 16

35 16

43 16

43 16

43 16

43 16

19 16

19 16

19 16

19 16

BGA

TBD

SKL-ULT-2+3E

OMIT_TABLE

U0500

AY8

BA8

BB7

BA7

AY7

AW7

AN8

AP7

AP8

AR7

AM5

AN7

AP5

AN5

AB1

AB2

W4

AB3

AC1

AC2

AC3

AB4

U7

U6

U8

U9

M2

M3

J4

B7

M4

N3

N1

N2

P2

P3

AK6

AK7

AK9

AK10

AH9

AH10

AB12

W12

W11

W10

W8

W7

N11

N12

AP13

16

16

16

16

16

16

16

16

16

16

59 16

35 16

104 80 16

94 28 16

18 16

18 16

43 16

61 16

43 16

43 16

43 16

43 16

35 16

35 16

35 16

43 16

II NOT TO REPRODUCE OR COPY IT

III NOT TO REVEAL OR PUBLISH IT IN WHOLE OR PART

I TO MAINTAIN THIS DOCUMENT IN CONFIDENCE

THE POSESSOR AGREES TO THE FOLLOWING:

36

BRANCH

REVISION

DRAWING NUMBER SIZE

D

R

IV ALL RIGHTS RESERVED

SHEET

PAGE TITLE

C

A

D

2 1

PAGE

NOTICE OF PROPRIETARY PROPERTY:

A

B

C

345678

D

B

8 7 5 4 2 1

PROPRIETARY PROPERTY OF APPLE INC.

THE INFORMATION CONTAINED HEREIN IS THE

Apple Inc.

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

PART# DESCRIPTIONQTY

TABLE_5_HEAD

BOM OPTIONREFERENCE DESIGNATOR(S)

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

TABLE_5_ITEM

IN

IN

BI

OUT

OUT

OUT

IN

IN

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

OUT

IN

IN

OUT

OUT

IN

IN

IN

IN

OUT

IN

OUT

OUT

IN

OUT

IN

OUT

OUT

OUT

IN

OUT

OUT

SYM 6 OF 20

LPSS ISH

BM_BUSY*/ISH_GP6

GPP_A18/ISH_GP0

GPP_C19/I2C1_SCL

GPP_C13/UART1_TXD/ISH_UART1_TXD

GPP_D3/SPI1_MOSI

GPP_D4/FLASHTRIG

GPP_F2/I2S2_TXD

GPP_F0/I2S2_SCLK

GPP_C15/UART1_CTS*/ISH_UART1_CTS*

GPP_C14/UART1_RTS*/ISH_UART1_RTS*

GPP_C12/UART1_RXD/ISH_UART1_RXD

GPP_F3/I2S2_RXD

GPP_F1/I2S2_SFRM

GPP_C11/UART0_CTS*

GPP_C10/UART0_RTS*

GPP_B21/GSPI1_MISO

GPP_B22/GSPI1_MOSI

GPP_C8/UART0_RXD

GPP_C18/I2C1_SDA

GPP_C17/I2C0_SCL

GPP_C16/I2C0_SDA

GPP_C9/UART0_TXD

GPP_B19/GSPI1_CS*

GPP_B20/GSPI1_CLK

GPP_B15/GSPI0_CS*

GPP_B16/GSPI0_CLK

GPP_B17/GSPI0_MISO

GPP_B18/GSPI0_MOSI

GPP_D5/ISH_I2C0_SDA

GPP_D6/ISH_I2C0_SCL

GPP_D7/ISH_I2C1_SDA

GPP_D8/ISH_I2C1_SCL

GPP_D1/SPI1_CLK

GPP_D2/SPI1_MISO

GPP_F4/I2C2_SDA

GPP_F5/I2C2_SCL

GPP_G6/SD_CLK

GPP_D9

GPP_G7/SD_WP

GPP_D10

GPP_G2/SD_DATA1

GPP_G3/SD_DATA2

GPP_G4/SD_DATA3

GPP_G5/SD_CD*

GPP_A19/ISH_GP1

GPP_A20/ISH_GP2

GPP_A21/ISH_GP3

GPP_A22/ISH_GP4

GPP_A23/ISH_GP5

SX_EXIT_HOLDOFF*/GPP_A12/

GPP_E22

GPP_E23