没有合适的资源?快使用搜索试试~ 我知道了~

首页MT6771 datasheet(芯片手册)

资源详情

资源评论

资源推荐

© 2018 MediaTek Inc.

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

M

e

Version: 1.1

Release date: 2018-02-13

Specifications are subject to change without notice.

MT6771 LTE-A Smartphone Application

Processor Technical Brief

M

MT6771

LTE-A Smartphone Application Processor

Technical Brief

© 2018 MediaTek Inc.

Page 2 of 73

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

A

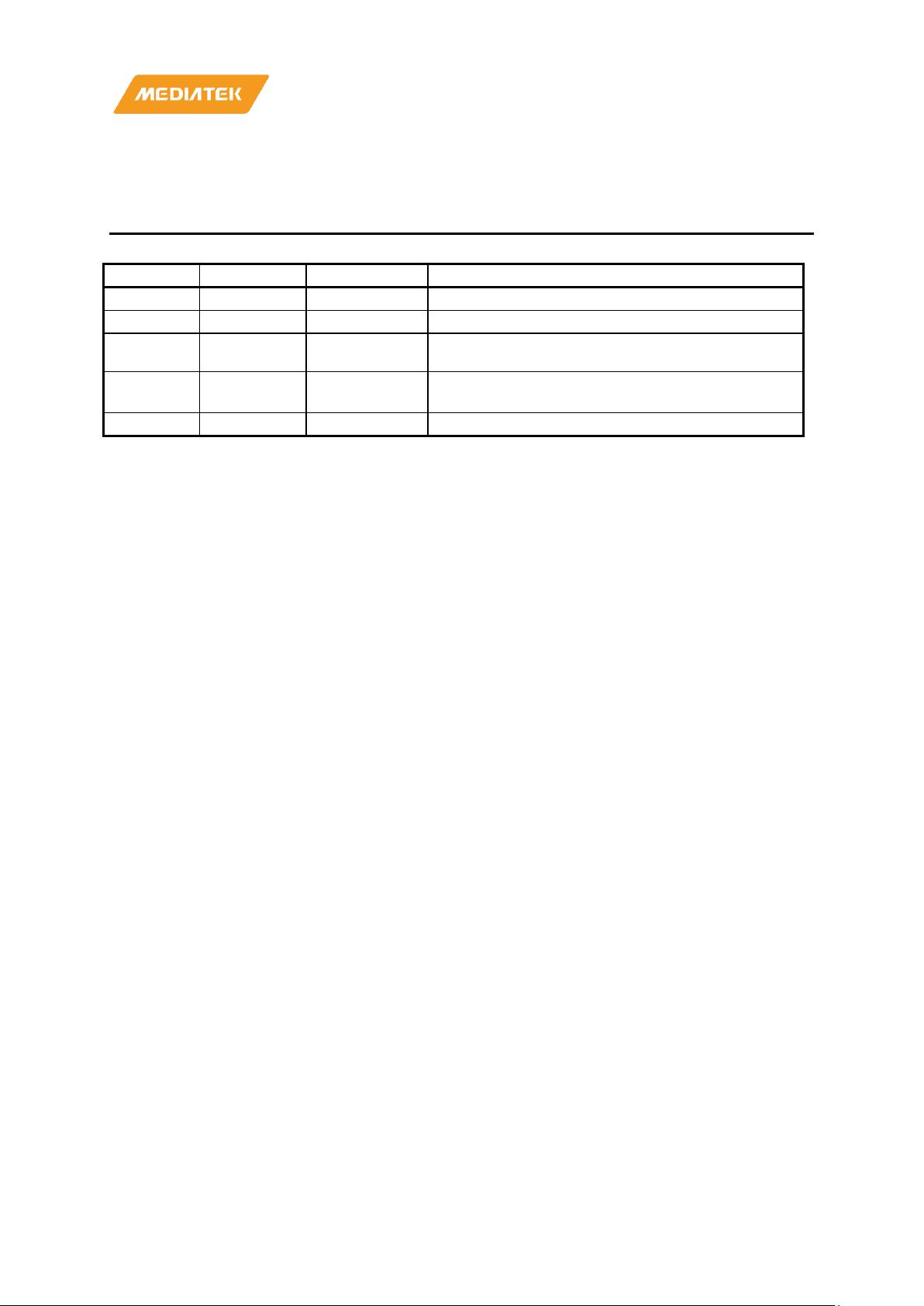

Document Revision History

Revision

Date

Author

Description

0.1

2017-07-18

YT Lin

Initial draft

0.2

2017-09-20

YT Lin

Updated Figure 2-2, Table 2-36 and Table 2-37.

0.3

2017-12-05

MN Tsou

Updated features (LP4-3600 8GB/GPU

800MHz/connectivity).

1.0

2018-02-05

MN Tsou

1. Updated AVDD2_EMI/AVDDQ_EMI voltage for LP4.

2. Updated MSDC0 VIH and VIL.

1.1

2018-02-13

MN Tsou

Updated operation condition.

MT6771

LTE-A Smartphone Application Processor

Technical Brief

© 2018 MediaTek Inc.

Page 3 of 73

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

A

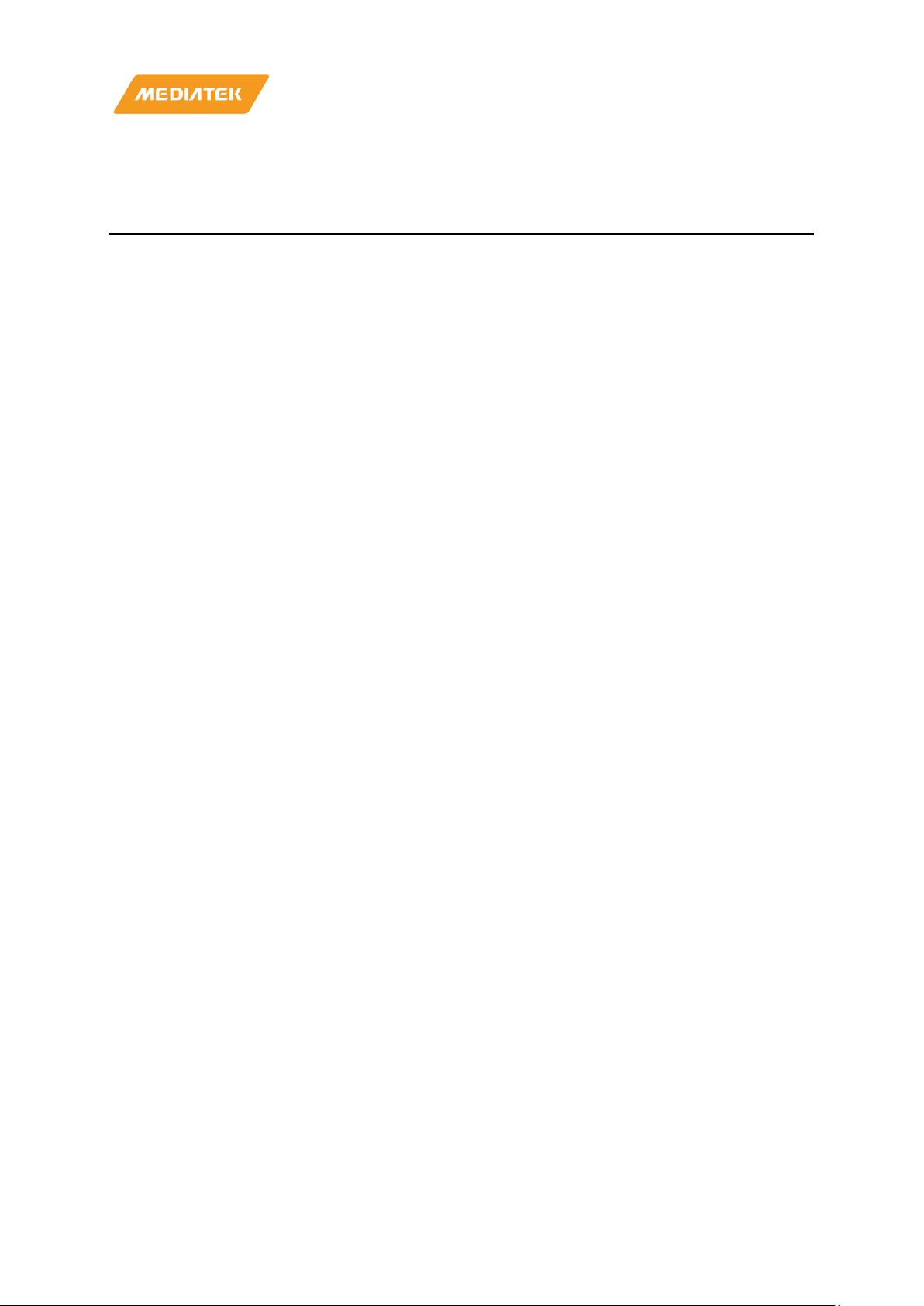

Table of Contents

Document Revision History ............................................................................................. 2

Table of Contents .............................................................................................................. 3

1 System Overview ...................................................................................................... 6

1.1 Highlighted Features Integrated in MT6771 ........................................................................... 6

1.2 Platform Features ...................................................................................................................... 8

1.3 Modem Features....................................................................................................................... 10

1.4 Connectivity Features .............................................................................................................. 12

1.5 Multimedia Features ................................................................................................................ 15

2 Product Description ................................................................................................17

2.1 Pin Description ......................................................................................................................... 17

2.2 Electrical Characteristic ........................................................................................................... 41

2.3 System Configuration.............................................................................................................. 63

2.4 Power-on Sequence ................................................................................................................. 64

2.5 Analog Baseband ..................................................................................................................... 65

2.6 Package Information ................................................................................................................ 72

Lists of Figures and Tables

Figure 1-1. High-level MT6771 functional block diagram ........................................................................... 7

Figure 2-1. LPDDR4 ball map view ............................................................................................................ 17

Figure 2-2. LPDDR3 ball map view ............................................................................................................ 18

Figure 2-3. LPDDR3 VIX definition ...........................................................................................................47

Figure 2-4. LPDDR3 single-ended output slew-rate definition ............................................................... 48

Figure 2-5. LPDDR3 differential output slew-rate definition .................................................................. 48

Figure 2-6. LPDDR3 RX mask ................................................................................................................... 48

Figure 2-7. LPDDR4/LPDDR4X VIX definition ....................................................................................... 49

Figure 2-8. LPDDR4/LPDDR4X single-ended output slew-rate definition ........................................... 49

Figure 2-9. LPDDR4/LPDDR4X differential output slew-rate definition .............................................. 50

Figure 2-10. LPDDR4/LPDDR4X RX mask ............................................................................................. 50

Figure 2-11. SPI timing diagram ................................................................................................................. 51

Figure 2-12. I2S master mode timing diagram .......................................................................................... 51

Figure 2-13. I2C timing diagram of standard mode (100kHz) and fast mode (400kHz) ...................... 52

Figure 2-14. MSDC device input timing diagram of default speed .......................................................... 53

Figure 2-15. MSDC device output timing diagram of default speed ........................................................ 53

Figure 2-16. MSDC device input timing diagram of high speed .............................................................. 54

Figure 2-17. MSDC device output timing diagram of high speed ............................................................. 55

Figure 2-18. MSDC device clock timing diagram of SDR12/SDR25/SDR50/SDR104 mode ................. 55

Figure 2-19. MSDC device input timing diagram of SDR50/SDR104 mode .......................................... 56

Figure 2-20. MSDC device output timing diagram of fixed data window (SDR12/SDR25/SDR50) .... 56

Figure 2-21. MSDC device output timing diagram of variable window (SDR104) ................................. 56

Figure 2-22. MSDC device clock timing diagram of DDR50 speed mode................................................ 57

Figure 2-23. MSDC device input/output timing diagram of DDR50 speed mode ................................. 58

MT6771

LTE-A Smartphone Application Processor

Technical Brief

© 2018 MediaTek Inc.

Page 4 of 73

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

A

Figure 2-24. MSDC device clock timing diagram of HS200 .................................................................... 59

Figure 2-25. MSDC device input timing diagram of HS200 .................................................................... 59

Figure 2-26. MSDC device output timing diagram of HS200 ................................................................. 59

Figure 2-27. MSDC device input timing diagram of HS400 .................................................................... 60

Figure 2-28. MSDC device output timing diagram of HS400 .................................................................. 61

Figure 2-29. Power-on sequence ............................................................................................................... 64

Figure 2-30. Block diagram of BBRX-ADC ............................................................................................... 66

Figure 2-31. Block diagram of BBTX ..........................................................................................................67

Figure 2-32. Block diagram of ETDAC .......................................................................................................67

Figure 2-33. Block diagram of DETADC ................................................................................................... 68

Figure 2-34. Block diagram of APC-DAC .................................................................................................. 69

Figure 2-35. Outlines and dimensions of VFBGA 11mm*11.8mm, 599-ball, 0.9mm pitch package ...... 72

Figure 2-36. Top marking of MT6771V/C .................................................................................................. 72

Figure 2-37. Top marking of MT6771V/W ................................................................................................. 73

Table 2-1. Pin coordinate LPDDR4 ............................................................................................................ 19

Table 2-2. Pin coordinate LPDDR3 ........................................................................................................... 23

Table 2-3. Acronym for pin type ................................................................................................................ 28

Table 2-4. Detailed pin description ........................................................................................................... 28

Table 2-5. Acronym for table of state of pins ............................................................................................ 40

Table 2-6. Absolute maximum ratings for power supply .......................................................................... 41

Table 2-7. Recommended operating conditions for power supply .......................................................... 42

Table 2-8. RTC DC electrical characteristics (DVDD18_IOLT =1.8V) .................................................... 44

Table 2-9. SPI, I2S DC electrical characteristics (DVDD18_IORB =1.8V) ............................................. 44

Table 2-10. I2C0, I2C1, I2C2 DC electrical characteristics (DVDD18_IORB =1.8V) ............................. 44

Table 2-11. I2C3 DC electrical characteristics (DVDD18_IOLB =1.8V) .................................................. 45

Table 2-12. MSDC0 DC electrical characteristics (DVDD28_MSDC0=1.8V) ........................................ 45

Table 2-13. MSDC1 DC electrical characteristics (DVDD28_MSDC1=2.8V/3.3V) ................................ 45

Table 2-14. MSDC1 DC electrical characteristics (DVDD28_MSDC1=1.8V) .......................................... 45

Table 2-15. SIM DC electrical characteristics ........................................................................................... 46

Table 2-16. LPDDR3 AC timing parameter table of external memory interface .................................... 49

Table 2-17. LPDDR4/LPDDR4X AC timing parameter table of external memory interface ................. 50

Table 2-18. SPI AC timing parameters ....................................................................................................... 51

Table 2-19. I2S AC timing parameters ....................................................................................................... 51

Table 2-20. I2C AC timing parameters ..................................................................................................... 52

Table 2-21. MSDC device AC timing parameters of default speed .......................................................... 54

Table 2-22. MSDC device AC timing parameters of high speed ............................................................... 55

Table 2-23. MSDC device AC timing parameters of SDR12/SDR25/SDR50/SDR104 mode ................ 56

Table 2-24. MSDC device AC timing parameters of DDR50 speed mode ............................................... 58

Table 2-25. MSDC device AC timing parameters of HS200 .................................................................... 60

Table 2-26. MSDC device AC timing parameters of HS400 ..................................................................... 61

Table 2-27. SIM AC timing parameters ..................................................................................................... 62

Table 2-28. Mode selection ........................................................................................................................ 63

Table 2-29. Constant tied pins ................................................................................................................... 63

Table 2-30. Baseband downlink specifications ......................................................................................... 66

Table 2-31. BBTX specifications .................................................................................................................67

Table 2-32. ETDAC specifications ............................................................................................................. 68

Table 2-33. DETADC specifications .......................................................................................................... 69

MT6771

LTE-A Smartphone Application Processor

Technical Brief

© 2018 MediaTek Inc.

Page 5 of 73

This document contains information that is proprietary to MediaTek Inc.

Unauthorized reproduction or disclosure of this information in whole or in part is strictly prohibited.

A

Table 2-34. APC-DAC specifications ......................................................................................................... 69

Table 2-35. Definitions of AUXADC channels .......................................................................................... 70

Table 2-36. AUXADC specifications .......................................................................................................... 70

Table 2-37. Clock squarer specifications .................................................................................................... 71

Table 2-38. Temperature sensor specifications ......................................................................................... 71

Table 2-39. Thermal operating specifications ........................................................................................... 73

剩余72页未读,继续阅读

有情之人

- 粉丝: 4

- 资源: 15

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论10