没有合适的资源?快使用搜索试试~ 我知道了~

首页pg153-axi-quad-spi.pdf

pg153-axi-quad-spi.pdf

需积分: 50 50 下载量 44 浏览量

更新于2023-03-03

评论

收藏 2.03MB PDF 举报

当我们在设计中使用Zynq SoC或Zynq UltraScale + MPSoC时,可以有两种方法来实现SPI接口: 使用PS端的SPI控制器(PS端有两个SPI控制器) 在PL端使用配置成标准SPI通信的AXI Quad SPI (QSPI) IP模块 我们可以根据应用的要求来选择使用哪种方法实现SPI控制器。两种SPI的实现方式都支持四种SPI模式,并且都可以作为SPI主设备或SPI从设备。下表列出了它们之间的一些差异:

资源详情

资源评论

资源推荐

AXI Quad SPI v3.2

LogiCORE IP Product Guide

Vivado Design Suite

PG153 April 4, 2018

AXI Quad SPI v3.2 www.xilinx.com 2

PG153 April 4, 2018

Table of Contents

IP Facts

Chapter 1: Overview

Legacy Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

AXI4 Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Core Internal Submodules. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Feature Summary. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13

Unsupported Features. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Licensing and Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Chapter 2: Product Specification

Standards . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Performance. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Resource Utilization. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Port Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Register Space (Legacy and Enhanced Non-XIP Mode) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

Specification Exceptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 44

Chapter 3: Designing with the Core

General Design Guidelines . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Clocking (SPI Clock Phase and Polarity Control) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Resets . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 63

Protocol Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Chapter 4: Design Flow Steps

Customizing and Generating the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

Constraining the Core . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Simulation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Synthesis and Implementation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 93

Chapter 5: Example Design

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 94

Implementing the Example Design . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 95

Send Feedback

AXI Quad SPI v3.2 www.xilinx.com 3

PG153 April 4, 2018

Testing the Example Design on a KC705 Board . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 97

Simulating the Example Design. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 98

Example Programming Sequence . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 99

Chapter 6: Test Bench

Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 101

Checking Results . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 102

Appendix A: Verification, Compliance, and Interoperability

Appendix B: Migrating and Upgrading

Migrating to the Vivado Design Suite. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Upgrading in the Vivado Design Suite . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Appendix C: Debugging

Finding Help on Xilinx.com . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 106

Vivado Design Suite Debug Feature . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 107

Hardware Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Interface Debug . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 108

Appendix D: Additional Resources and Legal Notices

Xilinx Resources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 110

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 111

Please Read: Important Legal Notices . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 114

Send Feedback

AXI Quad SPI v3.2 www.xilinx.com 4

PG153 April 4, 2018 Product Specification

Introduction

The LogiCORE™ IP AXI Quad Serial Peripheral

Interface (SPI) core connects the AXI4 interface to

those SPI slave devices that support the Standard,

Dual, or Quad SPI protocol instruction set. This core

provides a serial interface to SPI slave devices. The

Dual/Quad SPI is an enhancement to the standard

SPI protocol (described in the Motorola M68HC11

data sheet) and provides a simple method for data

exchange between a master and a slave.

Features

• Configurable AXI4 interface; when configured

with an AXI4-Lite interface the core is backward

compatible with version 1.00 of the core (legacy

mode)

•Configurable AXI4 interface for burst mode

operation for the Data Receive Register (DRR)

and the Data Transmit Register (DTR) FIFO

• Configurable eXecute In Place (XIP) mode of

operation

• Connects as a 32-bit slave on either AXI4-Lite or

AXI4 interface

•Configurable SPI modes:

°

Standard SPI mode

°

Dual SPI mode

°

Quad SPI mode

• Programmable SPI clock phase and polarity

• Configurable FIFO depth (16 or 256 element

deep in Dual/Quad/Standard SPI mode) and

fixed FIFO depth of 64 in XIP mode

• Configurable Slave Memories in dual and quad

modes are: Mixed, Micron, Winbond, and

Spansion (Beta Version)

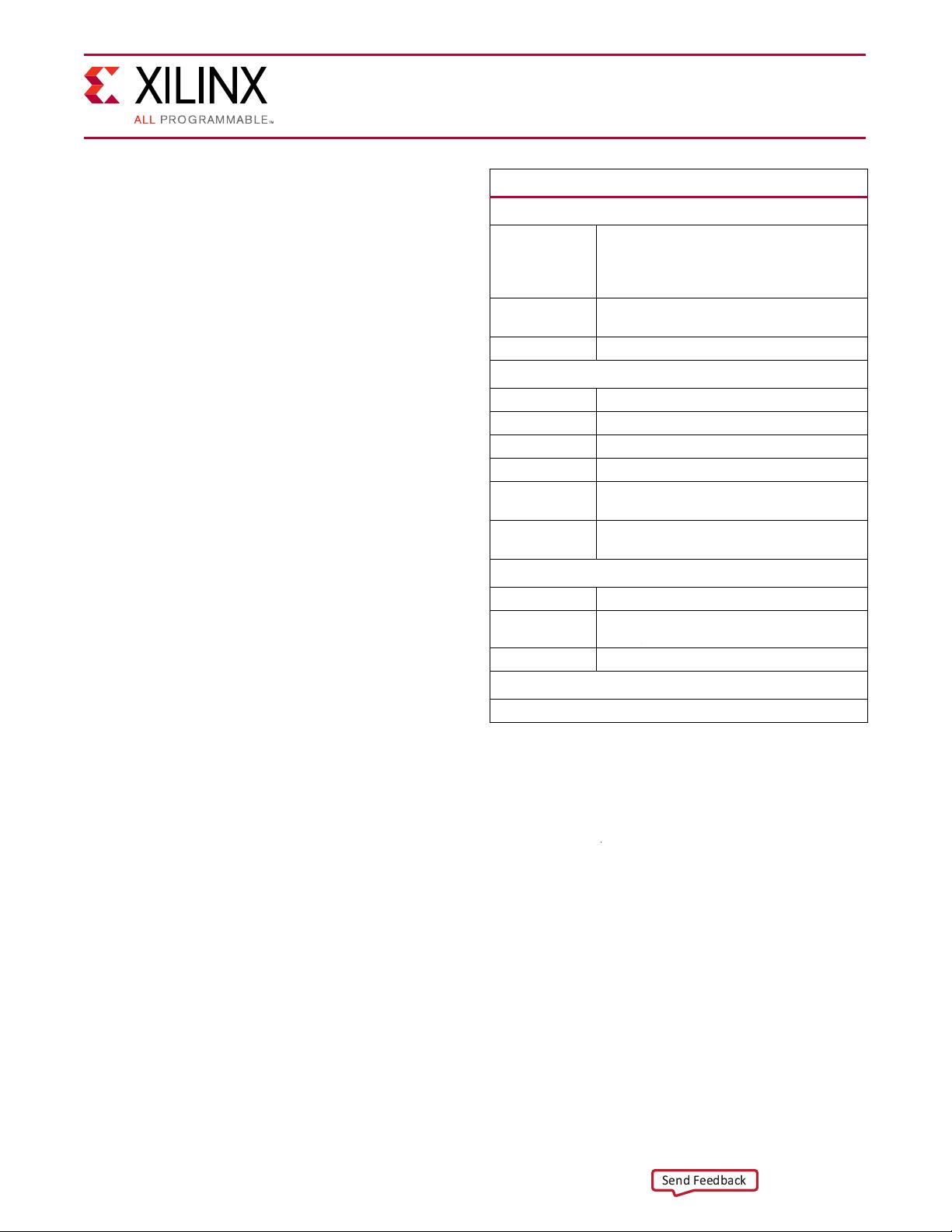

IP Facts

LogiCORE IP Facts Table

Core Specifics

Supported

Device Family

(1)

UltraScale+™

UltraScale™

Zynq®-7000 All Programmable SoC,

7 Series FPGAs

Supported User

Interfaces

AXI4, AXI4-Lite

Resources Performance and Resource Utilization web page

Provided with Core

Design Files VHDL

Example Design VHDL

Test Bench VHDL

Constraints File Xilinx Design Constraints (XDC)

Simulation

Model

Not Provided

Supported

S/W Driver

(2)

Standalone and Linux

Tested Design Flows

(3)

Design Entry Vivado® Design Suite

Simulation

For a list of supported simulators, see the

Xilinx Design Tools: Release Notes Guide

Synthesis Vivado synthesis

Support

Provided by Xilinx at the Xilinx Support web page

Notes:

1. For a complete list of supported devices, see the Vivado IP

catalog.

2. Standalone driver details can be found in the Software

Development Kit (SDK) directory (<install_directory>/SDK/

<release>/data/embeddedsw/doc/xilinx_drivers.htm) on the

Xilinx Wiki page.

3. For the supported versions of the tools, see the

Xilinx Design Tools: Release Notes Guide.

Send Feedback

AXI Quad SPI v3.2 5

PG153 April 4, 2018 www.xilinx.com

Chapter 1

Overview

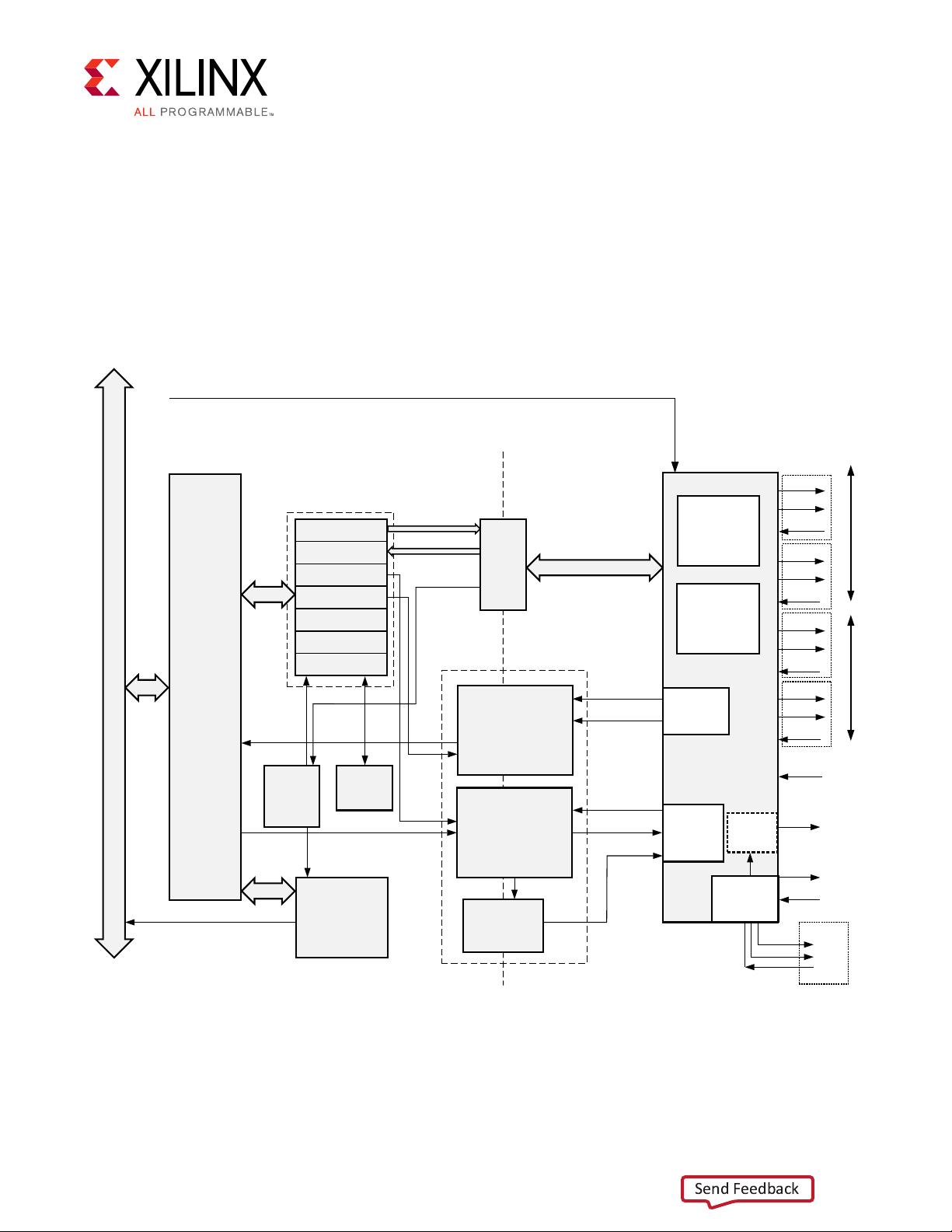

The top-level block diagram for the AXI Quad SPI core when configured with the AXI4-Lite

interface option is shown in Figure 1-1.

X-Ref Target - Figure 1-1

Figure 1-1: AXI Quad SPI Core Top-Level Block Diagram

-4-'

-RXIVJEGI

8<*-*3

6<*-*3

6H)REFPI

8\(EXE

;V)REFPI

6\(EXE

-RXIVVYTX

'SRXVSPPIV

-4-)6

-4-76

(+-)6

6\3''6IK

8\3''6IK

74-776

74-(66

74-(86

74-76

74-'6

3''

'SYRXIV

'('

&PSGO

6IKMWXIV1SHYPI

8\

ERH

6\

'SYRXIV

74-8VERWJIV

(SRI

74-7)013(*

74-<JIV(SRI

78%6894

&PSGO

'1('SQTEVI

ERH

&ILEZMSV

7MKREPW

WGOCS

WGOCX

WGOCM

MSCS

MSCX

MSCM

MSCS

MSCX

MSCM

MSCS

MSCX

MSCM

MSCS

MSCX

MSCM

WTMWIP

I\XCWTMCGPO

74-'PO

+IRIVEXSV

74-

6IGIMZI

(EXE0SKMG

74-

8VERWQMX

(EXE0SKMG

74-1SHI

0SKMG

74-1SHI

ERH0SKMG

FYWMTCHEXE(86

-4FYWCHEXE

(66

WWCS

WWCX

WWCM

3RP]MR5YEH74-1SHI 7XH(YEP5YEH74-1SHI

<

%<-5YEH74-&PSGO(MEKVEQ

74-'0/

(SQEMR

%<-'0/

(SQEMR

%<-

Send Feedback

剩余113页未读,继续阅读

不想睡觉的玛卡巴卡

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0