没有合适的资源?快使用搜索试试~ 我知道了~

首页ug1292-ultrafast-timing-closure-quick-reference(中文).pdf

资源详情

资源评论

资源推荐

根据《UltraFAST 设计方法指南(适用于 Vivado Design Suite)》 (UG949) 中

的建议,本快捷参考指南提供了以下简化的分步骤快速收敛时序流程:

初始设计检查:在实现设计前审核资源利用率、逻辑层次和时序约束。

时序基线:在每个实现步骤后检查并解决时序违规,从而帮助布线后收敛

时序。

时序违规解决:识别建立时间违规或保持时间违规的根源,并解决时序违规。

Failfast 报告

基于 Tcl 的 Failfast 报告总结关于设计与约束的关键信息,有助于您迅速识别并解

决常见的实现和性能问题。默认条件下该报告分析完整设计并输出一个表,在表中

将每个分析指标与典型的指南值做对比。将每个不符合指南值的指标标记为

REVIEW。报告包括下列部分:

设计特性

关键时钟方法检查

根据目标 Fmax 进行保守的逻辑层次评估

从 Vivado® 工具 2018.1 版开始,report_failfast 脚本能默认安装并以下列方式

调用:

xilinx::designutils::report_failfast

从 SDx™ 工具 2018.2 版开始,report_failfast 在编译流程中使用 xocc –R 1 或

xocc –R 2 调用。

如需了解更多有关 report_failfast 的信息,请参阅 Failfast 报告概览(第 10

页)。

虽然在赛灵思器件上实现设计是一个自动化程度相当高的任务,获得较高性能并解

决时序或布线违规带来的编译问题,是一项复杂且耗时的工作。根据简单的日志消

息或由工具生成的实现后时序报告可能难以确定故障原因。因此有必要采用逐步设

计开发和编译方法,包括审核中间结果以确保设计能进行到下一个实现步骤。

第一步是确保所有的初始设计检查都已经完成。在下列层次查看这些检查:

每个由定制 RTL 构成的内核或由 Vivado HLS 生成的内核

注意:检查目标时钟频率约束是否现实。

每个与子系统对应的主要层级,例如有多个内核、IP 块和连接逻辑的 Vivado

IP 集成器原理图

包括所有主要功能和层级、I/O 接口、完整时钟电路和物理及时序约束的完整

设计

如果设计使用布局规划约束,如超级逻辑区域 (SLR) 分配或分配给 Pblock 的逻

辑,为每个物理约束审核估算的资源占用,确保符合资源占用指南。在 Failfast 报

告中查看默认指南。使用下列命令生成报告:

report_utilization –pblocks <pblockName>

report_failfast –pblock <pblockName>

report_failfast [–slr SLR

n

| -by_slr]

UG1292 (v2018.2) 2018 年 9 月 28 日

1

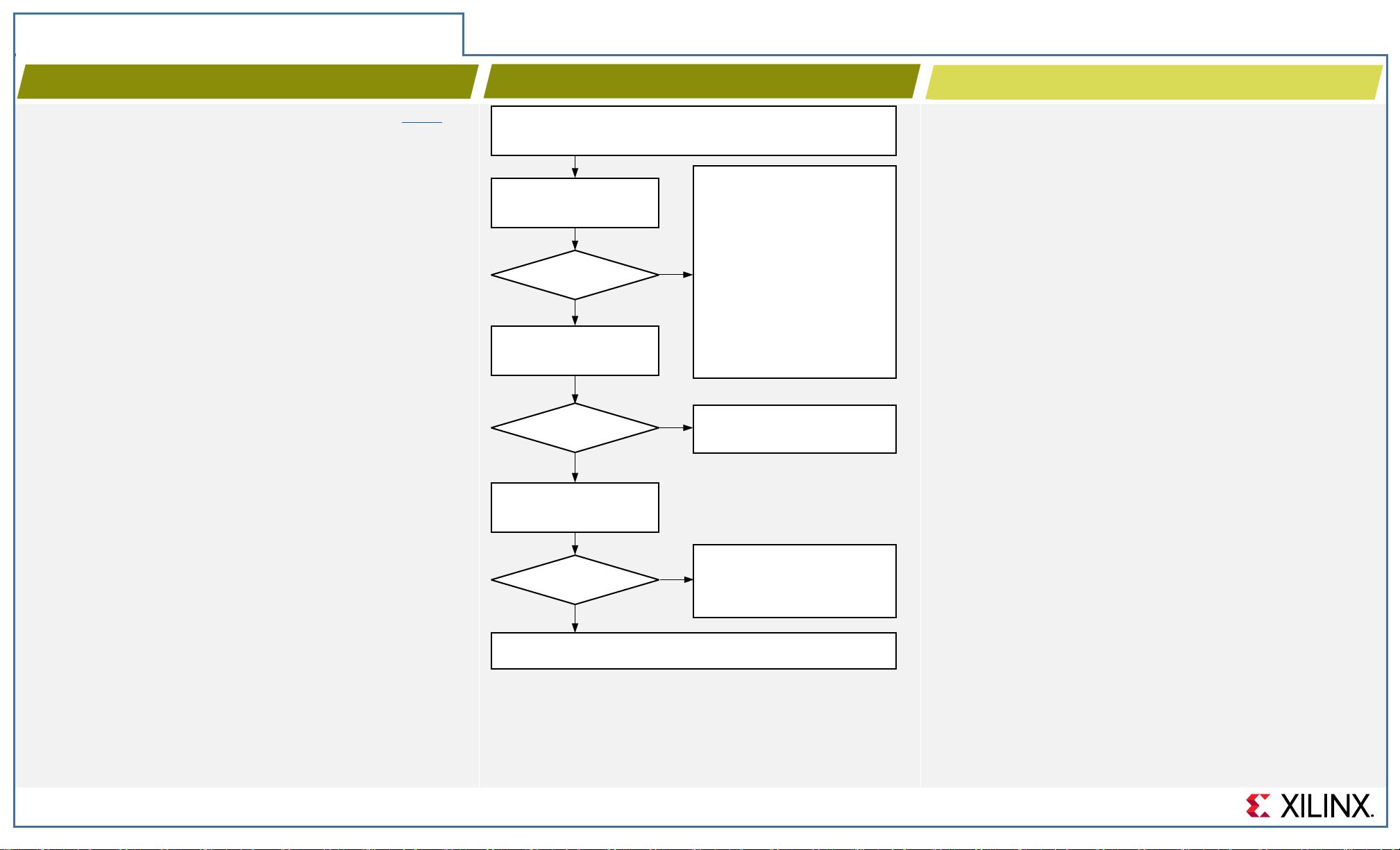

Open the synthesized design checkpoint (DCP) or the post-opt_design DCP

(if available)

Run report_failfast

Review Check Timing section in

report_timing_summary

Run report_methodology

Proceed to design implementation (logic optimization, placement, routing)

Fix methodology checks that impact

timing closure (Fmax)

Create missing clock constraints to

eliminate unconstrained internal

endpoints and avoid timing loops

Review the detailed reports to identify

the design characteristics or

constraints to improve:

● Estimated device and SLR Pblock

resource utilization

● Constraints preventing optimizations

● Control signals and average fanout

● Clock tree and clock domain

crossing constraints

● High logic levels given the target

frequency

Clean report?

Clean report?

Clean report?

Yes

Yes

Yes

No

No

No

X21574-091818

引言

初始设计检查

-

详细介绍

初始设计检查流程

初始设计检查详细介绍

UltraFast 设计方法时序收敛快捷参考指南 (UG1292)

何瑞毅

- 粉丝: 1

- 资源: 6

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- stc12c5a60s2 例程

- Android通过全局变量传递数据

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0