Xilinx FPGA底层资源架构与设计规范底层资源架构与设计规范

题主最近开始接触和FPGA的方案验证相关的工作内容,需要把握FPGA内部资源的详细信息,所以又仔细查看

了官方的器件手册。这一次给大家分享的内容主要涉及Xilinx FPGA内的CLBs,SelecTIO和Clocking资源,适合

对FPGA设计有时序要求,却还没有足够了解的朋友。

参考器件上,虽然一些专用的资源都集中在高端的FPGA型号中,不过题主想了想,还是把它们放在该系列后续的文章中吧。

下文中的举证皆来自Spartan6器件文档,所以也不会超出Spartan6涵盖内容。

传统的FPGA内部资源分类作三类,可配置逻辑模块(Configurable Logic Block)、输入输出模块(InputOutput Block)和内

部布线资源(Interconnect)三个部分,这些大家都知道的。随着FPGA的发展,为了满足对信号处理和片上储存的需要,又

在前三类基础上增加了块RAM(BRAM)、时钟管理单元和硬件乘法器,之后又在部分系列里增加了PPC和高速串行输入与

输出等等。

下文将要提到的CLB、SelecTIO和Clocking资源里,SelecTIO资源是比较丰富的一类,所以在顺序上把它放在最后。

正文:

首先说说CLB吧,它是一类最重要,其实也是最易于使用的结构。Xilinx把尽可能多的资源配置接口开放给用户,但是出于控

制开发周期,并且提高系统稳定性的考虑,CLB不是其中之一,它的配置方案几乎全部由IDE实现过程智能分配,用户可以约

束特殊Slice的位置,但很少有这种必要,交给IDE来完成会更加有效。

来看看它的结构(有一些图片资料不好找,后期整合的时候会补全):

① CLB资源会根据FPGA的尺寸被内部时钟网络分割成若干个区域,一般每个区域是40个CLB单元高度;

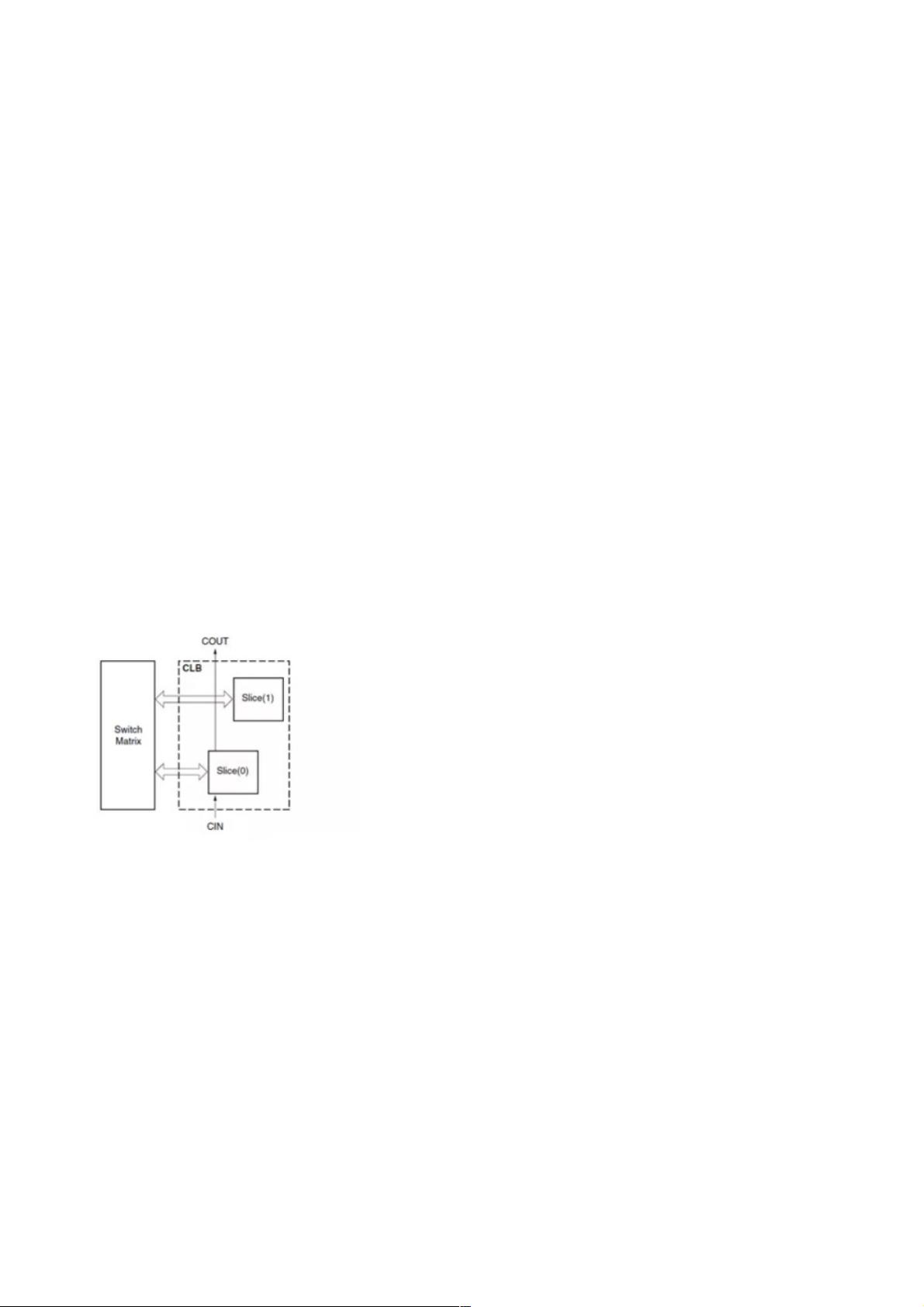

② 每个CLB连接到一个开关矩阵来接入全局布线矩阵;

③ 一个CLB单元包含 一对Slice单元(两个Slice无直接连接,并且在CLB间成列分布,每个纵列的Slice有一条独立的进位

链);

④ 一个CLB中下方的Slice记为Slice0,上方的记为Slice1;

评论0