没有合适的资源?快使用搜索试试~ 我知道了~

首页规格书LVDS芯片规格书

资源详情

资源评论

资源推荐

Topmicro Electronics Corp. reserves the right to make changes without further notice to any products herein to improve reliability,

function or design. Topmicro Electronics Corp. does not assume any liability arising out of the application or use of any product or

circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Topmicro Electronics Corp.

products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body,

or othe r a pplications i ntended to sup port or sustain life, or for an y other ap plication in which th e failu re of the Topmicro

Electronics Corp. product could create a si tuation whe re personal i njury or d eath may occu r. Should Bu yer p urchase or use

Topmicro Electronics Corp. products for any such unintended or unauthorized application, Buyer shall indemnify and hold Topmicro

Electronics Corp. and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages,

and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated

with such unintended or unauthorized use, even if such claim alleges that Topmicro Electronics Corp. was negligent regarding the

design or manufacture of the part.

User Guide — TH103-G V2.5

Topmicro Electronics Corp.

NON-DISCLOSURE AGREEMENT REQUIRED

1

High Speed 10-bits LVDS Transmitter

TH103-G V2.5

User Guide — TH103-G V2.5

Topmicro Electronics Corp.

NON-DISCLOSURE AGREEMENT REQUIRED 2

Section 1 Introduction

1.1 Overview

The TH103-G LVDS transmitter supports transmission between the host and the flat panel display up to

SXGA+ resolutions. The transmitter converts 32 bits (10-bits/color, 2 dummy bits) of CMOS/TTL data

and 3 control bits into 5 LVDS (Low Voltage Differential Signal) data streams. At a maximum input clock

rate of 135MHz, each LVDS differential data pair speed is 945Mbps, providing a total throughput of

4.7Gbps. The transmitter can be configured to input clock rising edge or falling edge strobe through an

external pin.

1.2 Features

The TH103-G includes the following distinctive features:

• Support 8MHz to 135MHz clock rates for NTSC to SXGA+ resolution

• Up to 4.7Gbps bandwidth

• PLL requires no external components

• Cycle-to-cycle jitter rejection

• Programmable data and control strobe select

• Reduced swing LVDS supported

• Power down mode supported

• Compatible with THine THC63LVD103

• Single 3.3V CMOS design

• 64-pin LQFP (Pb Free, compliant to JEDEC/IPC J-STD-006)

User Guide — TH103-G V2.5

Topmicro Electronics Corp.

NON-DISCLOSURE AGREEMENT REQUIRED 3

Section 2 Overview

2.1 Block Diagram

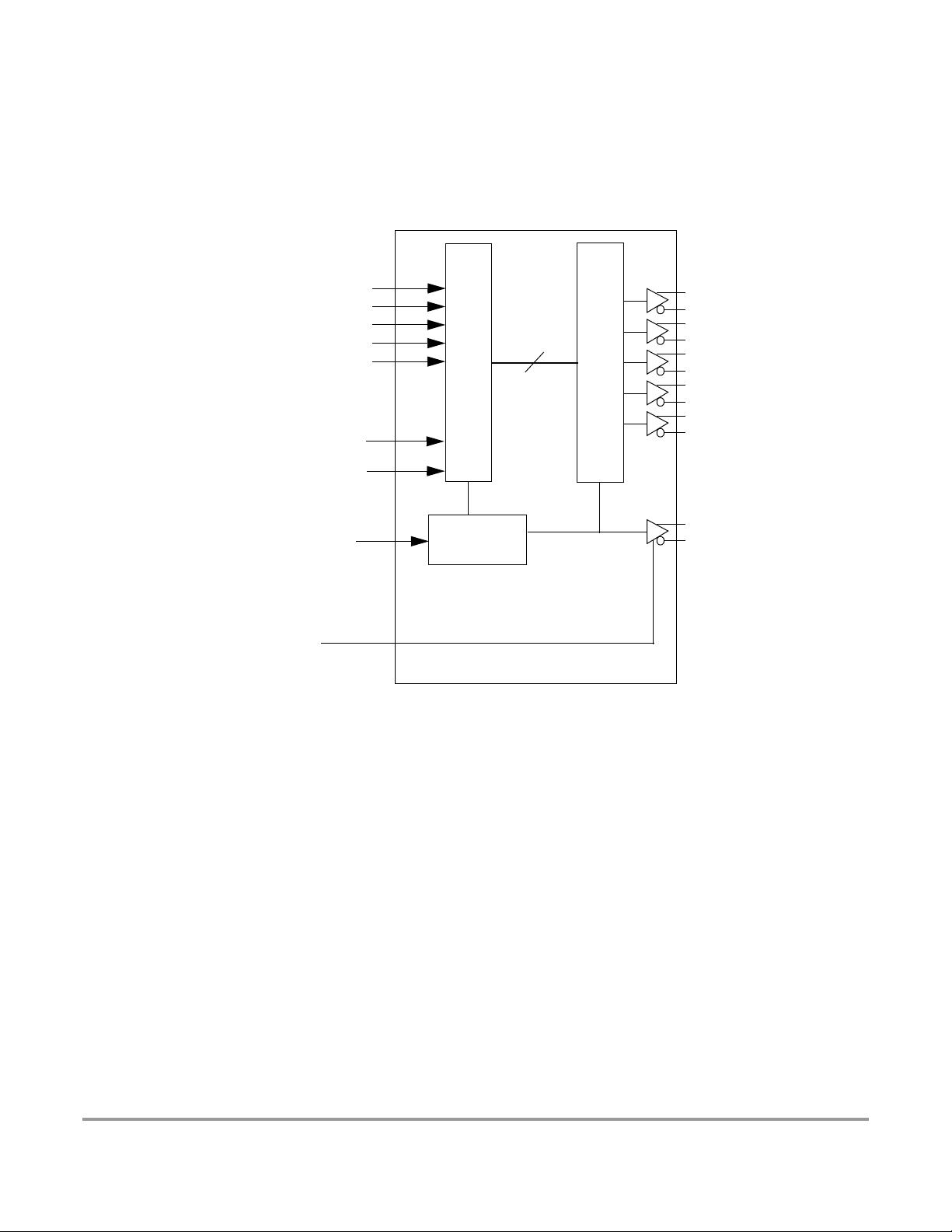

Figure 2-1 Block Diagram of LVDS Transmitter TH103-G

CLKIN

TA0 - TA6

TB0 - TB6

TC0 - TC6

TTL INPUT LATCH

PLL

TD0 - TD6

TE0 - TE6

PWR_UP

DATA SERIALIZER

35

TA+/-

TB+/-

TC+/-

TD+/-

TE+/-

CLK+/-

RS

R_F

剩余14页未读,继续阅读

gns001

- 粉丝: 0

- 资源: 4

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1