没有合适的资源?快使用搜索试试~ 我知道了~

首页MT29F16G08,MT29F32G08 nandflash器件资料

MT29F16G08,MT29F32G08 nandflash器件资料

Micron Technology, Inc.公司,2G/4G字节,8位接口,nandflash器件资料,pdf格式

资源详情

资源评论

资源推荐

NAND Flash Memory

MT29F16G08ABACA, MT29F16G08ABCCB, MT29F32G08AFACA

Features

•

Open NAND Flash Interface (ONFI) 2.2-compliant

1

•

Single-level cell (SLC) technology

•

Organization

–

Page size x8: 4320 bytes (4096 + 224 bytes)

–

Block size: 128 pages (512K + 28K bytes)

–

Plane size: 2 planes x 2048 blocks per plane

–

Device size: 16Gb: 4096 blocks;

32Gb: 8192 blocks;

•

Synchronous I/O performance

–

Up to synchronous timing mode 5

–

Clock rate: 10ns (DDR)

–

Read/write throughput per pin: 200 MT/s

•

Asynchronous I/O performance

–

Up to asynchronous timing mode 5

–

t

RC/

t

WC: 20ns (MIN)

•

Array performance

–

Read page: 35µs (MAX)

–

Program page: 300µs (TYP)

–

Erase block: 700µs (TYP)

•

Operating Voltage Range

–

V

CC

: 2.7–3.6V

–

V

CCQ

: 2.7–3.6V, 1.7-1.9V

•

Command set: ONFI NAND Flash Protocol

•

Advanced Command Set

–

Program cache

–

Read cache sequential

–

Read cache random

–

One-time programmable (OTP) mode

–

Multi-plane commands

–

Multi-LUN operations

–

Read unique ID

–

Copyback

•

First block (block address 00h) is valid when ship-

ped from factory. For minimum required ECC, see

Error Management (page 95).

•

RESET (FFh) required as first command after power-

on

•

Operation status byte provides software method for

detecting

–

Operation completion

–

Pass/fail condition

–

Write-protect status

•

Data strobe (DQS) signals provide a hardware meth-

od for synchronizing data DQ in the synchronous

interface

•

Copyback operations supported within the plane

from which data is read

•

Quality and reliability

–

Data retention: JESD47G compliant; see qualifica-

tion report

–

Endurance: 100,000 PROGRAM/ERASE cycles

•

Operating temperature:

–

Commercial: 0°C to +70°C

–

Industrial (IT): –40ºC to +85ºC

•

Package

–

48-pin TSOP

–

100-ball BGA

Note:

1. The ONFI 2.2 specification is available at

www.onfi.org.

Micron Confidential and Proprietary Advance

‡

16Gb, 32Gb Asynchronous/Synchronous NAND

Features

PDF: 09005aef83fccd10

m72a_async_sync_nand.pdf – Rev. A 6/10 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

‡Products and specifications discussed herein are for evaluation and reference purposes only and are subject to change by

Micron without notice. Products are only warranted by Micron to meet Micron's production data sheet specifications.

Draft: 06/30/10

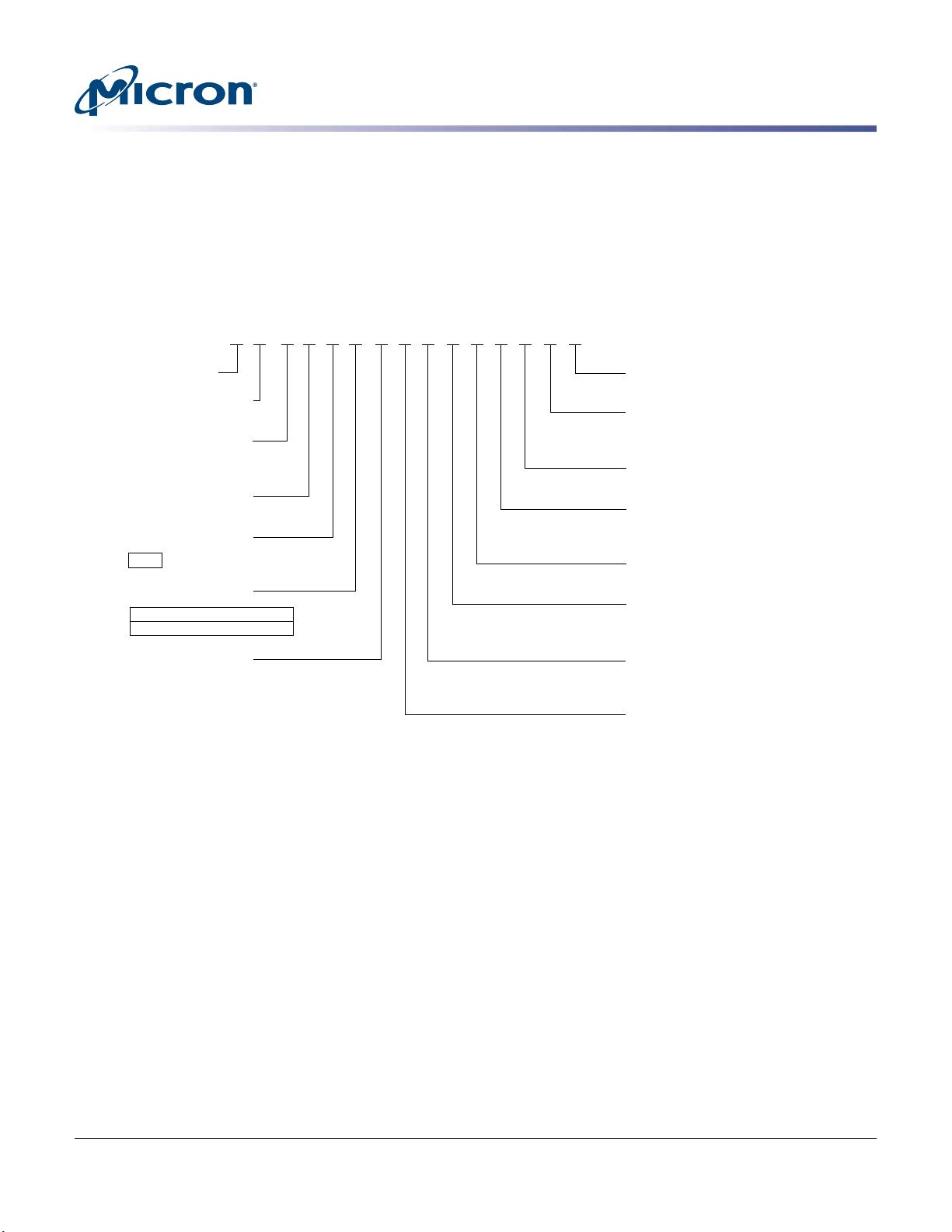

Part Numbering Information

Micron NAND Flash devices are available in different configurations and densities. Verify valid part numbers by

using Micron’s part catalog search at www.micron.com. To compare features and specifications by device type,

visit www.micron.com/products. Contact the factory for devices not found.

Figure 1: Part Numbering

MT 29F 16G 08 A B A C A WP ES :C

Micron Technology

NAND Flash

29F = NAND Flash memory

Density

16G = 16Gb

32G = 32Gb

Device Width

08 = 8 bits

Level

Bit/Cell

A 1-bit

Classification

Die # of CE# # of R/B# I/O

B 1 1 1 Common

F 2 2 2 Common

Operating Voltage Range

A = V

CC

: 3.3V (2.7–3.6V), V

CCQ

: 3.3V (2.7–3.6V)

C = V

CC

: 3.3V (2.7–3.6V), V

CCQ

: 1.8V (1.7–2.95V)

Design Revision

C = Third revision

Production Status

Blank = Production

ES = Engineering sample

Reserved for Future Use

Blank

Operating Temperature Range

Blank = Commercial (0°C to +70°C)

IT = Industrial (–40°C to +85°C)

Speed Grade (synchronous mode only)

-10 = 200 MT/s

Package Code

H1 = 100-ball VBGA 12mm x 18mm x 1.4mm

1

WP = 48-pin TSOP

1

(CPL)

Interface

A = Async only

B = Sync/Async

Generation Feature Set

C = Third set of device features

Note:

1. Pb-free package.

Micron Confidential and Proprietary

Advance

16Gb, 32Gb Asynchronous/Synchronous NAND

Features

PDF: 09005aef83fccd10

m72a_async_sync_nand.pdf – Rev. A 6/10 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Draft: 06/30/10

Contents

General Description ......................................................................................................................................... 9

Asynchronous and Synchronous Signal Descriptions ......................................................................................... 9

Signal Assignments ......................................................................................................................................... 11

Package Dimensions ...................................................................................................................................... 13

Architecture ................................................................................................................................................... 15

Device and Array Organization ....................................................................................................................... 16

Bus Operation – Asynchronous Interface ........................................................................................................ 19

Asynchronous Enable/Standby ................................................................................................................... 19

Asynchronous Bus Idle ............................................................................................................................... 19

Asynchronous Commands .......................................................................................................................... 20

Asynchronous Addresses ............................................................................................................................ 21

Asynchronous Data Input ........................................................................................................................... 22

Asynchronous Data Output ........................................................................................................................ 23

Write Protect .............................................................................................................................................. 24

Ready/Busy# .............................................................................................................................................. 24

Bus Operation – Synchronous Interface ........................................................................................................... 29

Synchronous Enable/Standby ..................................................................................................................... 30

Synchronous Bus Idle/Driving .................................................................................................................... 30

Synchronous Commands ........................................................................................................................... 31

Synchronous Addresses .............................................................................................................................. 32

Synchronous DDR Data Input ..................................................................................................................... 33

Synchronous DDR Data Output .................................................................................................................. 34

Write Protect .............................................................................................................................................. 36

Ready/Busy# .............................................................................................................................................. 36

Device Initialization ....................................................................................................................................... 37

Activating Interfaces ....................................................................................................................................... 38

Activating the Asynchronous Interface ........................................................................................................ 38

Activating the Synchronous Interface .......................................................................................................... 38

Command Definitions .................................................................................................................................... 40

Reset Operations ............................................................................................................................................ 42

RESET (FFh) ............................................................................................................................................... 42

SYNCHRONOUS RESET (FCh) .................................................................................................................... 43

RESET LUN (FAh) ....................................................................................................................................... 44

Identification Operations ................................................................................................................................ 45

READ ID (90h) ............................................................................................................................................ 45

READ ID Parameter Tables ............................................................................................................................. 46

READ PARAMETER PAGE (ECh) ...................................................................................................................... 47

Parameter Page Data Structure Tables ............................................................................................................. 48

READ UNIQUE ID (EDh) ................................................................................................................................ 53

Configuration Operations ............................................................................................................................... 54

SET FEATURES (EFh) ................................................................................................................................. 54

GET FEATURES (EEh) ................................................................................................................................. 55

Status Operations ........................................................................................................................................... 59

READ STATUS (70h) ................................................................................................................................... 60

READ STATUS ENHANCED (78h) ............................................................................................................... 61

Column Address Operations ........................................................................................................................... 62

CHANGE READ COLUMN (05h-E0h) .......................................................................................................... 62

CHANGE READ COLUMN ENHANCED (06h-E0h) ....................................................................................... 63

CHANGE WRITE COLUMN (85h) ................................................................................................................ 64

CHANGE ROW ADDRESS (85h) ................................................................................................................... 65

Micron Confidential and Proprietary

Advance

16Gb, 32Gb Asynchronous/Synchronous NAND

PDF: 09005aef83fccd10

m72a_async_sync_nand.pdf – Rev. A 6/10 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Draft: 06/30/10

Read Operations ............................................................................................................................................. 67

READ MODE (00h) ..................................................................................................................................... 69

READ PAGE (00h-30h) ................................................................................................................................ 70

READ PAGE CACHE SEQUENTIAL (31h) ..................................................................................................... 71

READ PAGE CACHE RANDOM (00h-31h) .................................................................................................... 72

READ PAGE CACHE LAST (3Fh) .................................................................................................................. 74

READ PAGE MULTI-PLANE (00h-32h) ........................................................................................................ 75

Program Operations ....................................................................................................................................... 77

PROGRAM PAGE (80h-10h) ........................................................................................................................ 77

PROGRAM PAGE CACHE (80h-15h) ............................................................................................................ 79

PROGRAM PAGE MULTI-PLANE 80h-11h ................................................................................................... 81

Erase Operations ............................................................................................................................................ 83

ERASE BLOCK (60h-D0h) ............................................................................................................................ 83

ERASE BLOCK MULTI-PLANE (60h-D1h) .................................................................................................... 84

Copyback Operations ..................................................................................................................................... 85

COPYBACK READ (00h-35h) ....................................................................................................................... 86

COPYBACK PROGRAM (85h–10h) ............................................................................................................... 87

COPYBACK READ MULTI-PLANE (00h-32h) ............................................................................................... 87

COPYBACK PROGRAM MULTI-PLANE (85h-11h) ........................................................................................ 88

One-Time Programmable (OTP) Operations .................................................................................................... 89

PROGRAM OTP PAGE (80h-10h) ................................................................................................................. 90

PROTECT OTP AREA (80h-10h) ................................................................................................................... 91

READ OTP PAGE (00h-30h) ......................................................................................................................... 92

Multi-Plane Operations .................................................................................................................................. 93

Multi-Plane Addressing .............................................................................................................................. 93

Interleaved Die (Multi-LUN) Operations ......................................................................................................... 94

Error Management ......................................................................................................................................... 95

Output Drive Impedance ................................................................................................................................ 96

AC Overshoot/Undershoot Specifications ....................................................................................................... 99

Synchronous Input Slew Rate ........................................................................................................................ 100

Output Slew Rate ........................................................................................................................................... 101

Electrical Specifications ................................................................................................................................. 102

Electrical Specifications – DC Characteristics and Operating Conditions (Asynchronous) ................................. 104

Electrical Specifications – DC Characteristics and Operating Conditions (Synchronous) .................................. 104

Electrical Specifications – DC Characteristics and Operating Conditions (V

CCQ

) ............................................... 104

Electrical Specifications – AC Characteristics and Operating Conditions (Asynchronous) ................................. 106

Electrical Specifications – AC Characteristics and Operating Conditions (Synchronous) ................................... 108

Electrical Specifications – Array Characteristics .............................................................................................. 111

Asynchronous Interface Timing Diagrams ...................................................................................................... 112

Synchronous Interface Timing Diagrams ........................................................................................................ 123

Revision History ............................................................................................................................................ 145

Rev. A – 6/10 ............................................................................................................................................. 145

Micron Confidential and Proprietary

Advance

16Gb, 32Gb Asynchronous/Synchronous NAND

PDF: 09005aef83fccd10

m72a_async_sync_nand.pdf – Rev. A 6/10 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Draft: 06/30/10

List of Figures

Figure 1: Part Numbering ................................................................................................................................ 2

Figure 2: 48-Pin TSOP Type 1 (Top View) ....................................................................................................... 11

Figure 3: 100-Ball BGA (Ball-Down, Top View) ................................................................................................ 12

Figure 4: 48-Pin TSOP – Type 1 CPL (Package Code: WP) ................................................................................ 13

Figure 5: 100-Ball VBGA – 12mm x 18mm (Package Code: H1) ......................................................................... 14

Figure 6: NAND Flash Die (LUN) Functional Block Diagram ........................................................................... 15

Figure 7: Device Organization for Single-Die Package (TSOP/BGA) ................................................................. 16

Figure 8: Device Organization for Two-Die Package (TSOP) ............................................................................ 17

Figure 9: Array Organization per Logical Unit (LUN) ....................................................................................... 18

Figure 10: Asynchronous Command Latch Cycle ............................................................................................ 20

Figure 11: Asynchronous Address Latch Cycle ................................................................................................ 21

Figure 12: Asynchronous Data Input Cycles ................................................................................................... 22

Figure 13: Asynchronous Data Output Cycles ................................................................................................. 23

Figure 14: Asynchronous Data Output Cycles (EDO Mode) ............................................................................. 24

Figure 15: READ/BUSY# Open Drain ............................................................................................................. 25

Figure 16:

t

Fall and

t

Rise (V

CCQ

= 2.7-3.6V) ...................................................................................................... 26

Figure 17:

t

Fall and

t

Rise (V

CCQ

= 1.7-1.95V) .................................................................................................... 26

Figure 18: IOL vs Rp (V

CCQ

= 2.7-3.6V) ............................................................................................................ 27

Figure 19: IOL vs Rp (V

CCQ

= 1.7-1.95V) .......................................................................................................... 27

Figure 20: TC vs Rp ........................................................................................................................................ 28

Figure 21: Synchronous Bus Idle/Driving Behavior ......................................................................................... 31

Figure 22: Synchronous Command Cycle ....................................................................................................... 32

Figure 23: Synchronous Address Cycle ........................................................................................................... 33

Figure 24: Synchronous DDR Data Input Cycles ............................................................................................. 34

Figure 25: Synchronous DDR Data Output Cycles ........................................................................................... 36

Figure 26: R/B# Power-On Behavior ............................................................................................................... 37

Figure 27: Activating the Synchronous Interface ............................................................................................. 39

Figure 28: RESET (FFh) Operation ................................................................................................................. 42

Figure 29: SYNCHRONOUS RESET (FCh) Operation ....................................................................................... 43

Figure 30: RESET LUN (FAh) Operation ......................................................................................................... 44

Figure 31: READ ID (90h) with 00h Address Operation .................................................................................... 45

Figure 32: READ ID (90h) with 20h Address Operation .................................................................................... 45

Figure 33: READ PARAMETER (ECh) Operation .............................................................................................. 47

Figure 34: READ UNIQUE ID (EDh) Operation ............................................................................................... 53

Figure 35: SET FEATURES (EFh) Operation .................................................................................................... 55

Figure 36: GET FEATURES (EEh) Operation ................................................................................................... 55

Figure 37: READ STATUS (70h) Operation ...................................................................................................... 61

Figure 38: READ STATUS ENHANCED (78h) Operation .................................................................................. 61

Figure 39: CHANGE READ COLUMN (05h-E0h) Operation ............................................................................. 62

Figure 40: CHANGE READ COLUMN ENHANCED (06h-E0h) Operation ......................................................... 63

Figure 41: CHANGE WRITE COLUMN (85h) Operation ................................................................................... 64

Figure 42: CHANGE ROW ADDRESS (85h) Operation ..................................................................................... 66

Figure 43: READ PAGE (00h-30h) Operation ................................................................................................... 70

Figure 44: READ PAGE CACHE SEQUENTIAL (31h) Operation ........................................................................ 71

Figure 45: READ PAGE CACHE RANDOM (00h-31h) Operation ....................................................................... 73

Figure 46: READ PAGE CACHE LAST (3Fh) Operation ..................................................................................... 74

Figure 47: READ PAGE MULTI-PLANE (00h-32h) Operation ........................................................................... 76

Figure 48: PROGRAM PAGE (80h-10h) Operation ........................................................................................... 78

Figure 49: PROGRAM PAGE CACHE (80h–15h) Operation (Start) .................................................................... 80

Figure 50: PROGRAM PAGE CACHE (80h–15h) Operation (End) ..................................................................... 80

Micron Confidential and Proprietary

Advance

16Gb, 32Gb Asynchronous/Synchronous NAND

PDF: 09005aef83fccd10

m72a_async_sync_nand.pdf – Rev. A 6/10 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

© 2010 Micron Technology, Inc. All rights reserved.

Draft: 06/30/10

剩余144页未读,继续阅读

edb430

- 粉丝: 1

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论3