没有合适的资源?快使用搜索试试~ 我知道了~

首页基于 SystemVerilog语言的验证方法学

基于 SystemVerilog语言的验证方法学

文章主要介绍《VMM for SystemVerilog》一书描述的如何利用SystemVerilog语言,采用验证方法学以及验证库开发出先进验证环境.

资源详情

资源评论

资源推荐

SYNOPSYS 基于 SystemVerilog 语言的验证方法学

前 言

文章主要介绍

《

VMM for SystemVerilog

》

一书描述的如何利用 SystemVerilog 语言,采

用验证方法学以及验证库开发出先进验证环境。文章分为四部分,第一部分概述了用

SystemVerilog 语言验证复杂 SoC 的基本方法。第二部分主要介绍使用先进验证技术进行

RTL 验证并定义一个能在项目之间进行验证单元重用的分层验证平台结构。第三部分将涉

及到系统级验证,包括 SystemVerilog 与 SystemC 交互等方面。当与一个合适方法相结

合,SystemVerilog 提供了建立一个完整 RTL 以及系统级(ESL)验证环境需要的所有结

构及特性。同时完全支持与 System C 或与一个以 C 为基础的软件测试环境交互。第四部

分讨论验证所采用的验证策略,VMM 方法学,以及利用

《

VMM for SystemVerilog

》

中定

义的标准库来支持方法学。这些库涉及到文章中讨论的基本方法,XVC,XVC 管理器,

软件验证等方面。

采用

《

VMM for SystemVerilog

》

书中提供的方法学是应对目前复杂芯片而带来验证

挑战的有用方法。此书基于业界多年领先的Synopsys公司以及ARM公司专家,及其客户

提供经验编写而成,因而对开发团队有益。采用此方法学将提高验证效率,为一次投片成

功提供更大可能。此文章全面介绍关于用SystemVerilog验证复杂SoC。更多书中信息可在

www.vmm-sv.com中找到。事实上业界已经认可VMM验证方法,此书日文版已经发行,与

VMM相关书籍也已诞生,除Synopsys之外的几个EDA厂家也提供相关练习,甚至在

California Extension Santa Cruz大学开展了VMM课程。

http://www.vmm-sv.org/提供了更

多业界对VMM验证方法支持信息。

- 1 -

SYNOPSYS 基于 SystemVerilog 语言的验证方法学

目 录

1 SystemVerilog验证方法学介绍..................................................................................... 4

1.1 验证面临挑战.......................................................................................................... 4

1.2 SystemVerilog验证技术.......................................................................................... 4

1.3 产生带约束随机仿真.............................................................................................. 4

1.4 覆盖率驱动验证...................................................................................................... 5

1.5 断言.......................................................................................................................... 6

1.6 小结.......................................................................................................................... 8

2 SystemVerilog验证方法学:RTL................................................................................. 8

2.1 分层测试平台结构.................................................................................................. 8

2.2 自顶向下和自底向上.............................................................................................. 9

2.3 结果检查................................................................................................................ 10

2.4 覆盖率驱动验证执行............................................................................................ 10

2.5 使用形式分析........................................................................................................ 11

2.6 产生可重用验证IP................................................................................................ 11

2.7 小结........................................................................................................................ 12

3 SystemVerilog验证方法学:ESL ............................................................................... 12

3.1 系统级验证介绍.................................................................................................... 12

3.2 可扩展的验证单元................................................................................................ 13

3.3 XVC管理器(XVC manager)................................................................................. 13

3.4 系统级验证环境.................................................................................................... 14

3.5 事务级模型(Transaction-level models)........................................................... 16

3.6 小结........................................................................................................................ 17

4 SystemVerilog验证方法学:采用VMM..................................................................... 17

4.1 采用验证方法学.................................................................................................... 17

4.2 VMM提供四类库.................................................................................................. 18

4.2.1 VMM标准库................................................................................................... 18

4.2.2 VMM Checker库 ............................................................................................ 19

4.2.3 XVC标准库 .................................................................................................... 20

4.2.4 软件测试架构................................................................................................. 21

4.3 小结........................................................................................................................ 21

结束语:........................................................................................................................... 21

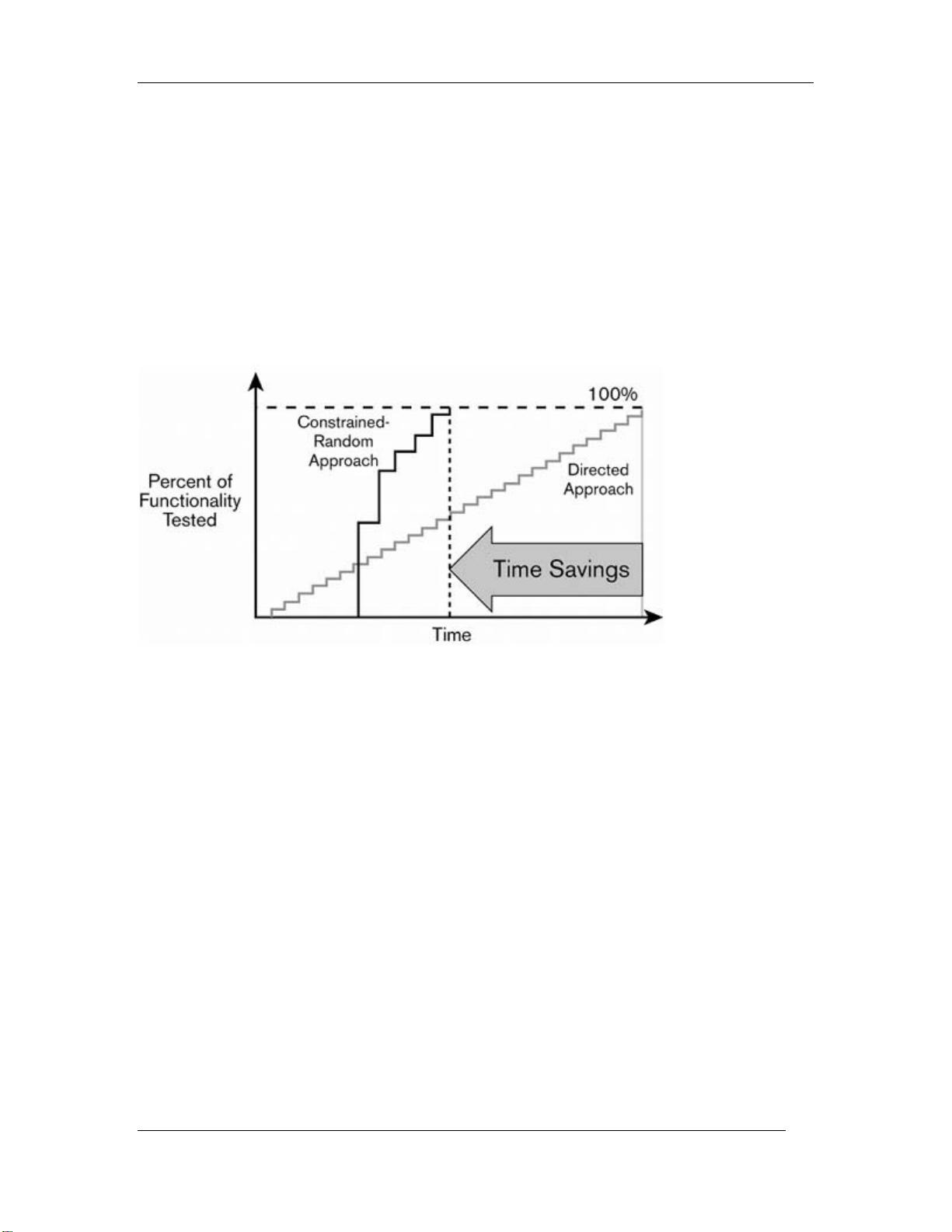

Figure 1 自动测试相对于直接测试有更高效率 ............................................................. 5

Figure 2 自动及人工验证技术运用在验证不同阶段 ..................................................... 6

Figure 3 断言是验证重要组成部分 ................................................................................ 7

- 2 -

SYNOPSYS 基于 SystemVerilog 语言的验证方法学

Figure 4 多层测试平台方便验证重用 ............................................................................. 9

Figure 5 高层次测试平台单元更早验证事务级模型 ................................................... 10

Figure 6 具有通用接口协议验证IP重用到新项目........................................................ 12

Figure 7 XVC结构分为两层:发生器和驱动器........................................................... 13

Figure 8 XVC 管理器控制并使测试平台中其他XVC协调工作 ................................. 14

Figure 9 系统确认环境必须高效度量系统执行 ........................................................... 16

Figure 10 vmm_env类定义一系列virtual methods用于执行测试用例 ........................ 18

Figure 11 VMM检查库扩展了OVL断言内容................................................................ 20

Figure 12 用XVC标准库和VMM标准库中类建立XVC ............................................... 20

- 3 -

SYNOPSYS 基于 SystemVerilog 语言的验证方法学

1 SystemVerilog 验证方法学介绍

芯片验证中虽然传统验证方法尽力保持技术更新步伐以适应设计尺寸以及复杂度的增

加,但验证依然是当前 SoC 以及可重用 IP 模块设计中面临的最大挑战。解决这个问题的

方法是采用有丰富语义支持的标准语言,以及可重用,覆盖率为驱动的验证方法学。

这是文章中的第一部分:介绍由 SystemVerilog 硬件设计验证标准语言支持的验证方

法学。此方法学在

《

VMM for SystemVerilog

》

一书中有全面介绍。

《

VMM for SystemVerilog

》

致力于如何建立一个可升级,可预期,可重用的验证环

境,使得用户能充分利用断言性,重用性,验证平台自动生成,覆盖率,形式分析以及其

他先进验证技术特点,从而帮助解决 RTL 以及系统级中验证技术问题。如此一个环境能

在芯片迈出成功第一步时增加用户验证信心。

《

VMM for SystemVerilog

》

目的是针对所有

SoC,IP 项目建立一个高效,可控验证过程。

《

VMM for SystemVerilog

》

来源于业界领先

的 ARM 公司,Synopsys 公司(新思科技)及其客户经验。

1.1 验证面临挑战

随着 SoC,IP 验证复杂度持续增加,有相应的新验证技术产生,但设计能力与验证所

能提供信心之间鸿沟仍然巨大。多次调查显示有一半到三分之二的 SoC 项目在第一次流片

失败,而功能缺陷的存在是其中主要原因。

这些统计显示了要验证当今设计所具有的固有难度。复杂模块,尤其在集成到一起

后,很难在验证中将芯片实际运用可能遇到的所有条件模拟执行。预期到所有可能边界条

件(corner cases),以及发现设计中深层次设计缺陷是验证面临的关键挑战之一。非常紧

迫的是在规定项目资源以及 time-to-market 需求情况下,项目过程中花费最小代价尽可能

早发现设计缺陷。

1.2 SystemVerilog 验证技术

对用户来说有多种方法编写验证平台,搭建验证环境。通常方法包括全手工编写代码

进行独立直接验证,或生成带约束随机仿真激励,能自动产生新测试用例先进的验证平

台。最有效技术包括利用功能覆盖率统计更进一步加强自动验证效率。一些验证技术还包

括应用断言检查设计意图,诊断设计缺陷。

《

VMM for SystemVerilog

》

覆盖了多种验证技术,并详细介绍如何将他们有机结合在

一起。多种先进验证技术的有效融合能彻底改进验证,增加验证产量,加速开发进程,尽

早结束项目。相对于传统方法消耗更少资源。

《

VMM for SystemVerilog

》

既能提升现有验

证方法,也能充分利用验证过程自动化,功能覆盖,断言这些特点建立一个全面通用验证

环境。

1.3 产生带约束随机仿真

传统验证依赖于直接测试(directed tests),此时测试平台包含产生特定情节的代码,

对设计提供激励,仿真结束时检查(手工或自测方式)结果。直接测试平台也可以采用有

限的随机方式。通常是产生随机数,而不是在每个数据单元简单写入预先设定值。直接测

试方法适合于小设计,但一个典型 SoC 设计需要上千个测试用例。乐观估计用三天时间产

- 4 -

SYNOPSYS 基于 SystemVerilog 语言的验证方法学

生并调试一个测试,一个有十验证工程师的团队(也是一个乐观估计)将花费超过一年完

成所有测试。因此提升验证产量的唯一方法是减少产生测试所消耗时间。

SysemVerilog 具有丰富语言能力,能描述复杂验证环境,包括带约束随机激励产生,

面向对象编程,功能覆盖统计。这些特点使用户开发出能自动产生大量验证情节的测试平

台。

《

VMM for SystemVerilog

》

展示了如何用 SysemVerilog 语言功能构建一个自动化验证

平台。建立一个验证环境时,采用正确策略,充分利用自动化特点,产生一个新测试所消

耗时间将显著减少。应用带约束随机激励产生方法,在可控制规则,或用户自定义约束下

以自动方式产生测试情节。验证中很重要一点在于测试平台质量,这样附加的测试可在对

一系列基本测试用例基础上进行简单调整测试参数或加入定义好的约束而产生。通过这种

方法获得好处在图 1 中说明。

Figure 1 自动测试相对于直接测试有更高效率

用直接测试方法,产生一个新测试所需要时间相对固定,因此功能验证质量提高与时

间基本成线型关系。而一个带约束随机验证环境,在第一次能正常测试之前有一个前期投

入消耗。此投入用于建立验证环境中参数化配置能力,以及约束测试中相关部分,使得之

后测试更容易基于约束驱动。

测试情节类型中建立随机化,不仅仅是产生新数据值,更增加了测试击中边界条件

(corner case)可能性,从而发现更多设计缺陷。下一部分还将讨论,这样的测试用例也

能击中更多覆盖点,加速验证收敛。

SystemVerilog 提供了带约束随机激励测试所需要的所有验证语言结构。

《

VMM for

SystemVerilog

》

提供了如何建立一个带约束随机环境,如何运用面向对象编程技术编写可

重用验证单元,如何在整个项目验证,或跨项目之间重用验证单元的整套方法。

1.4 覆盖率驱动验证

贯穿验证过程中的覆盖率测量数据有两方面重要作用。一方面能明确指出设计中还没

有被充分验证到的部分,确定验证过程中空洞。通过回答下一步如何去做这样的关键问

题,有助于指引验证需要努力的方向。比如,需要补充编写哪些直接测试用例,如何改变

参数用于带约束的随机测试。

另一方面,覆盖率测量是验证已经足够充分,可进行流片的指示器。覆盖率不仅仅简

单提供是或否这样结果。覆盖率增量提升,用于评估验证进度,增加开发团队进行流片时

- 5 -

剩余21页未读,继续阅读

ran_muen

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 数据结构1800题含完整答案详解.doc

- 医疗企业薪酬系统设计与管理方案.pptx

- 界面与表面技术界面理论与表面技术要点PPT学习教案.pptx

- Java集合排序及java集合类详解(Collection、List、Map、Set)讲解.pdf

- 网页浏览器的开发 (2).pdf

- 路由器原理与设计讲稿6-交换网络.pptx

- 火电厂锅炉过热汽温控制系统设计.doc

- 企业识别CIS系统手册[收集].pdf

- 物业管理基础知识.pptx

- 第4章财务预测.pptx

- 《集成电路工艺设计及器件特性分析》——实验教学计算机仿真系.pptx

- 局域网内共享文件提示没有访问权限的问题借鉴.pdf

- 第5章网络营销策略.pptx

- 固井质量测井原理PPT教案.pptx

- 毕业实习总结6篇.doc

- UGNX建模基础篇草图模块PPT学习教案.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2