没有合适的资源?快使用搜索试试~ 我知道了~

首页Xilinx_ise使用教程(配合Modelsim使用)

Xilinx_ise使用教程(配合Modelsim使用)

这是我收集的一个Xilinx_ISE6.1的教程,结合了MODELSIM的仿真功能,自己感觉讲解的还可以,适合初学者入门使用,对其他人员也有一定的参考价值。

资源详情

资源评论

资源推荐

2004-2-16 征求意见版本(3-21) To Luo 第 207 页

第 7 章 Xilinx ISE6.1i 简明教程

在本章里介绍 Xilinx 公司 FPGA/CPLD 的集成开发环境——ISE(Xilinx Integrated

Software Environment)6.1i 软件的简单使用,该软件环境集成了 FPGA 的整个开发过程

所用到的工具,不过仿真工具除外。本章主要介绍了用 VHDL、VerilogHDL、原理图以及 EDIF

网表进行设计输入、用 ModelSim 仿真工具对设计进行功能仿真和时序仿真以及将数据流文

件加载到 FPGA 等方面的内容。本章给初学者演示了一个完整的实现 FPGA 设计的开发流程,

没有涉及较深入的细节问题,阅读并练习本章介绍的各节,读者就有足够的信心去把精力放

到设计本身,而不是放到掌握 ISE 软件上来。如果你有 HDL 语言方面的基础,读完本章,

也许你会发现,原来开发 FPGA 并不神秘,而且是如此容易上手。关于较为深入的方面,可

以参阅 ISE 高级设计工具一章。

7.1 设计准备

7.1.1 ISE6.1i 软件的安装

ISE6.1i 软件本身共有两张光盘,包括了 ISE 的各种工具。如果读者需要对设计进行仿真,

可以安装 ModelSim,一般在购买 ISE 时会有一张 ModelSim 的光盘,该光盘为 ModelSim 的

Xilinx 版本 ModelSimXE(XilinxEdition)。当然也可以直接购买 ModelSim 的其他版本,再将

Xilinx 的仿真库文件编译即可使用,与 ISE6.1i 对应的 ModelSim 版本为 5.7 版本,ISE 软件

和 ModelSim 软件的更新非常快,在写这本书的时候,ISE6.2 和 ModelSim5.8 已经发布了,

ModelSim 的任何版本可以从该公司网站 http://www.model.com/

上免费下载,所谓的购买就是

购买 License 文件,好了,关于 ModelSim 的介绍就先说到这里,在 ModelSim 使用一章中将

详细再讲。

在安装时,先放入第一张光盘,运行 setup.exe 文件,输入申请的注册号码,根据提示一

步一步地确认即可正常安装,第一张光盘安装完成之后,放入第二张光盘,运行 setup.exe 文

件,再根据提示信息一步一步完成安装。相信对于有 Windows 操作基础的读者应该不成问题。

要注意的是 ISE 是根据注册号码来确认是评估版本还是正式版本,两个版本之间除了评估版

本有时间限制外,两者其他区别不大。要确定自己按照的版本是不是正式版本,只需要看看

编译结果中是否有警告信息说明该版本是评估版本就可以了。如果读者需要,可以安装

ModelSim,建议初学者安装 ModelSimXE,因为不需要编译 Xilinx 的仿真库文件。另外,在

安装时选择类型为初学者类型,可以到 Xilinx 网站上申请免费的 License 文件,使用该 License

文件足够完成一般的设计仿真,并且避免了费很大功夫去试那些破解文件的烦恼。何乐不为

呢?关于 ModelSim 的安装以及 License 的申请等等关于 ModelSim 的问题,在 ModelSim 使

2004-2-16 征求意见版本(3-21) To Luo 第 208 页

用一章中详细讨论。

另外,如果读者需要,可以购买安装其他第三方工具(前面所说的 ModelSim 就是第三

方工具),例如文本输入工具 UltraEdit、Code Wright 等,以及 Synplify、Synplify Pro、

LeonardoSpectrum 等综合工具,另外,如果还可以安装 ChipScope(片内逻辑分析仪)工具。

之所以提到这些工具是因为 ISE6.1i 中可以集成使用这些工具。这也是不同于以前版本的地

方。同时,也希望读者明白,这些工具是可选的,没有这些工具也可以完成设计,在深入教

程中会对部分上述提到的部分工具介绍一下。

7.1.2 ISE 软件的运行及 ModelSim 的配置

安装完成之后,单击“开始->程序->Xilinx ISE6->Project Navigator”,进入 ISE 软件。为

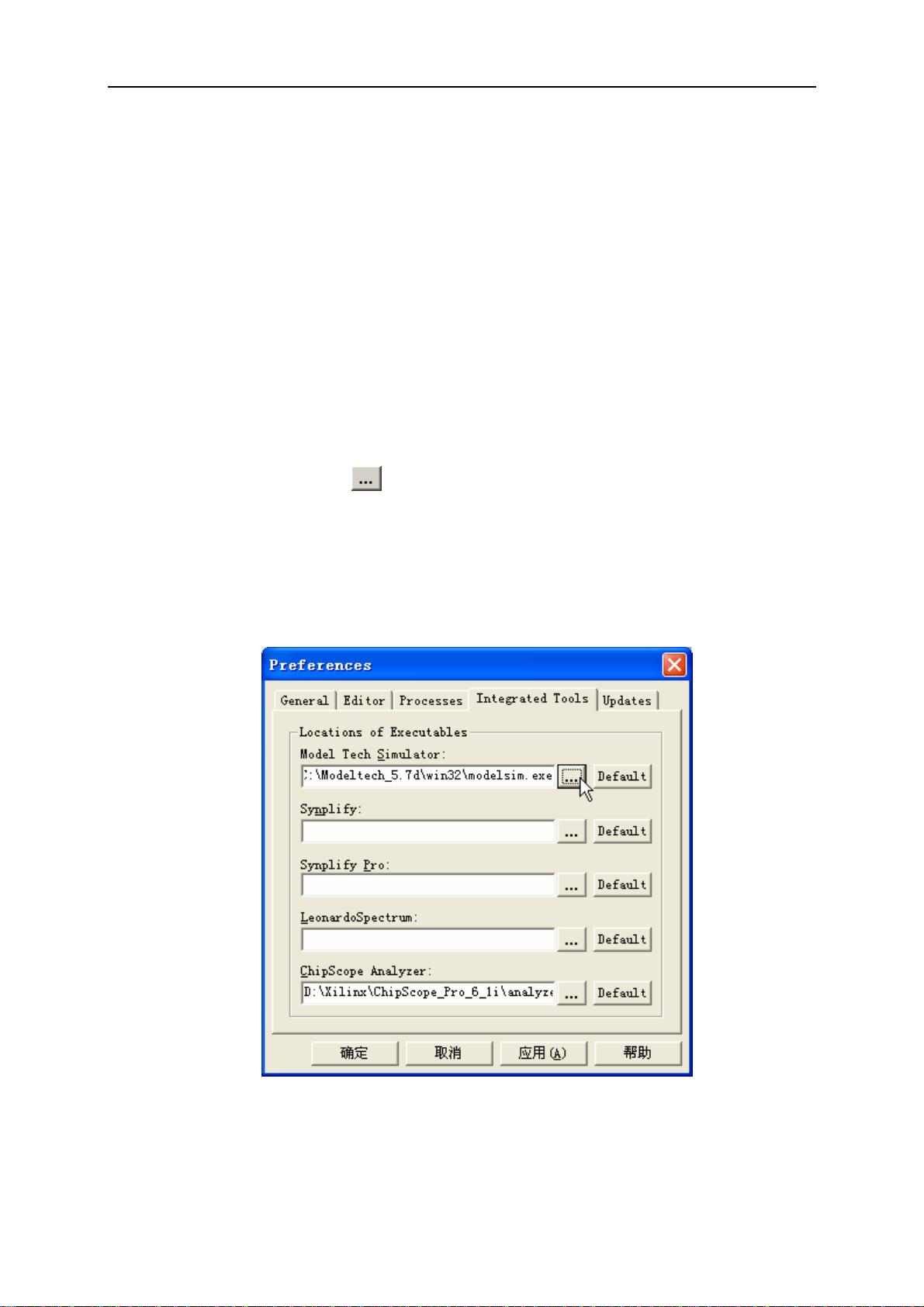

了能够使用 ModelSim 进行仿真,选择菜单 Edit->Preferences…,选择选项卡 Partner Tools,出

现界面如图 7-1 所示。单击按钮

找出 ModelSim.exe 文件,单击“确定”。需要注意的是这

方面的设置与以前 ISE 版本不同,在 ISE4.2 中设置是这样的。但在 ISE5.1 以及 ISE5.2 中是

指定 ModelSim.exe 文件所在的目录,而 ISE6.1 的设置与 ISE4.2 的设置相同。单击“确定”

关闭该窗口,关闭 ISE(这一步非常重要,否则可能不能在 ISE 中调用 ModelSim 进行仿真),

再重新进入 ISE 既可用调用 ModelSim 对设计进行仿真了。

图 7-1 第三方工具设置窗口

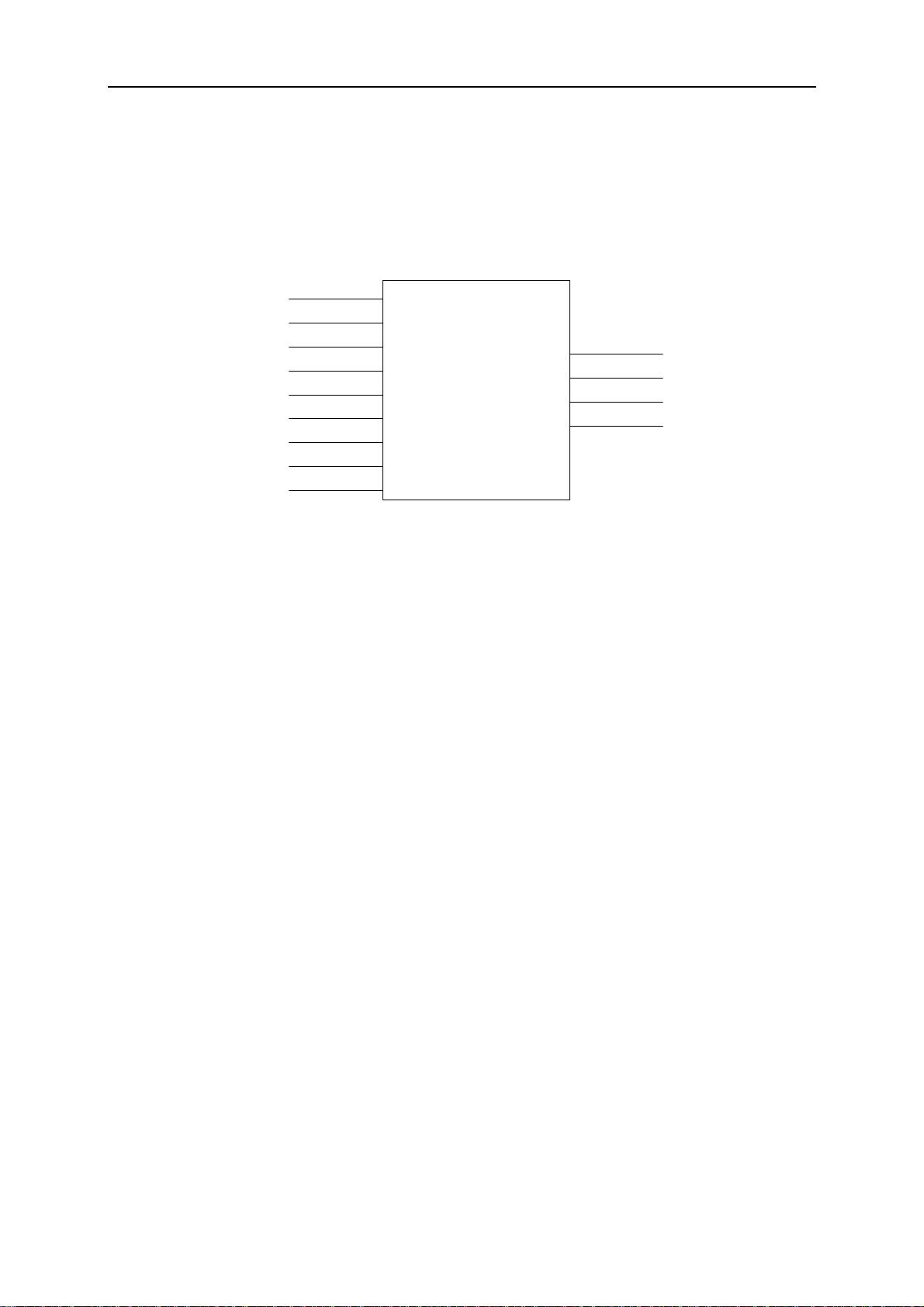

在下一节我们以一个具有复位(reset)、使能(ce)、置数(load)、计数方向控制(dir)

功能的计数器为基础进行设计。其方块图如图 7-2 所示。其中 CLK 为输入计数时钟信号,系

2004-2-16 征求意见版本(3-21) To Luo 第 209 页

统在该信号的驱动下开始工作;RESET 为复位信号,在上升沿处,输入复位为全零;CE 为

使能信号,为 1 时计数正常进行,为 0 时停止计数;LOAD 为置数信号,当在时钟上升沿该

信号为 1 时,将 DIN0~DIN3 分别置给 COUT0~COUT3。DIR 为计数方向控制,为 1 时递

增计数,为 0 时递减计数。这些功能描述只是我们的设计目标,或称为设计需求,我们在设

计一个系统时,第一步就是要明确我们的设计要求。下面,我们就开始设计过程。

图 7-2 计数器方块图

7.2 用 VHDL 语言设计输入

在本节,我们用 ISE6.1 中的 VHDL 语言模板来实现图 7-2 所示的 4 位计数器模块。所谓

的语言模板是对特定功能模块给出了一个基本的描述或者给出了一些部件的使用信息,编程

者可以根据这些基本的描述来做稍微的修改来实现设计所需功能。下面就一步步开始我们的

设计。对于已经初步掌握 ISE 的读者,可以略过这一部分。对于初学者,建议按照所列的步

骤一步一步实现一遍,体会一下。

7.2.1 创建一个新工程

步骤如下:

Step1. 单击“开始->程序->Xilinx ISE6->Project Navigator”,进入 ISE 软件。

Step2. 选择 File->New Project…,出现如图 7-3 所示的窗口。这个窗口与以前版本的差

别较大,以前的版本出现的窗口中可以直接选取器件类型、封装、门数、速度等级等

信息。而在 ISE6.1 中需要单击“下一步”才能看到这些设置信息。在本例中,我们

先选择工程存放的路径,然后输入工程名称。系统自动为每一个工程设定一个目录,

目录名为工程名。再选择顶层模块类型为 HDL。其他几种类型说明如下:Schematic

为原理图输入类型,类似于我们制作 PCB 原理图时的情况,可以从库中选取器件,

也可以用 HDL 语言来生成器件,在后续章节会介绍原理图为设计输入的情况;EDIF

计数器

CLK

RESET

CE

LOAD

DIR

DIN3

DIN2

DIN1

DIN0

COUT3

COUT2

COUT1

COUT0

2004-2-16 征求意见版本(3-21) To Luo 第 210 页

为网表输入类型,EDIF 是 Electronic Data Interchange Format 的缩写,是一种描述设

计网表的标准的工业文件格式,可以由第三方工具生成,在 ISE 中可以将其作为一种

标准的输入格式。NGC 文件是一种包含了逻辑设计数据和约束的网表,所谓约束是

指 FPGA 设计中的一些特定的要求,例如,我们分配设计中的信号到具体的管脚时,

需要一个文件来指定如何分配,这就是一种约束文件,由于 NGC 网表包含了设计和

约束,因此一个文件足够描述一个设计了。NGC/NGO 和 EDIF 都可以在 ISE 外由其

他综合工具生成也可由 ISE 生成。如果我们需要用 ISE 作为设计输入,需要选择

Schematic 或 HDL 作为顶层模块类型;如果已经完成的设计文件为 ABEL、Verilog

或 VHDL,应选择 HDL 为顶层模块类型;如果已经完成的设计文件为原理图,这里

应该选择 Schematic 作为顶层模块类型。这里我们先学习一下最常用的用 HDL 语言

来描述设计。

图 7-3 新工程项对话框

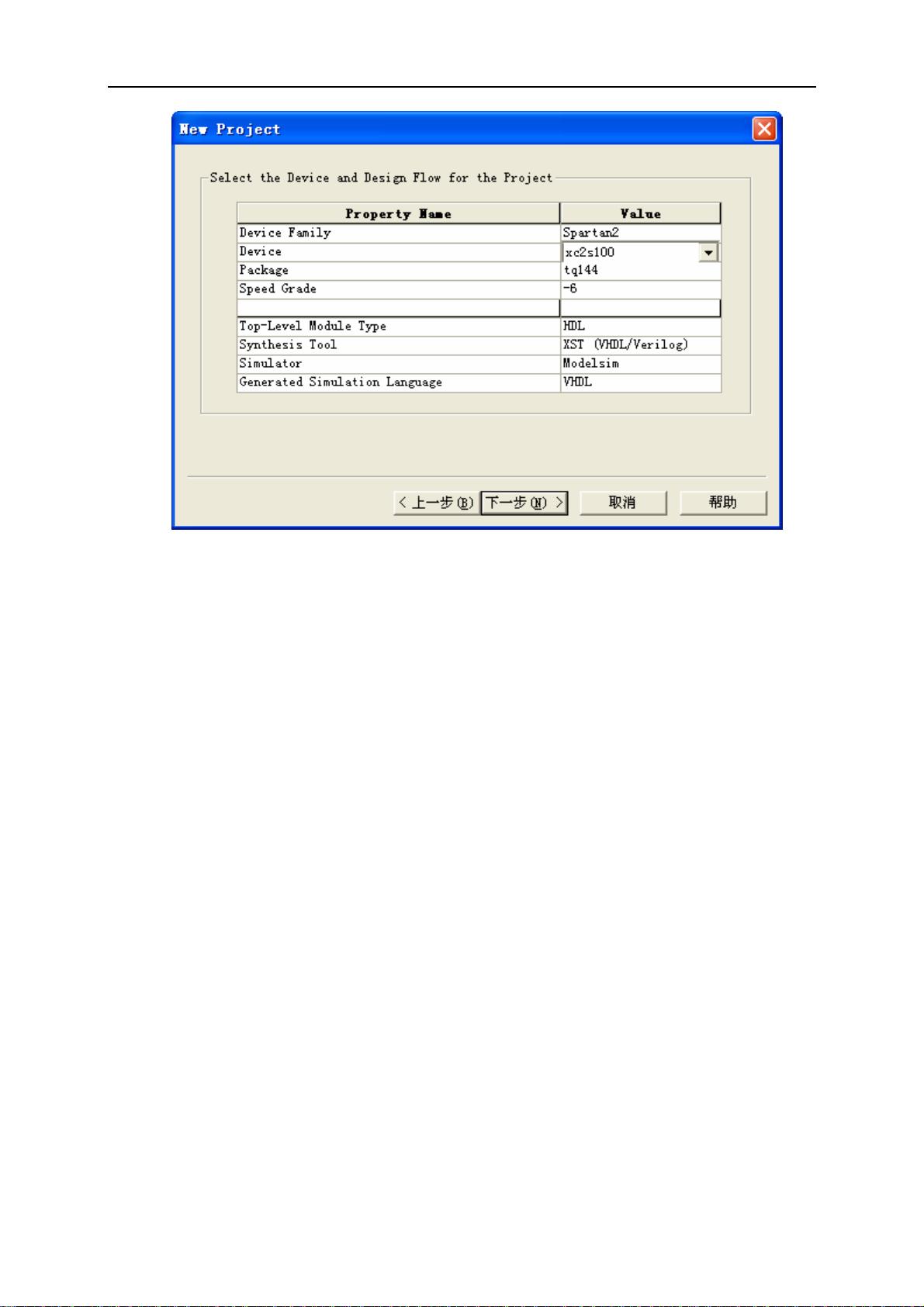

Step3. 单击“下一步”,出现如图 7-4 所示的窗口,在该窗口中来选择设计实现时所用

的器件。在包含 FPGA 的 PCB 板子做出来以前,我们选择不同类型的 FPGA 进行测

试,看看 FPGA 的资源是否够用,在 PCB 板子做出来以后,我们在这里的选择与 PCB

板上的 FPGA 必须一致。否则生成的下载文件无法配置到 FPGA 中。此处若选择错了,

也没有关系,因为后面可以随时修改这些设置。其中 DeviceFamily 表示目标器件的

类型;Device 表示目标器件的具体型号;Package 表示器件的封装;SpeedGrade 表示

器件的速度等级。这里我们选择器件为 Spartan2E,xc2s100,tq144,-6。其 中 xc2s100

中的 100 表示器件为 10 万门,tq144 表示器件有 144 个管脚。

2004-2-16 征求意见版本(3-21) To Luo 第 211 页

图 7-4 设置工程所用的器件参数

Step4. 因为这里我们重新编写 VHDL 源代码,而不是使用以前设计好的源代码,故再

单击“下一步”,“下一步”,单击“完成”,工程创建完毕。

Step5. 这时的界面如图 7-5 所示,这里需要关注的是界面左上角出现的小框为我们所有

的源文件的管理窗口,在其下面的窗口为我们选择不同的源文件时其所有可能操作的

显示窗口;右半部分窗口为我们设计输入代码的窗口;下面的窗口为编译等信息的显

示窗口。这里与以前版本不同的地方在于编译输入窗口这里将 Warnings 和 Errors 可

以分开显示。我们可以在输入不同文件后选中不同的文件,看看进程窗口中的变化。

这样,我们新建了一个工程,下一步就要在工程中输入一些设计文件来实现我们的设

计。

剩余48页未读,继续阅读

LukeGu10

- 粉丝: 0

- 资源: 17

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论9