没有合适的资源?快使用搜索试试~ 我知道了~

首页逻辑电平转换方法及电路设计

资源详情

资源评论

资源推荐

Application Report

SCAA062 – March 2003

1

DC-Coupling Between Differential LVPECL, LVDS, HSTL, and CM

Kal Mustafa / Chris Sterzik High Performance Analog

ABSTRACT

This report describes various methods of interfacing different logic levels. The focus is dc-

coupling between the following differential signaling: LVPECL (low-voltage positive-

referenced emitter coupled logic), LVDS (low-voltage differential signals), HSTL (high-

speed transceiver logic), and CML (current-mode logic). The report discusses sixteen

various interface cases between the aforementioned differential signaling levels.

Contents

1 AC-Coupling..................................................................................................................................2

1.1 LVPECL..................................................................................................................................3

1.2 LVDS ....................................................................................................................................7

1.3 CML ..................................................................................................................................11

1.4 HSTL ..................................................................................................................................13

2 References ..................................................................................................................................15

Figures

Figure 1. Input and Output Parameters..........................................................................................2

Figure 2. LVPECL to LVPECL..........................................................................................................3

Figure 3. LVPECL to LVPECL..........................................................................................................4

Figure 4. LVPECL to LVDS..............................................................................................................4

Figure 5. LVPECL to LVDS..............................................................................................................5

Figure 6. LVPECL to CML................................................................................................................5

Figure 7. LVPECL to CML Converter ..............................................................................................6

Figure 8. LVPECL to HSTL ..............................................................................................................6

Figure 9. LVDS to LVPECL..............................................................................................................7

Figure 10. LVDS to LVPECL..............................................................................................................8

Figure 11. LVDS to LVDS Without On-Chip Termination ................................................................8

Figure 12. LVDS to LVDS With On-Chip Termination......................................................................9

Figure 13. LVDS to CML Converter...................................................................................................9

Figure 14. LVDS to HSTL.................................................................................................................10

Figure 15. CML to LVPECL Translator............................................................................................11

Figure 16. CML to LVDS ..................................................................................................................11

Figure 17. CML to CML....................................................................................................................12

Figure 18. CML to HSTL...................................................................................................................13

Figure 19. HSTL to LVPECL Converter...........................................................................................13

Figure 20. HSTL to LVDS.................................................................................................................14

Figure 21. HSTL to CML Translator ................................................................................................14

Figure 22. HSTL to HSTL.................................................................................................................15

Tables

Table 1. Typical LVPECL, LVDS, HSTL, and CML Outputs..........................................................2

Table 2. Typical LVPECL, LVDS, CML, and HSTL Input Levels...................................................2

Table 3. Interface Table..................................................................................................................3

SCAA062

2 DC-Coupling Between Differential LVPECL, LVDS, HSTL, and CM

1 AC-Coupling

DC-coupling is used in a system when there is a need for a wide bandwidth, or when dc-

unbalanced code is used. Both interfaces must have the same ground potential on the same

board or system. DC-coupling directly connects the components together without any coupling

capacitors. Among the advantages of dc-coupling are: simple board design, no dc-wander

issues, and it is useful in all coded-data streams including SONET and NRZ data applications.

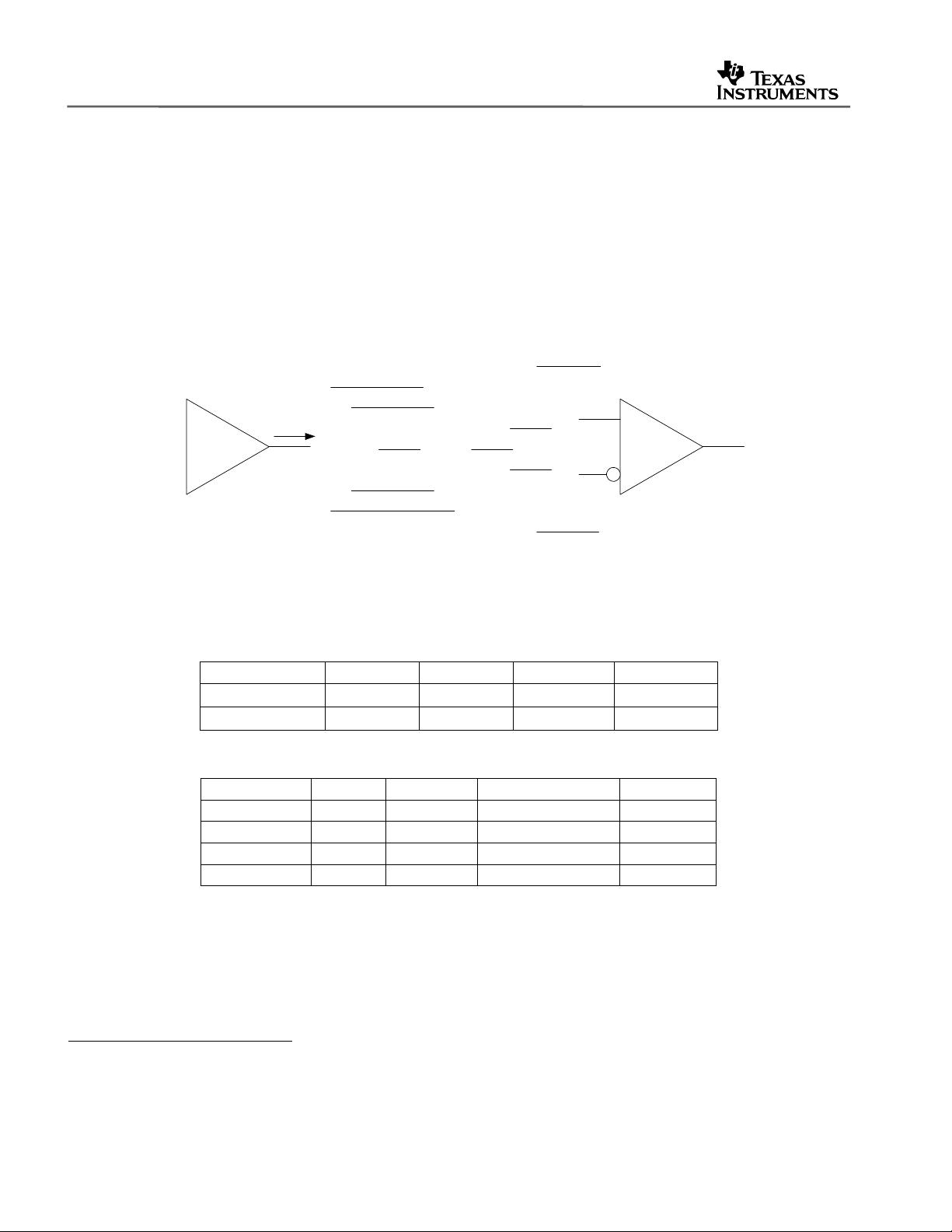

One disadvantage of dc-coupling is that it requires careful power supply design. Figure1,

Table 1, and Table 2 provide the I/O levels for these differential signals.

Receiver

V

IH

(MAX)

V

IH

(MIN)

V

IL

(MAX)

V

IL

(MIN)

Driver

V

OH

(MAX)

V

OH

(MIN)

I

OH

(MAX)

V

OL

(MAX)

V

OL

(MIN)

I/O Parameters

VCM

Figure 1. Input and Output Parameters

Table 1. Typical LVPECL, LVDS, HSTL, and CML Outputs

Output LVPECL LVDS HSTL CML

V

OH

(Min)

2.275 V 1.249 VDDQ

1

-0.4 V

CC

2

V

OL

(Max)

1.68 V 1.252 0.4 V

CC

-0.4V

Table 2. Typical LVPECL, LVDS, CML, and HSTL Input Levels

Input LVPECL LVDS HSTL CML

V

IH

(Min) 2.135 V 1.249 VRef + 0.2 V

CC

VRef or VCM 2 1.2 0.75 V

CC

-0.2V

V

IL

(Max) 1.825 V 1.252 VRef -0.2 V

CC

-0.4V

V

ID

(Min) 310 mV 200 mV 400 mV 400 mV

1

VDDQ = 1.5 V ±10%

2

V

CC

= 3.3 V ±10%

SCAA062

DC-Coupling Between Differential LVPECL, LVDS, HSTL, and CM 3

Table 3. Interface Table

TO

LVPECL LVDS CML HSTL

LVPECL

See Figure 3

See Figure 4 or Figure 5 See Figure 6 or Figure 7 See Figure 8

LVDS

See Figure 9

or Figure 10 See Figure 11 or Figure 12 See Figure 13 See Figure 14

CML

See Figure 15

See Figure 16 or See Figure 17 See Figure 18

FROM

HSTL

See Figure 19

See Figure 20 See Figure 21 See Figure 22

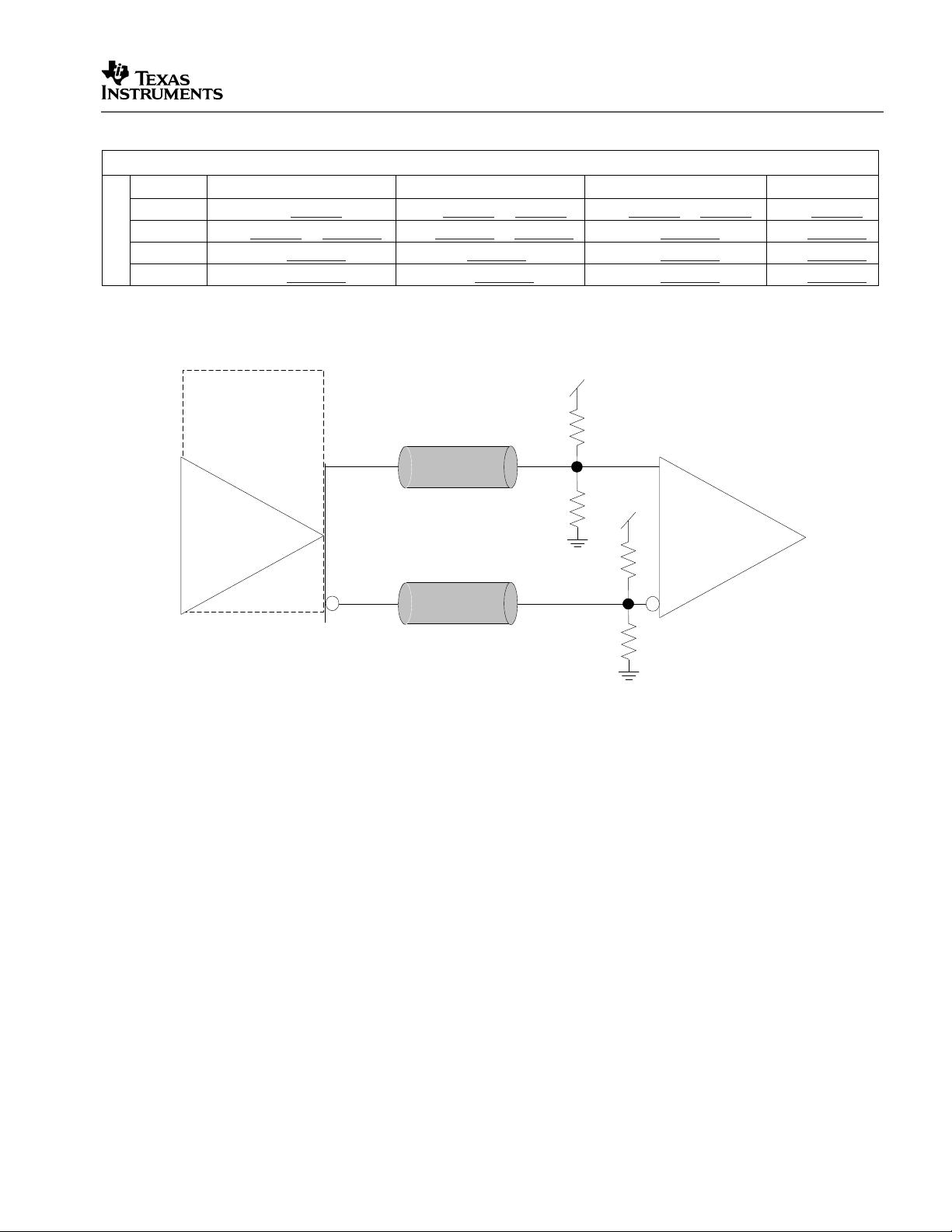

1.1 LVPECL

e.g.,

CDC111

CDCVF111

CDCLVP110

Z

O

=50Ω

ΩΩ

Ω

Z

O

=50Ω

ΩΩ

Ω

V

C

C

V

C

C

130

Ω

Ω

Ω

Ω

130

Ω

Ω

Ω

Ω

83

Ω

Ω

Ω

Ω

83

Ω

Ω

Ω

Ω

LVPECL

Driver

LVPECL

Receiver

Figure 2. LVPECL to LVPECL

PECL and LVPECL are normally terminated though 50 Ω to (V

CC

- 2 V). Most systems normally

do not have dual power supplies of both 3.3 V and 1.3 V; therefore Figures 2 and Figure 3 show

alternative methods to terminate LVPECL output signals. The pullup and pulldown combination

terminates the 50-Ω transmission line and establish the LVPECL common-mode voltage of 2 V

at the receiver.

SCAA062

4 DC-Coupling Between Differential LVPECL, LVDS, HSTL, and CM

e.g.,

CDC111

CDCVF111

CDCLVP110

Z

O

=50Ω

ΩΩ

Ω

Z

O

=50Ω

ΩΩ

Ω

R2

R1

R3

LVPECL

Driver

LVPECL

Receiver

(V

CC

-2V)

Note:

For V

CC

=3.3V,useR1=R2=R3=50Ω

ΩΩ

Ω

For V

CC

=2.5V,useR1=R2=50 Ω,

50 Ω, 50 Ω,

50 Ω, R3 = 22 Ω

= 22 Ω= 22 Ω

= 22 Ω

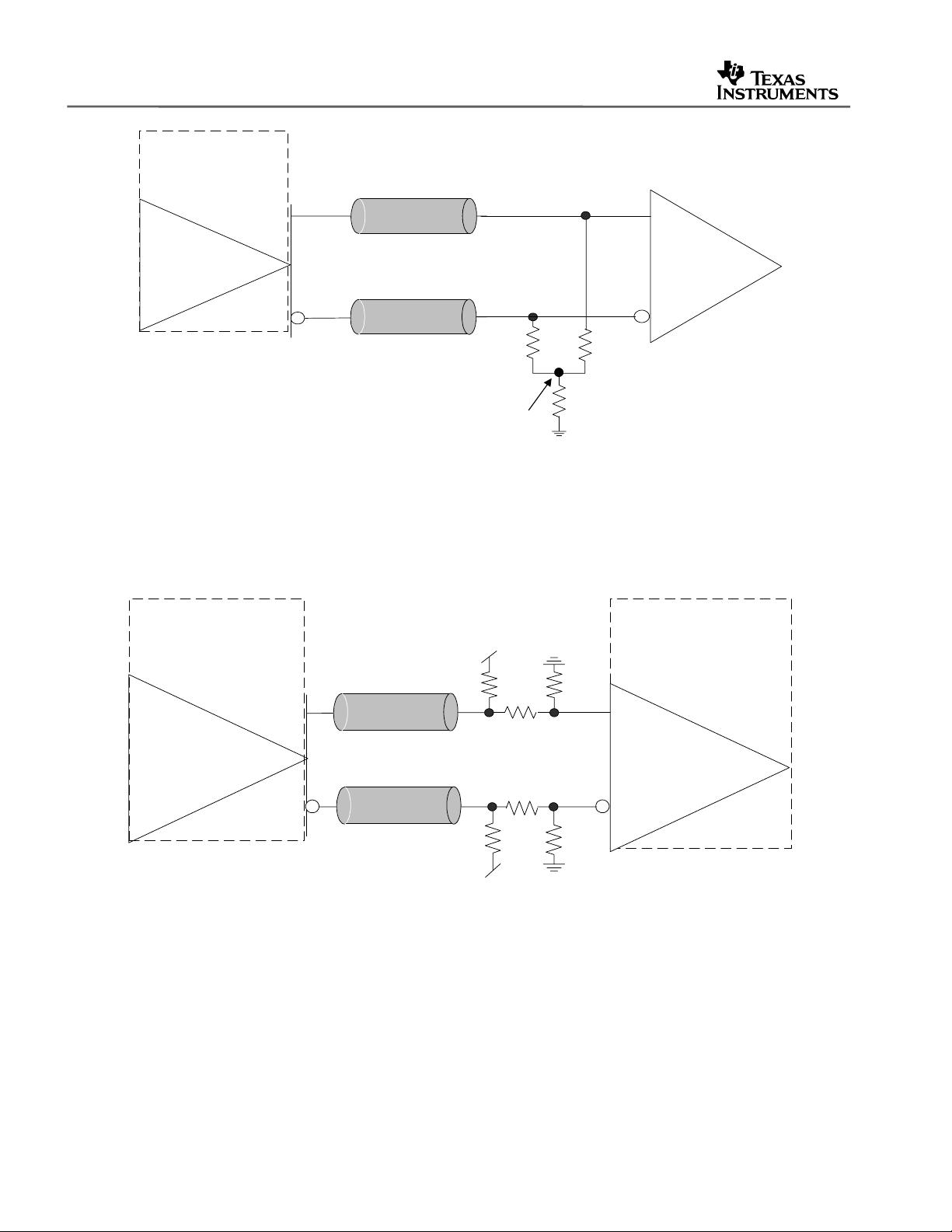

Figure 3. LVPECL to LVPECL

The Y-termination in Figure 3 is another alternative to LVPECL termination where a VTT supply

is not readily available. This scheme saves one resistor over the scheme in Figure 2.

e.g.,

CDC111

CDCVF111

SN65LVDS101

CDCLVP110

e.g.,

SN65LVDS104

SN65LVDS108

SN65LVDS116

Z

O

=50Ω

ΩΩ

Ω

Z

O

=50Ω

ΩΩ

Ω

130

Ω

Ω

Ω

Ω

33 Ω

ΩΩ

Ω

3

.

3

V

LVDS

Receiver

3

.

3

V

130

Ω

Ω

Ω

Ω

50

Ω

Ω

Ω

Ω

33 Ω

ΩΩ

Ω

50

Ω

Ω

Ω

Ω

LVPECL

Driver

Figure 4. LVPECL to LVDS

The 33-Ω resistor is usually required when the LVPECL output is too high for the LVDS receiver

input stage. For the LVDS receivers listed above, it is not required and Figure 5 is

recommended.

剩余15页未读,继续阅读

sfm1231

- 粉丝: 0

- 资源: 14

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0