没有合适的资源?快使用搜索试试~ 我知道了~

首页usb2.0 IP CORE

usb2.0 IP CORE

需积分: 10 13 下载量 93 浏览量

更新于2023-03-03

评论 1

收藏 135KB PDF 举报

USB 2.0 开发的参考资料 内涵usb的开发内核 易于理解Usb的协议

资源详情

资源评论

资源推荐

Features

• USB Specification Rev. 2.0 com-

pliant

• Supports up to 127 devices and 8

downstream ports

• Compliant with EHCI Rev. 1.0

specification

• OHCI companion processor for

UBS 1.1 transfers

• Supports 16-bit UTMI and 8-bit

ULPI interfaces

• Direct addressing of all IP Core

registers from PCI, Custom, or

AHB bus

• DMA controller supports high-

speed data transfers between

USB Host and PCI/Custom/AHB

host

• Supports 8, 16, 32-bit PCI/Cus-

tom/AHB bus

• Optional 33 MHz PCI Rev. 2.2

master/target interface

• Optional 133 MHz AHB Rev. 2.0

master/slave interface

• Optional Custom bus interface

USB 2.0 Host IP Core

Overview

The Arasan USB 2.0 Host IP Core is an USB 2.0 specification compliant

host core with optional PCI, Custom, or AHB master/slave interfaces.

The USB 2.0 host core supports 480 Mbit/s in High Speed (HS) mode.

12 Mbit/s in Full Speed (FS) mode, and 1.5 Mbit/s in Low Speed (LS)

mode.

The Arasan USB 2.0 Host IP Core consists of an Enhanced Host Control-

ler Interface (EHCI) and a companion Open Host Controller Interface

(OHCI). The EHCI processor handles HS transactions and is the default

owner of the Root Hub that connects to downstream ports. In a

downstream data transfer, the EHCI sends data to the Host Parallel

Interface Engine (HPIE) for encoding and CRC appending. Data

received by the USB 2.0 Root Hub is forwarded to downstream ports

through the Root Hub. Similarly, FS and LS transactions are handled by

the OHCI, Host Serial Interface Engine (HSIE), and USB 1.1 Root Hub.

The Root Hub performs multiplexing and forwarding of packets

between the downstream ports and USB 2.0/1.1 Root Hubs. Up to 8

downstream ports can be connected to the USB 2.0 Host IP Core.

With the addition of optional ULPI Wrappers, the Arasan USB 2.0 Host

IP Core can be connected directly to standard UTMI or 8-bit ULPI trans-

ceivers.

The Arasan USB 2.0 Host IP Core is an RTL design in Verilog and VHDL

that implements an USB host controller on an ASIC or FPGA. The core

includes RTL code, test scripts and a test environment for full simula-

tion verifications. Licensees include Los Alamos National Labs, Stac-

cato Communications, Focus Semiconductors, etc.

Copyright 2006 Arasan Chip Systems Inc.

Version 1.0

USB 2.0 Certified

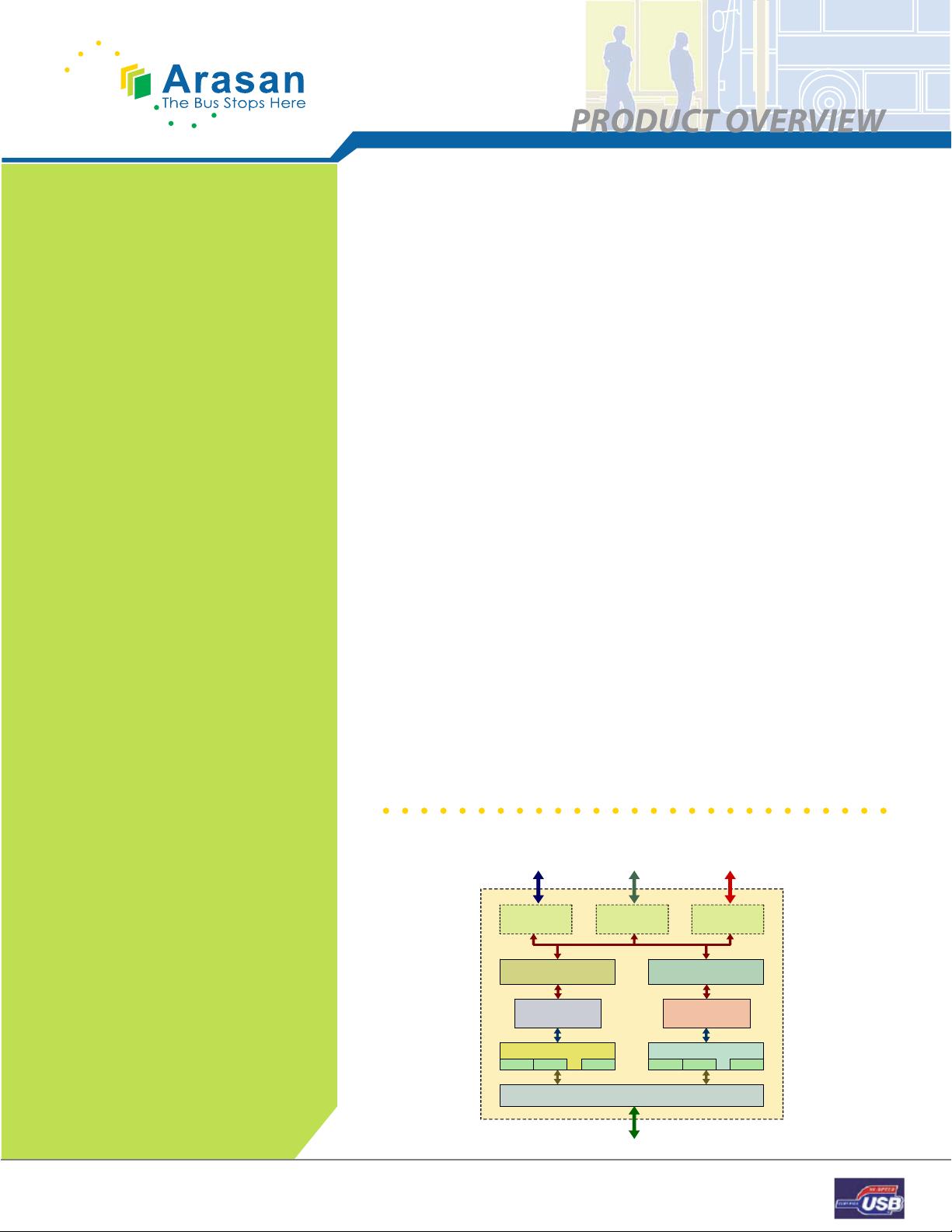

USB 2.0 Host IP Core Functional Block Diagram

AMBA

Master/Slave

AHB Bus

PCI Bus

PCI

Master/Target

Custom

Master/Target

Custom Bus

EHCI List Processor OHCI List Processor

Host Serial

Interface Engine

Host Parallel

Interface Engine

USB 2.0 Root Hub USB 1.1 Root Hub

Root Hub

XCVR1, XCVR2, … XCVRN

Prot 1 Prot 2 Prot N Prot 1 Prot 2 Prot N

……

The Arasan USB 2.0 Host IP Core is an

RTL design in Verilog and VHDL that

implements an USB host controller on

an ASIC or FPGA. The core includes RTL

code, test scripts and a test environ-

ment for full simulation verifications.

tom781019

- 粉丝: 0

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0