用 CPU 配置 Altera 公司的 FPGA

一. 概 述

目前很多产品都广泛用了 FPGA,虽然品种不同,但编程方式几乎都一样:利用专

用的 EPROM 对 FPGA 进行配置。专用的 EPROM 价格不便宜,且大不跟上都是一

次性 OPT 方式编程。一旦更改 FPGA 设计,代价不小。 为了进一步降低产品的成本

和升级成本,可以考虑利用板上现有 CPU 子系统中空闲的 ROM 空间存放 FPGA 的

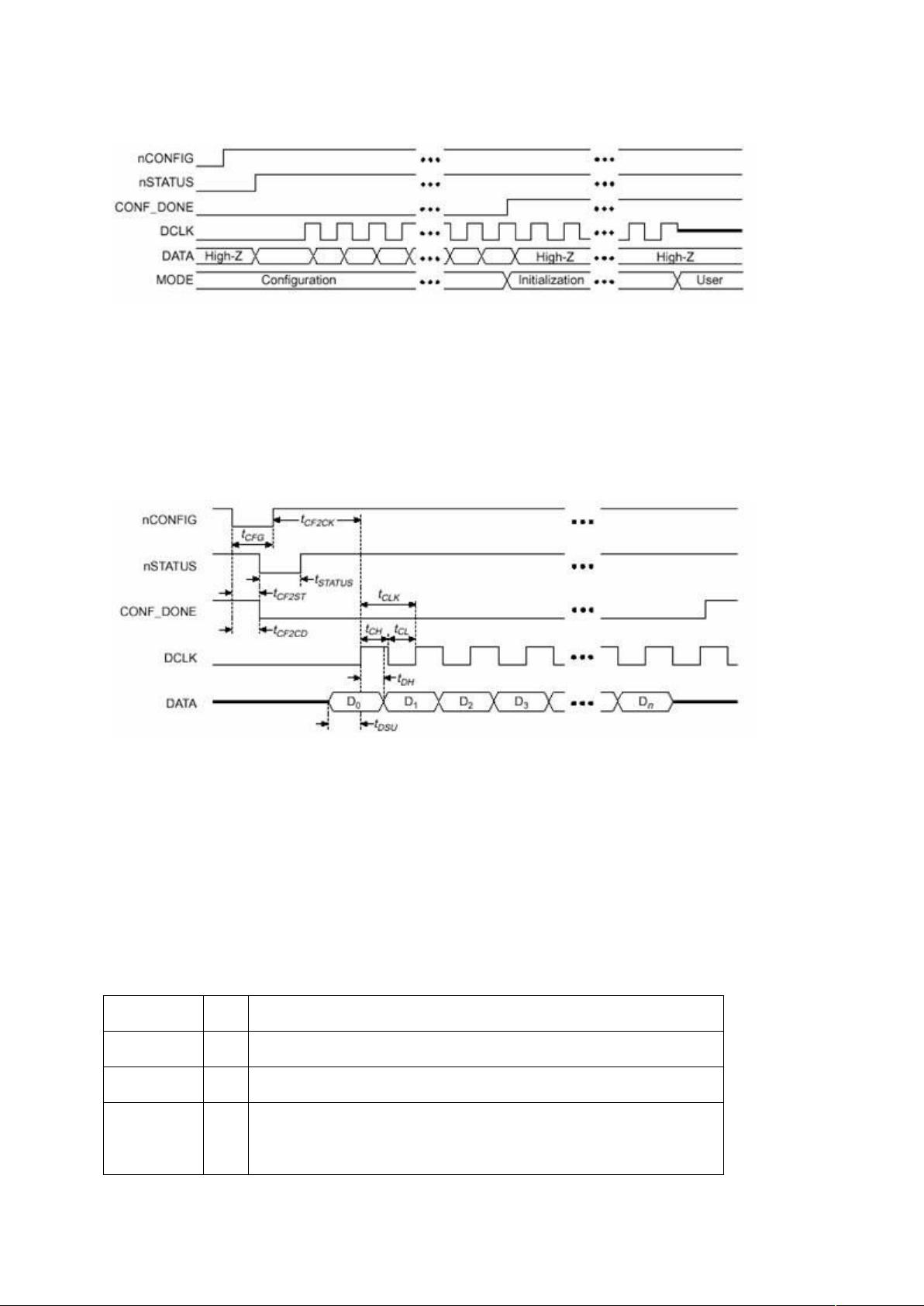

配置数据,并由 CPU 模拟专用 EPROM 对 FPGA 进行配置。 本文将以

PowerPC860 和 EP1K30 为例,讲解如何利用 CPU 来配置 FPGA。

CPU 配置 FPGA 的优点

与 Conguration EPROM 方式相比本设计有如下优点:

1. 降低硬件成本——省去了 FPGA 专用 EPROM 的成本,而几乎不增加其他成本。

以 ALTERA 的 10K 系列为例,板上至少要配一片以上的 EPC1,每片 EPC1 的价格

要几十元,容量 1M 位。提供 1Mb 的存储空间,对于大部分单板来说(如 860 系统

的单板),是不需要增加硬件的。即使增加 1Mb 存储空间,通用存储器也会比

FPGA 专用 EPROM 便宜。

2. 可多次编程——FPGA 专用 EPROM 几乎都是 OTP,一旦更换 FPGA 版本,旧

版本的并不便宜的 EPROM 只能丢弃。如果使用本设计对 FPGA 配置,选用可擦除

的通用存储器保存 FPGA 的编程数据,更换 FPGA 版本,无须付出任何硬件代价。

这也是降低硬件成本的一个方面。

3. 实现真正"现场可编程"--FPGA 的特点就是"现场可编程",只有使用 CPU 对

FPGA 编程才能体现这一特点。如果设计周全的话,单板上的 FPGA 可以做到在线

升级。

4. 减少生产工序--省去了对"FPGA 专用 EPROM"烧结的工序,对提高生产率,降

低生产成本等均有好处。对于双面再流焊的单板,更可省去手工补焊 DIP 器件的工

序。

评论0