没有合适的资源?快使用搜索试试~ 我知道了~

首页Verilog HDL设计的要点.pdf

Verilog HDL设计的要点.pdf

Verilog HDL设计的要点.pdf Verilog HDL设计的要点.pdf Verilog HDL设计的要点.pdf Verilog HDL设计的要点.pdf

资源详情

资源评论

资源推荐

第十章.设计练习进阶

266

设计练习进阶

前言:

在前面九章学习的基础上, 通过本章十个阶段的练习,一定能逐步掌握 Verilog HDL 设计的

要点。我们可以先理解样板模块中每一条语句的作用,然后对样板模块进行综合前和综合后

仿真,再独立完成每一阶段规定的练习。当十个阶段的练习做完后,便可以开始设计一些简

单的逻辑电路和系统。很快我们就能过渡到设计相当复杂的数字逻辑系统。当然,复杂的数

字逻辑系统的设计和验证,不但需要系统结构的知识和经验的积累,还需要了解更多的语法

现象和掌握高级的 Verilog HDL 系统任务,以及与 C 语言模块接口的方法(即 PLI),这些已

超出的本书的范围。有兴趣的同学可以阅读 Verilog 语法参考资料和有关文献,自己学习,

我们将在下一本书中介绍 Verilog 较高级的用法。

练习一.简单的组合逻辑设计

目的: 掌握基本组合逻辑电路的实现方法。

这是一个可综合的数据比较器,很容易看出它的功能是比较数据 a 与数据 b,如果两个

数据相同,则给出结果 1,否则给出结果 0。在 Verilog HDL 中,描述组合逻辑时常使用 assign

结构。注意 equal=(a==b)?1:0,这是一种在组合逻辑实现分支判断时常使用的格式。

模块源代码:

//--------------- compare.v -----------------

module compare(equal,a,b);

input a,b;

output equal;

assign equal=(a==b)?1:0; //a 等于 b 时,equal 输出为 1;a 不等于 b 时,

//equal 输出为 0。

endmodule

测试模块用于检测模块设计得正确与否,它给出模块的输入信号,观察模块的内部信号

和输出信号,如果发现结果与预期的有所偏差,则要对设计模块进行修改。

测试模块源代码:

`timescale 1ns/1ns //定义时间单位。

`include "./compare.v" //包含模块文件。

在有的仿真调试环境中并不需要此语句。

//

而需要从调试环境的菜单中键入有关模块文件的路径和名称

module comparetest;

reg a,b;

wire equal;

initial //initial 常用于仿真时信号的给出。

第十章.设计练习进阶

267

begin

a=0;

b=0;

#100 a=0; b=1;

#100 a=1; b=1;

#100 a=1; b=0;

#100 $stop; //系统任务,暂停仿真以便观察仿真波形。

end

compare compare1(.equal(equal),.a(a),.b(b)); //调用模块。

endmodule

仿真波形(部分):

练习:

设计一个字节(8 位)比较器

。

要求:比较两个字节的大小,如 a[7:0]大于 b[7:0]输出高电平,否则输出低电平,改写测试

模型,使其能进行比较全面的测试 。

练习二. 简单时序逻辑电路的设计

目的:掌握基本时序逻辑电路的实现。

在 Verilog HDL 中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式。在可综

合的 Verilog HDL 模型,我们通常使用 always 块和 @(posedge clk)或 @(negedge clk)的结

构来表述时序逻辑。下面是一个 1/2 分频器的可综合模型。

// half_clk.v:

module half_clk(reset,clk_in,clk_out);

input clk_in,reset;

output clk_out;

reg clk_out;

always @(posedge clk_in)

第十章.设计练习进阶

268

begin

if(!reset) clk_out=0;

else clk_out=~clk_out;

end

endmodule

在 always 块中,被赋值的信号都必须定义为 reg 型,这是由时序逻辑电路的特点所决定的。

对于 reg 型数据,如果未对它进行赋值,仿真工具会认为它是不定态。为了能正确地观察到

仿真结果,在可综合风格的模块中我们通常定义一个复位信号 reset,当 reset 为低电平时,

对电路中的寄存器进行复位。

测试模块的源代码:

//------------------- clk_Top.v -----------------------------

`timescale 1ns/100ps

`define clk_cycle 50

module clk_Top.v

reg clk,reset;

wire clk_out;

always #`clk_cycle clk = ~clk;

initial

begin

clk = 0;

reset = 1;

#100 reset = 0;

#100 reset = 1;

#10000 $stop;

end

half_clk half_clk(.reset(reset),.clk_in(clk),.clk_out(clk_out));

endmodule

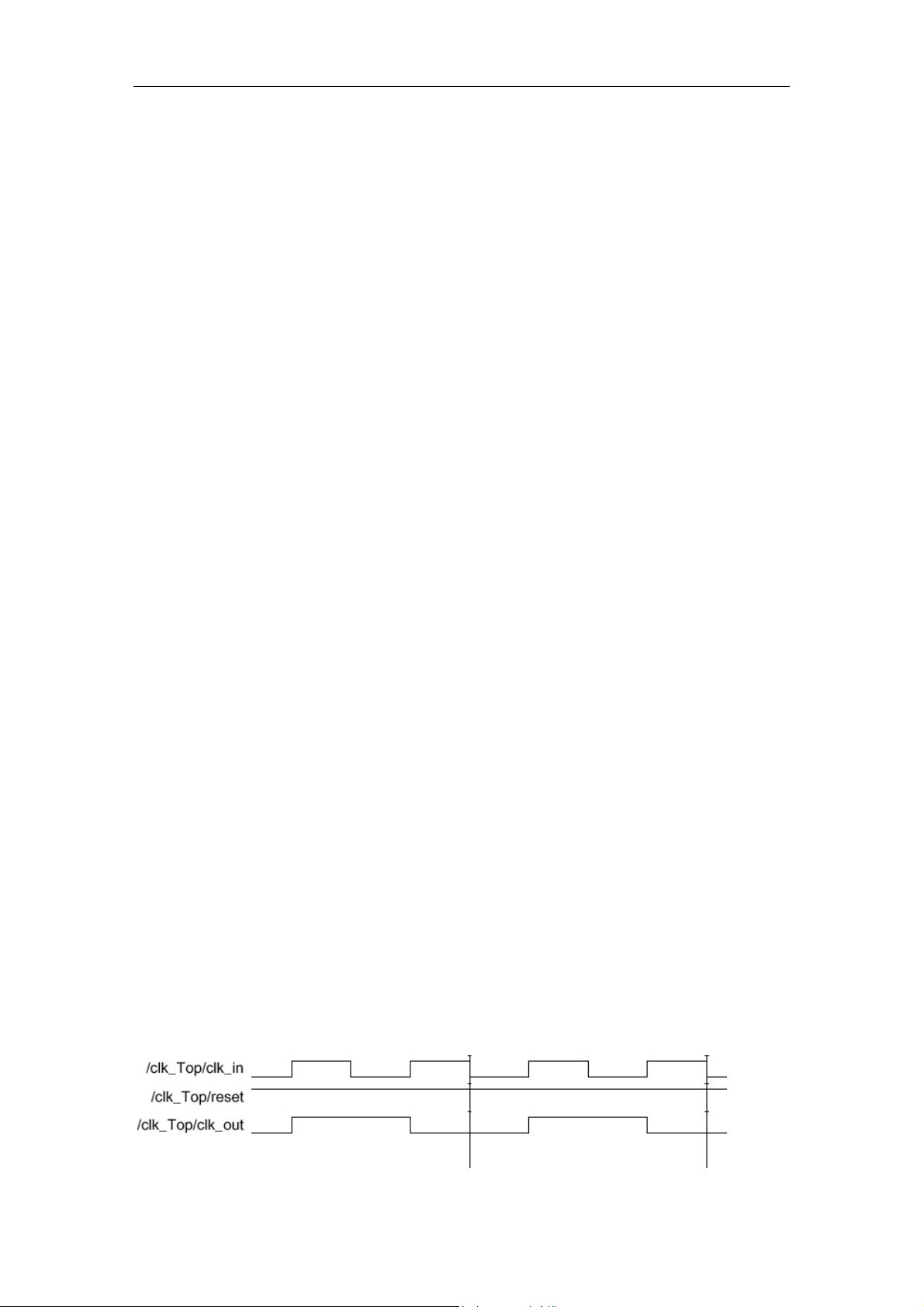

仿真波形:

第十章.设计练习进阶

269

练习:依然作 clk_in 的二分频 clk_out,要求输出与上例的输出正好反相。编写测试模块,

给出仿真波形。

练习三. 利用条件语句实现较复杂的时序逻辑电路

目的:掌握条件语句在 Verilog HDL 中的使用。

与常用的高级程序语言一样,为了描述较为复杂的时序关系,Verilog HDL 提供了条件语

句供分支判断时使用。在可综合风格的 Verilog HDL 模型中常用的条件语句有 if…else 和

case…endcase 两种结构,用法和 C 程序语言中类似。两者相较,if…else 用于不很复杂的

分支关系,实际编写可综合风格的模块、特别是用状态机构成的模块时,更常用的是

case…endcase 风格的代码。这一节我们给的是有关 if…else 的范例,有关 case…endcase

结构的代码已后会经常用到。

下面给出的范例也是一个可综合风格的分频器,是将 10M 的时钟分频为 500K 的时钟。基

本原理与 1/2 分频器是一样的,但是需要定义一个计数器,以便准确获得 1/20 分频

模块源代码:

// --------------- fdivision.v -----------------------------

module fdivision(RESET,F10M,F500K);

input F10M,RESET;

output F500K;

reg F500K;

reg [7:0]j;

always @(posedge F10M)

if(!RESET) //低电平复位。

begin

F500K <= 0;

j <= 0;

end

else

begin

if(j==19) //对计数器进行判断,以确定 F500K 信号是否反转。

begin

j <= 0;

F500K <= ~F500K;

end

else

j <= j+1;

end

endmodule

第十章.设计练习进阶

270

测试模块源代码:

//--------------- fdivision_Top.v ------------------------

`timescale 1ns/100ps

`define clk_cycle 50

module division_Top;

reg F10M_clk,RESET;

wire F500K_clk;

always #`clk_cycle F10M_clk

=

~ F10M_clk;

initial

begin

RESET=1;

F10M=0;

#100 RESET=0;

#100 RESET=1;

#10000 $stop;

end

fdivision fdivision (.RESET(RESET),.F10M(F10M_clk),.F500K(F500K_clk));

endmodule

仿真波形:

练习:利用 10M 的时钟,设计一个单周期形状如下的周期波形。

练习四. 设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别

10μs 20μs

20μs

0

T

剩余25页未读,继续阅读

q042096

- 粉丝: 6

- 资源: 176

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1