1

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

2

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1

ISER[31:16]

ISER0/1[31:0] ISER0/1 64

STM32 60 : ISER0 0~31 ISER1 32~59

STM32F10x_NVIC.h 0 ISCR

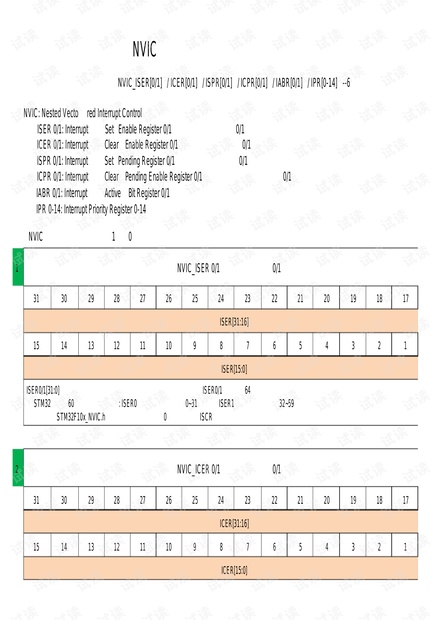

NVIC

NVIC_ISER[0/1] / ICER[0/1] / ISPR[0/1] / ICPR[0/1] / IABR[0/1] / IPR[0-14] --6

NVIC: Nested Vecto red Interrupt Control

ISER 0/1: Interrupt Set Enable Register 0/1 0/1

ICER 0/1: Interrupt Clear Enable Register 0/1 0/1

ISPR 0/1: Interrupt Set Pending Register 0/1 0/1

ICPR 0/1: Interrupt Clear Pending Enable Register 0/1 0/1

IABR 0/1: Interrupt Active Bit Register 0/1

IPR 0-14: Interrupt Priority Register 0-14

NVIC 10

NVIC_ISER 0/1 0/1

ISER[15:0]

NVIC_ICER 0/1 0/1

ICER[31:16]

ICER[15:0]

评论1