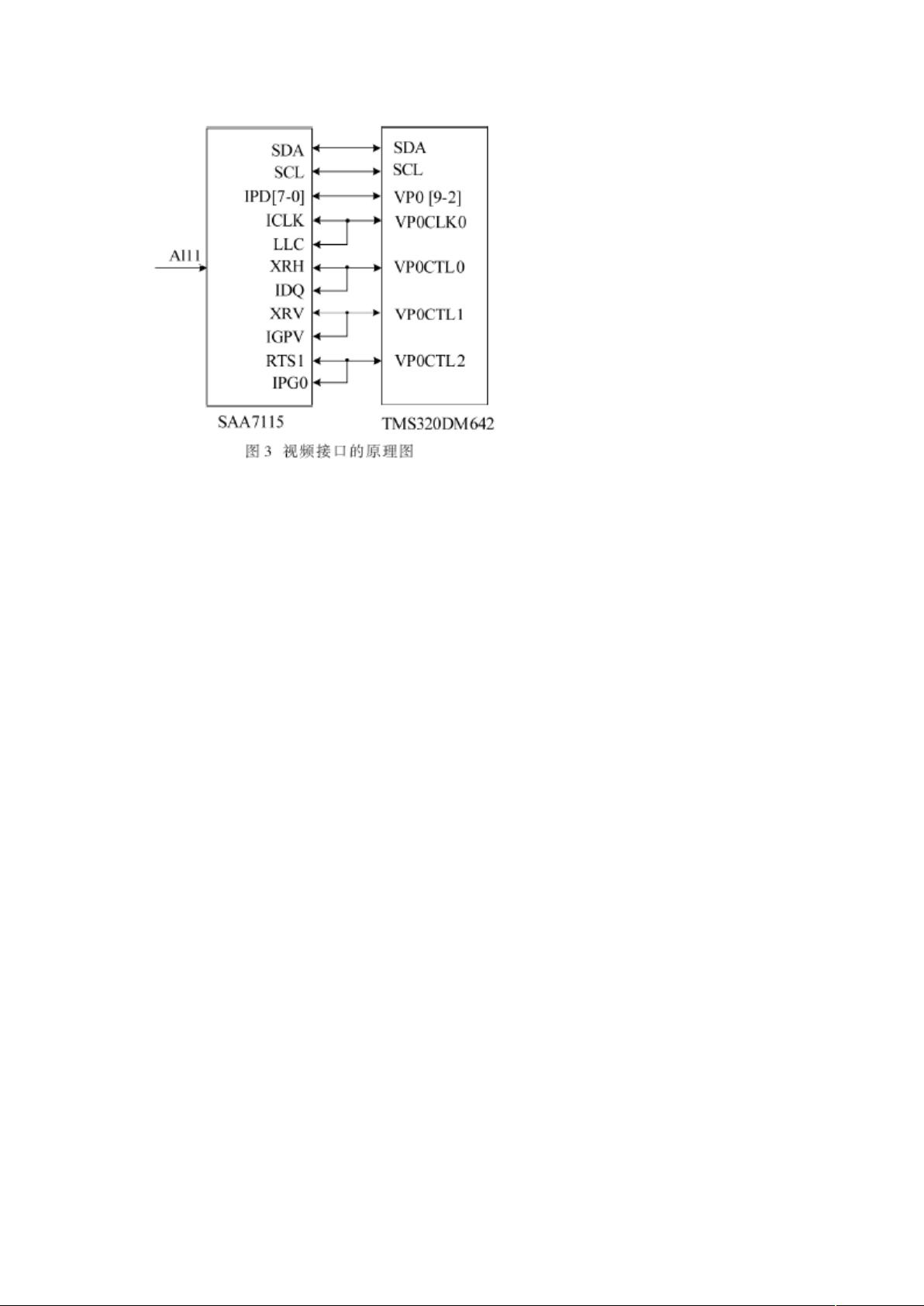

所有这些功能均在 I2C 总线控制下完成。SCL 作为 I2C 接口的时钟线与 TMS320DM642 的 SCL 相连,

SDA 作为 I2C 接口的数据地址线与 TMS320DM642 的 SDA 相连。通过 SCL 和 SDA 的时序配合,可由

TMS320DM642 向 SAA7115 的寄存器写入数据或读出数据。

2.2 TMS320DM642 图像处理模块

本系统中视频口 VP0 作为输入,与视频解码器 SAA7115 的 IPD 相连。从解码器 SAA7115 出来的

BT.656 数据流进入 VP0 口后,经由 BT.656 捕获通道,进入到视频口缓冲区中,每个视频口都有 1 个 5

120 B 的视频输入/输出缓冲区,视频口输人的数据分别进入捕获 FIFO A 和 FIFO B,其中 Y 缓存 2 560

B,Cb 和 Cr 缓存分别为 1 280 B。根据输出的同步脉冲产生帧存储器的地址信号、读写和片选等控制信

号,将图像逐帧存入 SDRAM 存储器中,通过中断通知 TMS320DM642 读取。TMS320DM642 通过

EDMA 事件实现视频口缓冲区和片内 L2 存储器之间的数据传递。用户编程设定 1 个缓冲区阈值用以产生

EDMA 事件。BT.656 格式的数据流经由捕获通道分别进入各自的缓冲区,并打包成 64 B 的双字。当双

字增至缓冲区阈值时触发 EDMA 事件,存储器映射寄存器即作为 EDMA 数据传输的源地址。为保证每一

场的数据能够全部传完且没有遗漏,每次 EDMA 传输的数据大小应等于阈值。由于 TMS320DM642 的

强大处理能力,用户算法作为任务线程嵌入 TMS320DM642 软件系统中。

2.3 外围存储模块

本系统的 TMS320DM642 在视频图像的处理时,处理过程中会产生大量数据,而其内部最多仅有 256

KB 的 RAM,所以需要扩展大容量的外部存储器才能满足数据处理的需要。本系统选用 2 片 SDRAM 用于

存储程序、数据和缓存数字视频信息,选用 1 片 FLASH 存储器用于固化程序和一些掉电后仍需保存的用

户数据。SDRAM 芯片和 FLASH 芯片均通过 TMS320DM642 的 EMIF 口实现无缝连接

[3]。TMS320DM642 的 EMIF 有 4 个独立的可设定地址的区域,称为芯片使能空间(CE0~CE3),当

评论1