没有合适的资源?快使用搜索试试~ 我知道了~

首页MT40A2G4 MT40A1G8 MT40A512M16 DDR4 SDRAM 数据手册.pdf

资源详情

资源评论

资源推荐

DDR4 SDRAM

MT40A2G4

MT40A1G8

MT40A512M16

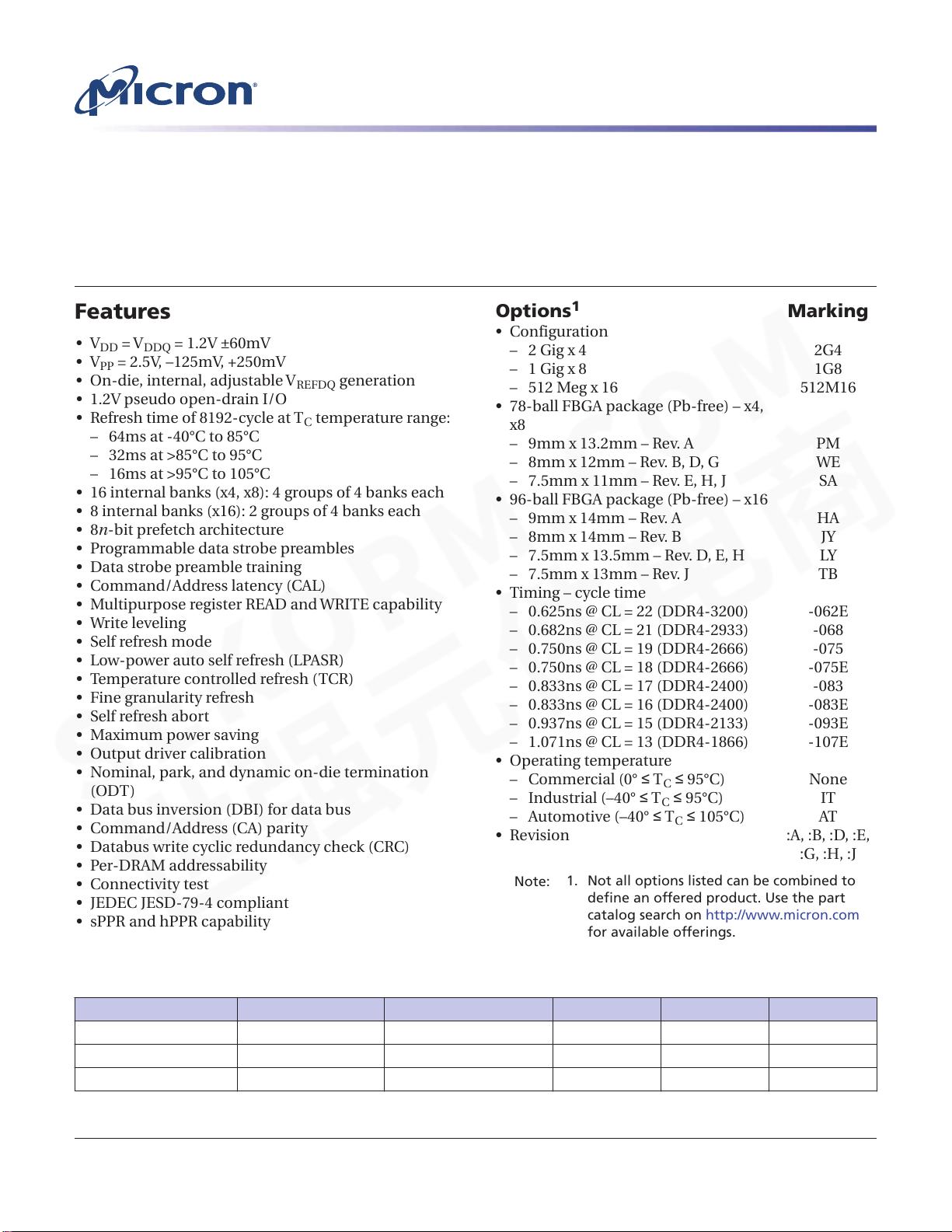

Features

•V

DD

= V

DDQ

= 1.2V ±60mV

•V

PP

= 2.5V, –125mV, +250mV

• On-die, internal, adjustable V

REFDQ

generation

• 1.2V pseudo open-drain I/O

• Refresh time of 8192-cycle at T

C

temperature range:

– 64ms at -40°C to 85°C

– 32ms at >85°C to 95°C

– 16ms at >95°C to 105°C

• 16 internal banks (x4, x8): 4 groups of 4 banks each

• 8 internal banks (x16): 2 groups of 4 banks each

•8n-bit prefetch architecture

• Programmable data strobe preambles

• Data strobe preamble training

• Command/Address latency (CAL)

• Multipurpose register READ and WRITE capability

• Write leveling

• Self refresh mode

• Low-power auto self refresh (LPASR)

• Temperature controlled refresh (TCR)

• Fine granularity refresh

• Self refresh abort

• Maximum power saving

• Output driver calibration

• Nominal, park, and dynamic on-die termination

(ODT)

• Data bus inversion (DBI) for data bus

• Command/Address (CA) parity

• Databus write cyclic redundancy check (CRC)

• Per-DRAM addressability

• Connectivity test

• JEDEC JESD-79-4 compliant

• sPPR and hPPR capability

Options

1

Marking

• Configuration

– 2 Gig x 4 2G4

– 1 Gig x 8 1G8

– 512 Meg x 16 512M16

• 78-ball FBGA package (Pb-free) – x4,

x8

– 9mm x 13.2mm – Rev. A PM

– 8mm x 12mm – Rev. B, D, G WE

– 7.5mm x 11mm – Rev. E, H, J SA

• 96-ball FBGA package (Pb-free) – x16

– 9mm x 14mm – Rev. A HA

– 8mm x 14mm – Rev. B JY

– 7.5mm x 13.5mm – Rev. D, E, H LY

– 7.5mm x 13mm – Rev. J TB

• Timing – cycle time

– 0.625ns @ CL = 22 (DDR4-3200) -062E

– 0.682ns @ CL = 21 (DDR4-2933) -068

– 0.750ns @ CL = 19 (DDR4-2666) -075

– 0.750ns @ CL = 18 (DDR4-2666) -075E

– 0.833ns @ CL = 17 (DDR4-2400) -083

– 0.833ns @ CL = 16 (DDR4-2400) -083E

– 0.937ns @ CL = 15 (DDR4-2133) -093E

– 1.071ns @ CL = 13 (DDR4-1866) -107E

• Operating temperature

– Commercial (0° ื T

C

ื 95°C) None

– Industrial (–40° ื T

C

ื 95°C) IT

– Automotive (–40° ื T

C

ื 105°C) AT

• Revision :A, :B, :D, :E,

:G, :H, :J

Note:

1. Not all options listed can be combined to

define an offered product. Use the part

catalog search on http://www.micron.com

for available offerings.

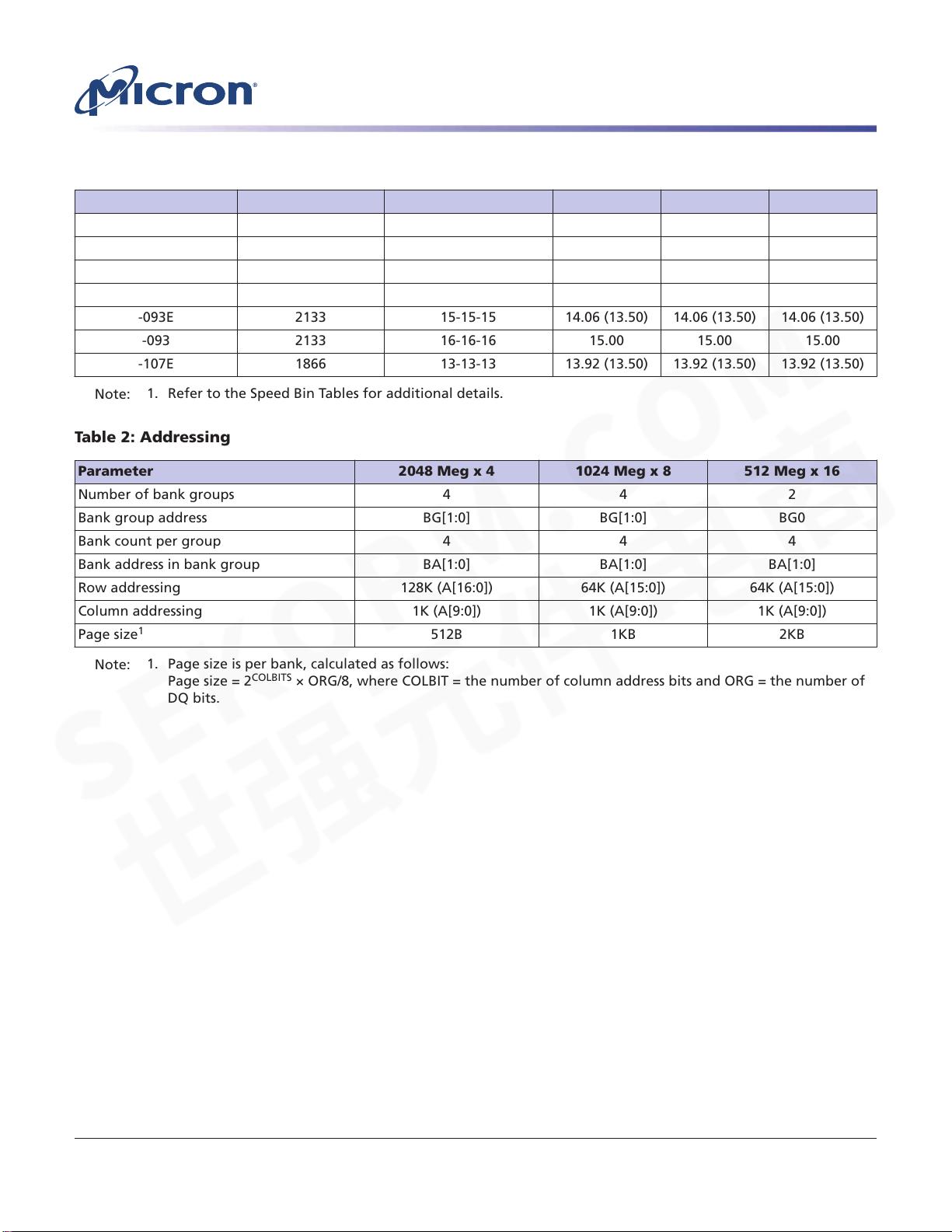

Table 1: Key Timing Parameters

Speed Grade

1

Data Rate (MT/s) Target CL-nRCD-nRP

t

AA (ns)

t

RCD (ns)

t

RP (ns)

-062Y 3200 22-22-22 13.75 (13.32) 13.75 (13.32) 13.75 (13.32)

-062E 3200 22-22-22 13.75 13.75 13.75

-068 2933 21-21-21 14.32 (13.75) 14.32 (13.75) 14.32 (13.75)

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. P 04/19 EN

1

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

Products and specifications discussed herein are subject to change by Micron without notice.

Table 1: Key Timing Parameters (Continued)

Speed Grade

1

Data Rate (MT/s) Target CL-nRCD-nRP

t

AA (ns)

t

RCD (ns)

t

RP (ns)

-075E 2666 18-18-18 13.50 13.50 13.50

-075 2666 19-19-19 14.25 (13.75) 14.25 (13.75) 14.25 (13.75)

-083E 2400 16-16-16 13.32 13.32 13.32

-083 2400 17-17-17 14.16 (13.75) 14.16 (13.75) 14.16 (13.75)

-093E 2133 15-15-15 14.06 (13.50) 14.06 (13.50) 14.06 (13.50)

-093 2133 16-16-16 15.00 15.00 15.00

-107E 1866 13-13-13 13.92 (13.50) 13.92 (13.50) 13.92 (13.50)

Note:

1. Refer to the Speed Bin Tables for additional details.

Table 2: Addressing

Parameter 2048 Meg x 4 1024 Meg x 8 512 Meg x 16

Number of bank groups 4 4 2

Bank group address BG[1:0] BG[1:0] BG0

Bank count per group 4 4 4

Bank address in bank group BA[1:0] BA[1:0] BA[1:0]

Row addressing 128K (A[16:0]) 64K (A[15:0]) 64K (A[15:0])

Column addressing 1K (A[9:0]) 1K (A[9:0]) 1K (A[9:0])

Page size

1

512B 1KB 2KB

Note:

1. Page size is per bank, calculated as follows:

Page size = 2

COLBITS

× ORG/8, where COLBIT = the number of column address bits and ORG = the number of

DQ bits.

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. P 04/19 EN

2

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

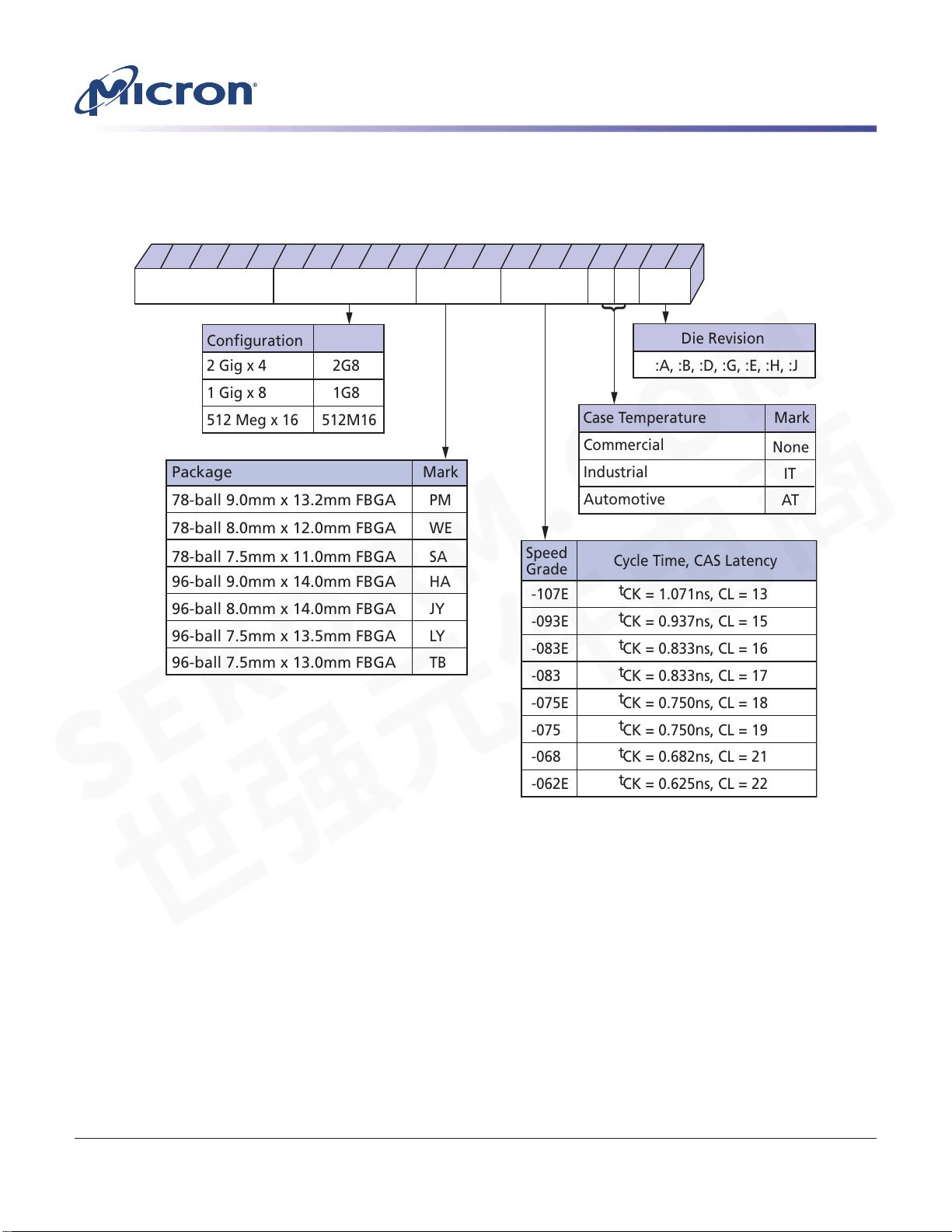

Figure 1: Order Part Number Example

Example Part Number: MT40A1G8WE-083:D

Configuration

2 Gig x 4 2G8

1 Gig x 8

512 Meg x 16

1G8

512M16

-

Configuration

MT40A

Package Speed

Revision

:

{

Package

Mark

78-ball 9.0mm x 13.2mm FBGA

PM

78-ball 8.0mm x 12.0mm FBGA

WE

78-ball 7.5mm x 11.0mm FBGA

SA

96-ball 9.0mm x 14.0mm FBGA

HA

96-ball 8.0mm x 14.0mm FBGA

JY

96-ball 7.5mm x 13.5mm FBGA

LY

96-ball 7.5mm x 13.0mm FBGA

TB

:A, :B, :D, :G, :E, :H, :J

Die Revision

Speed

Grade

-107E

-093E

t

CK = 1.071ns, CL = 13

t

CK = 0.937ns, CL = 15

-083E

t

CK = 0.833ns, CL = 16

-083

t

CK = 0.833ns, CL = 17

-075E

t

CK = 0.750ns, CL = 18

-075

t

CK = 0.750ns, CL = 19

-068

t

t

CK = 0.682ns, CL = 21

-062E CK = 0.625ns, CL = 22

Cycle Time, CAS Latency

Commercial

Industrial

Automotive

None

IT

AT

Case Temperature Mark

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. P 04/19 EN

3

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

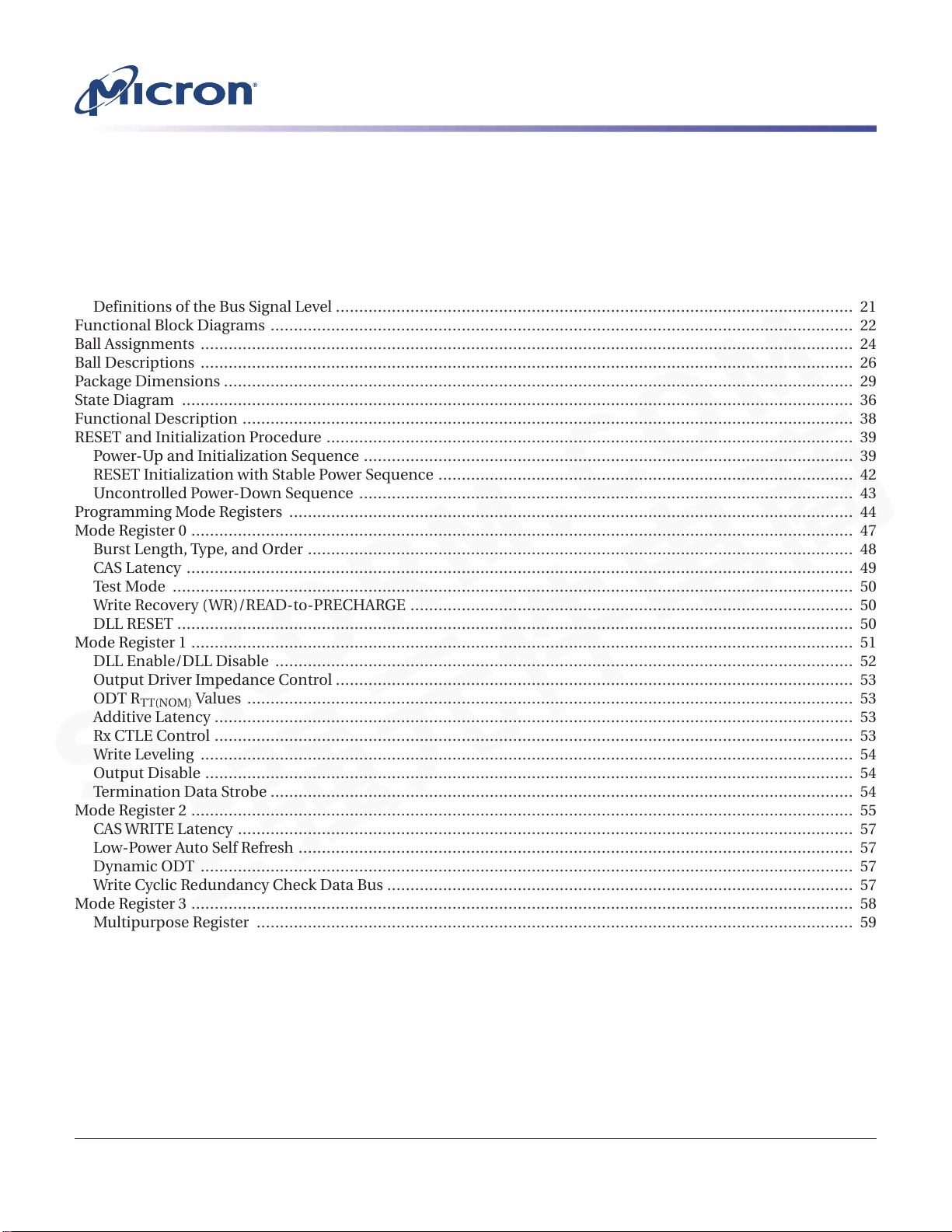

Contents

Important Notes and Warnings ....................................................................................................................... 19

General Notes and Description ....................................................................................................................... 19

Description ................................................................................................................................................ 19

Industrial Temperature ............................................................................................................................... 20

Automotive Temperature ............................................................................................................................ 20

General Notes ............................................................................................................................................ 20

Definitions of the Device-Pin Signal Level ................................................................................................... 21

Definitions of the Bus Signal Level ............................................................................................................... 21

Functional Block Diagrams ............................................................................................................................. 22

Ball Assignments ............................................................................................................................................ 24

Ball Descriptions ............................................................................................................................................ 26

Package Dimensions ....................................................................................................................................... 29

State Diagram ................................................................................................................................................ 36

Functional Description ................................................................................................................................... 38

RESET and Initialization Procedure ................................................................................................................. 39

Power-Up and Initialization Sequence ......................................................................................................... 39

RESET Initialization with Stable Power Sequence ......................................................................................... 42

Uncontrolled Power-Down Sequence .......................................................................................................... 43

Programming Mode Registers ......................................................................................................................... 44

Mode Register 0 .............................................................................................................................................. 47

Burst Length, Type, and Order ..................................................................................................................... 48

CAS Latency ............................................................................................................................................... 49

Test Mode .................................................................................................................................................. 50

Write Recovery (WR)/READ-to-PRECHARGE ............................................................................................... 50

DLL RESET ................................................................................................................................................. 50

Mode Register 1 .............................................................................................................................................. 51

DLL Enable/DLL Disable ............................................................................................................................ 52

Output Driver Impedance Control ............................................................................................................... 53

ODT R

TT(NOM)

Values .................................................................................................................................. 53

Additive Latency ......................................................................................................................................... 53

Rx CTLE Control ......................................................................................................................................... 53

Write Leveling ............................................................................................................................................ 54

Output Disable ........................................................................................................................................... 54

Termination Data Strobe ............................................................................................................................. 54

Mode Register 2 .............................................................................................................................................. 55

CAS WRITE Latency .................................................................................................................................... 57

Low-Power Auto Self Refresh ....................................................................................................................... 57

Dynamic ODT ............................................................................................................................................ 57

Write Cyclic Redundancy Check Data Bus .................................................................................................... 57

Mode Register 3 .............................................................................................................................................. 58

Multipurpose Register ................................................................................................................................ 59

WRITE Command Latency When CRC/DM is Enabled ................................................................................. 60

Fine Granularity Refresh Mode .................................................................................................................... 60

Temperature Sensor Status ......................................................................................................................... 60

Per-DRAM Addressability ........................................................................................................................... 60

Gear-Down Mode ....................................................................................................................................... 60

Mode Register 4 .............................................................................................................................................. 61

Hard Post Package Repair Mode .................................................................................................................. 62

Soft Post Package Repair Mode .................................................................................................................... 62

WRITE Preamble ........................................................................................................................................ 63

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. P 04/19 EN

4

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

READ Preamble .......................................................................................................................................... 63

READ Preamble Training ............................................................................................................................ 63

Temperature-Controlled Refresh ................................................................................................................. 63

Command Address Latency ........................................................................................................................ 63

Internal V

REF

Monitor ................................................................................................................................. 63

Maximum Power Savings Mode ................................................................................................................... 64

Mode Register 5 .............................................................................................................................................. 65

Data Bus Inversion ..................................................................................................................................... 66

Data Mask .................................................................................................................................................. 67

CA Parity Persistent Error Mode .................................................................................................................. 67

ODT Input Buffer for Power-Down .............................................................................................................. 67

CA Parity Error Status ................................................................................................................................. 67

CRC Error Status ......................................................................................................................................... 67

CA Parity Latency Mode .............................................................................................................................. 67

Mode Register 6 .............................................................................................................................................. 68

t

CCD_L Programming ................................................................................................................................. 69

V

REFDQ

Calibration Enable .......................................................................................................................... 69

V

REFDQ

Calibration Range ........................................................................................................................... 69

V

REFDQ

Calibration Value ............................................................................................................................ 70

Truth Tables ................................................................................................................................................... 71

NOP Command .............................................................................................................................................. 74

DESELECT Command .................................................................................................................................... 74

DLL-Off Mode ................................................................................................................................................ 74

DLL-On/Off Switching Procedures .................................................................................................................. 76

DLL Switch Sequence from DLL-On to DLL-Off ........................................................................................... 76

DLL-Off to DLL-On Procedure .................................................................................................................... 78

Input Clock Frequency Change ....................................................................................................................... 79

Write Leveling ................................................................................................................................................ 80

DRAM Setting for Write Leveling and DRAM TERMINATION Function in that Mode ..................................... 81

Procedure Description ................................................................................................................................ 82

Write Leveling Mode Exit ............................................................................................................................ 83

Command Address Latency ............................................................................................................................ 85

Low-Power Auto Self Refresh Mode ................................................................................................................. 90

Manual Self Refresh Mode .......................................................................................................................... 90

Multipurpose Register .................................................................................................................................... 92

MPR Reads ................................................................................................................................................. 93

MPR Readout Format ................................................................................................................................. 95

MPR Readout Serial Format ........................................................................................................................ 95

MPR Readout Parallel Format ..................................................................................................................... 96

MPR Readout Staggered Format .................................................................................................................. 97

MPR READ Waveforms ............................................................................................................................... 98

MPR Writes ............................................................................................................................................... 100

MPR WRITE Waveforms ............................................................................................................................. 101

MPR REFRESH Waveforms ........................................................................................................................ 102

Gear-Down Mode .......................................................................................................................................... 105

Maximum Power-Saving Mode ....................................................................................................................... 108

Maximum Power-Saving Mode Entry .......................................................................................................... 108

Maximum Power-Saving Mode Entry in PDA .............................................................................................. 109

CKE Transition During Maximum Power-Saving Mode ................................................................................ 109

Maximum Power-Saving Mode Exit ............................................................................................................ 109

Command/Address Parity .............................................................................................................................. 111

Per-DRAM Addressability .............................................................................................................................. 119

8Gb: x4, x8, x16 DDR4 SDRAM

Features

CCMTD-1725822587-9875

8gb_ddr4_dram.pdf - Rev. P 04/19 EN

5

Micron Technology, Inc. reserves the right to change products or specifications without notice.

2015 Micron Technology, Inc. All rights reserved.

剩余395页未读,继续阅读

下一个雨天

- 粉丝: 18

- 资源: 10

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- RTL8188FU-Linux-v5.7.4.2-36687.20200602.tar(20765).gz

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0