没有合适的资源?快使用搜索试试~ 我知道了~

首页时钟同步芯片dp83640技术文档

资源详情

资源评论

资源推荐

February 26, 2008

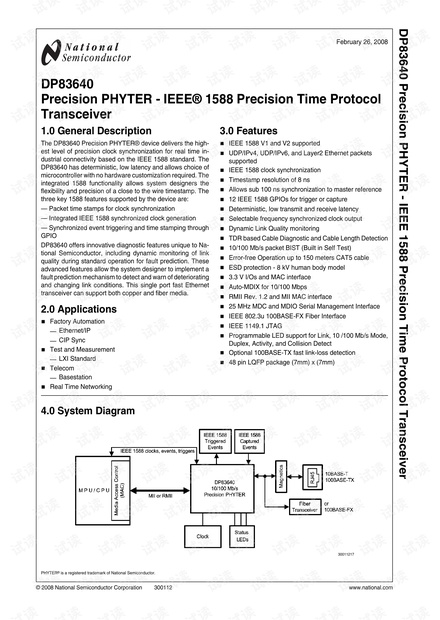

DP83640

Precision PHYTER - IEEE® 1588 Precision Time Protocol

Transceiver

1.0 General Description

The DP83640 Precision PHYTER® device delivers the high-

est level of precision clock synchronization for real time in-

dustrial connectivity based on the IEEE 1588 standard. The

DP83640 has deterministic, low latency and allows choice of

microcontroller with no hardware customization required. The

integrated 1588 functionality allows system designers the

flexibility and precision of a close to the wire timestamp. The

three key 1588 features supported by the device are:

— Packet time stamps for clock synchronization

— Integrated IEEE 1588 synchronized clock generation

— Synchronized event triggering and time stamping through

GPIO

DP83640 offers innovative diagnostic features unique to Na-

tional Semiconductor, including dynamic monitoring of link

quality during standard operation for fault prediction. These

advanced features allow the system designer to implement a

fault prediction mechanism to detect and warn of deteriorating

and changing link conditions. This single port fast Ethernet

transceiver can support both copper and fiber media.

2.0 Applications

■

Factory Automation

—

Ethernet/IP

—

CIP Sync

■

Test and Measurement

—

LXI Standard

■

Telecom

—

Basestation

■

Real Time Networking

3.0 Features

■

IEEE 1588 V1 and V2 supported

■

UDP/IPv4, UDP/IPv6, and Layer2 Ethernet packets

supported

■

IEEE 1588 clock synchronization

■

Timestamp resolution of 8 ns

■

Allows sub 100 ns synchronization to master reference

■

12 IEEE 1588 GPIOs for trigger or capture

■

Deterministic, low transmit and receive latency

■

Selectable frequency synchronized clock output

■

Dynamic Link Quality monitoring

■

TDR based Cable Diagnostic and Cable Length Detection

■

10/100 Mb/s packet BIST (Built in Self Test)

■

Error-free Operation up to 150 meters CAT5 cable

■

ESD protection - 8 kV human body model

■

3.3 V I/Os and MAC interface

■

Auto-MDIX for 10/100 Mbps

■

RMII Rev. 1.2 and MII MAC interface

■

25 MHz MDC and MDIO Serial Management Interface

■

IEEE 802.3u 100BASE-FX Fiber Interface

■

IEEE 1149.1 JTAG

■

Programmable LED support for Link, 10 /100 Mb/s Mode,

Duplex, Activity, and Collision Detect

■

Optional 100BASE-TX fast link-loss detection

■

48 pin LQFP package (7mm) x (7mm)

4.0 System Diagram

30011217

PHYTER

®

is a registered trademark of National Semiconductor.

© 2008 National Semiconductor Corporation 300112 www.national.com

DP83640 Precision PHYTER - IEEE 1588 Precision Time Protocol Transceiver

Table of Contents

1.0 General Description ......................................................................................................................... 1

2.0 Applications .................................................................................................................................... 1

3.0 Features ........................................................................................................................................ 1

4.0 System Diagram .............................................................................................................................. 1

5.0 Block Diagram ................................................................................................................................ 6

6.0 Key IEEE 1588 Features .................................................................................................................. 6

6.1 IEEE 1588 SYNCHRONIZED CLOCK .............................................................................................. 7

6.1.1 IEEE 1588 Clock Output ............................................................................................................ 7

6.1.2 IEEE 1588 Clock Input .............................................................................................................. 8

6.2 PACKET TIMESTAMPS ................................................................................................................ 8

6.2.1 IEEE 1588 Transmit Packet Parser and Timestamp ....................................................................... 8

6.2.1.1 One-Step Operation ............................................................................................................. 8

6.2.2 IEEE 1588 Receive Packet Parser and Timestamp ....................................................................... 8

6.2.2.1 Receive Timestamp Insertion ................................................................................................. 8

6.2.3 NTP Packet Timestamp ............................................................................................................. 8

6.3 EVENT TRIGGERING AND TIMESTAMPING ................................................................................... 8

6.3.1 IEEE 1588 Event Triggering ....................................................................................................... 8

6.3.2 IEEE 1588 Event Timestamping ................................................................................................. 8

6.4 PTP INTERRUPTS ........................................................................................................................ 8

6.5 GPIO ........................................................................................................................................... 8

7.0 Pin Layout ...................................................................................................................................... 9

8.0 Pin Descriptions ............................................................................................................................ 10

8.1 SERIAL MANAGEMENT INTERFACE ........................................................................................... 10

8.2 MAC DATA INTERFACE .............................................................................................................. 10

8.3 CLOCK INTERFACE ................................................................................................................... 12

8.4 LED INTERFACE ........................................................................................................................ 13

8.5 IEEE 1588 EVENT/TRIGGER/CLOCK INTERFACE ......................................................................... 13

8.6 JTAG INTERFACE ...................................................................................................................... 13

8.7 RESET AND POWER DOWN ....................................................................................................... 14

8.8 STRAP OPTIONS ....................................................................................................................... 15

8.9 10 Mb/s AND 100 Mb/s PMD INTERFACE ...................................................................................... 16

8.10 POWER SUPPLY PINS .............................................................................................................. 17

8.11 PACKAGE PIN ASSIGNMENTS .................................................................................................. 17

9.0 Configuration ................................................................................................................................ 18

9.1 MEDIA CONFIGURATION ............................................................................................................ 18

9.2 AUTO-NEGOTIATION ................................................................................................................. 18

9.2.1 Auto-Negotiation Pin Control .................................................................................................... 18

9.2.2 Auto-Negotiation Register Control ............................................................................................. 18

9.2.3 Auto-Negotiation Parallel Detection ........................................................................................... 19

9.2.4 Auto-Negotiation Restart .......................................................................................................... 19

9.2.5 Enabling Auto-Negotiation via Software ..................................................................................... 19

9.2.6 Auto-Negotiation Complete Time .............................................................................................. 19

9.3 AUTO-MDIX ............................................................................................................................... 19

9.4 PHY ADDRESS .......................................................................................................................... 19

9.4.1 MII Isolate Mode ..................................................................................................................... 19

9.4.2 Broadcast Mode ..................................................................................................................... 20

9.5 LED INTERFACE ........................................................................................................................ 20

9.5.1 LEDs ..................................................................................................................................... 21

9.5.2 LED Direct Control .................................................................................................................. 21

9.6 HALF DUPLEX vs. FULL DUPLEX ................................................................................................ 21

9.7 INTERNAL LOOPBACK ............................................................................................................... 21

9.8 POWER DOWN/INTERRUPT ....................................................................................................... 21

9.8.1 Power Down Control Mode ...................................................................................................... 21

9.8.2 Interrupt Mechanisms .............................................................................................................. 22

9.9 ENERGY DETECT MODE ............................................................................................................ 22

9.10 LINK DIAGNOSTIC CAPABILITIES ............................................................................................. 22

9.10.1 Linked Cable Status .............................................................................................................. 22

9.10.1.1 Polarity Reversal .............................................................................................................. 22

9.10.1.2 Cable Swap Indication ...................................................................................................... 22

9.10.1.3 100 Mb Cable Length Estimation ........................................................................................ 22

9.10.1.4 Frequency Offset Relative to Link Partner ............................................................................ 22

9.10.1.5 Cable Signal Quality Estimation .......................................................................................... 22

9.10.2 Link Quality Monitor ............................................................................................................... 22

9.10.2.1 Link Quality Monitor Control and Status ............................................................................... 23

www.national.com 2

DP83640

9.10.2.2 Checking Current Parameter Values ................................................................................... 23

9.10.2.3 Threshold Control ............................................................................................................. 23

9.10.3 TDR Cable Diagnostics .......................................................................................................... 23

9.10.4 TDR Pulse Generator ............................................................................................................ 23

9.10.5 TDR Pulse Monitor ................................................................................................................ 24

9.10.6 TDR Control Interface ............................................................................................................ 24

9.10.7 TDR Results ......................................................................................................................... 24

9.11 BIST ........................................................................................................................................ 24

10.0 MAC Interface ............................................................................................................................. 24

10.1 MII INTERFACE ........................................................................................................................ 24

10.1.1 Nibble-wide MII Data Interface ................................................................................................ 25

10.1.2 Collision Detect ..................................................................................................................... 25

10.1.3 Carrier Sense ....................................................................................................................... 25

10.2 REDUCED MII INTERFACE ....................................................................................................... 25

10.2.1 RMII Master Mode ................................................................................................................. 26

10.2.2 RMII Slave Mode .................................................................................................................. 26

10.3 SINGLE CLOCK MII MODE ........................................................................................................ 26

10.4 IEEE 802.3u MII SERIAL MANAGEMENT INTERFACE .................................................................. 26

10.4.1 Serial Management Register Access ....................................................................................... 26

10.4.2 Serial Management Access Protocol ........................................................................................ 26

10.4.3 Serial Management Preamble Suppression .............................................................................. 27

10.5 PHY CONTROL FRAMES .......................................................................................................... 27

10.6 PHY STATUS FRAMES ............................................................................................................. 28

11.0 Architecture ................................................................................................................................ 28

11.1 100BASE-TX TRANSMITTER ..................................................................................................... 28

11.1.1 Code-Group Encoding and Injection ........................................................................................ 30

11.1.2 Scrambler ............................................................................................................................ 30

11.1.3 NRZ to NRZI Encoder ............................................................................................................ 31

11.1.4 Binary to MLT-3 Convertor ..................................................................................................... 31

11.2 100BASE-TX RECEIVER ........................................................................................................... 31

11.2.1 Analog Front End .................................................................................................................. 31

11.2.2 Digital Signal Processor ......................................................................................................... 31

11.2.2.1 Base Line Wander Compensation ....................................................................................... 32

11.2.2.2 Digital Adaptive Equalization and Gain Control ..................................................................... 32

11.2.3 Signal Detect ........................................................................................................................ 32

11.2.4 MLT-3 to Binary Decoder ....................................................................................................... 32

11.2.5 Clock Recovery Module ......................................................................................................... 33

11.2.6 NRZI to NRZ Decoder ........................................................................................................... 33

11.2.7 Serial to Parallel ................................................................................................................... 33

11.2.8 Descrambler ......................................................................................................................... 33

11.2.9 Code-Group Alignment .......................................................................................................... 33

11.2.10 4B/5B Decoder ................................................................................................................... 33

11.2.11 100BASE-TX Link Integrity Monitor ........................................................................................ 33

11.2.12 Bad SSD Detection .............................................................................................................. 33

11.3 100BASE-FX OPERATION ......................................................................................................... 33

11.3.1 100BASE-FX Transmit ........................................................................................................... 33

11.3.2 100BASE-FX Receive ........................................................................................................... 33

11.3.3 Far-End Fault ....................................................................................................................... 33

11.4 10BASE-T TRANSCEIVER MODULE .......................................................................................... 34

11.4.1 Operational Modes ................................................................................................................ 34

11.4.2 Smart Squelch ...................................................................................................................... 34

11.4.3 Collision Detection and SQE ................................................................................................... 34

11.4.4 Carrier Sense ....................................................................................................................... 35

11.4.5 Normal Link Pulse Detection/Generation .................................................................................. 35

11.4.6 Jabber Function .................................................................................................................... 35

11.4.7 Automatic Link Polarity Detection and Correction ....................................................................... 35

11.4.8 Transmit and Receive Filtering ................................................................................................ 35

11.4.9 Transmitter ........................................................................................................................... 35

11.4.10 Receiver ............................................................................................................................ 35

12.0 Reset Operation .......................................................................................................................... 35

12.1 HARDWARE RESET ................................................................................................................. 35

12.2 FULL SOFTWARE RESET ......................................................................................................... 35

12.3 SOFT RESET ........................................................................................................................... 35

12.4 PTP RESET .............................................................................................................................. 35

13.0 Design Guidelines ....................................................................................................................... 36

13.1 TPI NETWORK CIRCUIT ............................................................................................................ 36

3 www.national.com

DP83640

13.2 FIBER NETWORK CIRCUIT ....................................................................................................... 37

13.3 ESD PROTECTION ................................................................................................................... 37

13.4 CLOCK IN (X1) RECOMMENDATIONS ........................................................................................ 37

14.0 Register Block ............................................................................................................................. 39

14.1 REGISTER DEFINITION ............................................................................................................ 45

14.1.1 Basic Mode Control Register (BMCR) ...................................................................................... 46

14.1.2 Basic Mode Status Register (BMSR) ....................................................................................... 48

14.1.3 PHY Identifier Register #1 (PHYIDR1) ..................................................................................... 49

14.1.4 PHY Identifier Register #2 (PHYIDR2) ..................................................................................... 49

14.1.5 Auto-Negotiation Advertisement Register (ANAR) ..................................................................... 50

14.1.6 Auto-Negotiation Link Partner Ability Register (ANLPAR) (BASE Page) ........................................ 51

14.1.7 Auto-Negotiation Link Partner Ability Register (ANLPAR) (Next Page) .......................................... 52

14.1.8 Auto-Negotiate Expansion Register (ANER) ............................................................................. 52

14.1.9 Auto-Negotiation Next Page Transmit Register (ANNPTR) .......................................................... 53

14.1.10 PHY Status Register (PHYSTS) ............................................................................................ 54

14.1.11 MII Interrupt Control Register (MICR) ..................................................................................... 56

14.1.12 MII Interrupt Status and Event Control Register (MISR) ............................................................ 57

14.1.13 Page Select Register (PAGESEL) ......................................................................................... 59

14.2 EXTENDED REGISTERS - PAGE 0 ............................................................................................. 59

14.2.1 False Carrier Sense Counter Register (FCSCR) ........................................................................ 59

14.2.2 Receiver Error Counter Register (RECR) ................................................................................. 59

14.2.3 100 Mb/s PCS Configuration and Status Register (PCSR) .......................................................... 60

14.2.4 RMII and Bypass Register (RBR) ............................................................................................ 61

14.2.5 LED Direct Control Register (LEDCR) ...................................................................................... 62

14.2.6 PHY Control Register (PHYCR) .............................................................................................. 63

14.2.7 10Base-T Status/Control Register (10BTSCR) .......................................................................... 65

14.2.8 CD Test and BIST Extensions Register (CDCTRL1) .................................................................. 66

14.2.9 PHY Control Register 2 (PHYCR2) .......................................................................................... 67

14.2.10 Energy Detect Control (EDCR) .............................................................................................. 68

14.2.11 PHY Control Frames Configuration Register (PCFCR) ............................................................. 69

14.3 TEST REGISTERS - PAGE 1 ...................................................................................................... 70

14.3.1 Signal Detect Configuration (SD_CNFG), Page 1 ...................................................................... 70

14.4 LINK DIAGNOSTICS REGISTERS - PAGE 2 ................................................................................ 71

14.4.1 100 Mb Length Detect Register (LEN100_DET), Page 2 ............................................................. 71

14.4.2 100 Mb Frequency Offset Indication Register (FREQ100), Page 2 ............................................... 71

14.4.3 TDR Control Register (TDR_CTRL), Page 2 ............................................................................. 72

14.4.4 TDR Window Register (TDR_WIN), Page 2 .............................................................................. 73

14.4.5 TDR Peak Register (TDR_PEAK), Page 2 ................................................................................ 73

14.4.6 TDR Threshold Register (TDR_THR), Page 2 ........................................................................... 73

14.4.7 Variance Control Register (VAR_CTRL), Page 2 ....................................................................... 74

14.4.8 Variance Data Register (VAR_DATA), Page 2 .......................................................................... 74

14.4.9 Link Quality Monitor Register (LQMR), Page 2 .......................................................................... 75

14.4.10 Link Quality Data Register (LQDR), Page 2 ............................................................................. 77

14.4.11 Link Quality Monitor Register 2 (LQMR2), Page 2 .................................................................... 78

14.5 PTP 1588 BASE REGISTERS - PAGE 4 ...................................................................................... 79

14.5.1 PTP Control Register (PTP_CTL), Page 4 ................................................................................ 79

14.5.2 PTP Time Data Register (PTP_TDR), Page 4 ........................................................................... 81

14.5.3 PTP Status Register (PTP_STS), Page 4 ................................................................................. 81

14.5.4 PTP Trigger Status Register (PTP_TSTS), Page 4 .................................................................... 82

14.5.5 PTP Rate Low Register (PTP_RATEL), Page 4 ......................................................................... 83

14.5.6 PTP Rate High Register (PTP_RATEH), Page 4 ....................................................................... 84

14.5.7 PTP Read Checksum (PTP_RDCKSUM), Page 4 ..................................................................... 84

14.5.8 PTP Write Checksum (PTP_WRCKSUM), Page 4 ..................................................................... 84

14.5.9 PTP Transmit Timestamp Register (PTP_TXTS), Page 4 ........................................................... 85

14.5.10 PTP Receive Timestamp Register (PTP_RXTS), Page 4 .......................................................... 85

14.5.11 PTP Event Status Register (PTP_ESTS), Page 4 .................................................................... 86

14.5.12 PTP Event Data Register (PTP_EDATA), Page 4 .................................................................... 87

14.6 PTP 1588 CONFIGURATION REGISTERS - PAGE 5 .................................................................... 89

14.6.1 PTP Trigger Configuration Register (PTP_TRIG), Page 5 ........................................................... 89

14.6.2 PTP Event Configuration Register (PTP_EVNT), Page 5 ............................................................ 90

14.6.3 PTP Transmit Configuration Register 0 (PTP_TXCFG0), Page 5 ................................................. 91

14.6.4 PTP Transmit Configuration Register 1 (PTP_TXCFG1), Page 5 ................................................. 92

14.6.5 PHY Status Frame Configuration Register 0 (PSF_CFG0), Page 5 .............................................. 92

14.6.6 PTP Receive Configuration Register 0 (PTP_RXCFG0), Page 5, ................................................. 93

14.6.7 PTP Receive Configuration Register 1 (PTP_RXCFG1), Page 5 .................................................. 94

14.6.8 PTP Receive Configuration Register 2 (PTP_RXCFG2), Page 5 .................................................. 94

www.national.com 4

DP83640

14.6.9 PTP Receive Configuration Register 3 (PTP_RXCFG3), Page 5 .................................................. 95

14.6.10 PTP Receive Configuration Register 4 (PTP_RXCFG4), Page 5 ................................................ 96

14.6.11 PTP Temporary Rate Duration Low Register (PTP_TRDL), Page 5 ............................................ 96

14.6.12 PTP Temporary Rate Duration High Register (PTP_TRDH), Page 5 ........................................... 97

14.7 PTP 1588 CONFIGURATION REGISTERS - PAGE 6 .................................................................... 97

14.7.1 PTP Clock Output Control Register (PTP_COC), Page 6 ............................................................ 97

14.7.2 PHY Status Frame Configuration Register 1 (PSF_CFG1), Page 6 .............................................. 98

14.7.3 PHY Status Frame Configuration Register 2 (PSF_CFG2), Page 6 .............................................. 98

14.7.4 PHY Status Frame Configuration Register 3 (PSF_CFG3), Page 6 .............................................. 98

14.7.5 PHY Status Frame Configuration Register 4 (PSF_CFG4), Page 6 .............................................. 98

14.7.6 PTP SFD Configuration Register (PTP_SFDCFG), Page 6 ......................................................... 99

14.7.7 PTP Interrupt Control Register (PTP_INTCTL), Page 6 .............................................................. 99

14.7.8 PTP Clock Source Register (PTP_CLKSRC), Page 6 ................................................................. 99

14.7.9 PTP Ethernet Type Register (PTP_ETR), Page 6 ...................................................................... 99

14.7.10 PTP Offset Register (PTP_OFF), Page 6 .............................................................................. 100

14.7.11 PTP GPIO Monitor Register (PTP_GPIOMON), Page 6 .......................................................... 100

14.7.12 PTP Receive Hash Register (PTP_RXHASH), Page 6 ............................................................ 100

15.0 Absolute Maximum Ratings ......................................................................................................... 101

16.0 AC and DC Specifications ........................................................................................................... 101

16.1 DC SPECIFICATIONS ............................................................................................................. 101

16.2 AC SPECIFICATIONS .............................................................................................................. 102

16.2.1 Power Up Timing ................................................................................................................ 102

16.2.2 Reset Timing ...................................................................................................................... 103

16.2.3 MII Serial Management Timing ............................................................................................. 104

16.2.4 100 Mb/s MII Transmit Timing ............................................................................................... 104

16.2.5 100 Mb/s MII Receive Timing ................................................................................................ 105

16.2.6 100BASE-TX and 100BASE-FX MII Transmit Packet Latency Timing ......................................... 105

16.2.7 100BASE-TX and 100BASE-FX MII Transmit Packet Deassertion Timing ................................... 106

16.2.8 100BASE-TX Transmit Timing (t

R/F

& Jitter) ............................................................................ 106

16.2.9 100BASE-TX and 100BASE-FX MII Receive Packet Latency Timing ......................................... 107

16.2.10 100BASE-TX and 100BASE-FX MII Receive Packet Deassertion Timing ................................. 107

16.2.11 10 Mb/s MII Transmit Timing ............................................................................................... 108

16.2.12 10 Mb/s MII Receive Timing ................................................................................................ 108

16.2.13 10BASE-T MII Transmit Timing (Start of Packet) ................................................................... 109

16.2.14 10BASE-T MII Transmit Timing (End of Packet) .................................................................... 109

16.2.15 10BASE-T MII Receive Timing (Start of Packet) .................................................................... 110

16.2.16 10BASE-T MII Receive Timing (End of Packet) ..................................................................... 110

16.2.17 10 Mb/s Heartbeat Timing .................................................................................................. 111

16.2.18 10 Mb/s Jabber Timing ...................................................................................................... 111

16.2.19 10BASE-T Normal Link Pulse Timing ................................................................................... 112

16.2.20 Auto-Negotiation Fast Link Pulse (FLP) Timing ...................................................................... 112

16.2.21 100BASE-TX Signal Detect Timing ..................................................................................... 113

16.2.22 100 Mb/s Internal Loopback Timing ..................................................................................... 113

16.2.23 10 Mb/s Internal Loopback Timing ...................................................................................... 114

16.2.24 RMII Transmit Timing (Slave Mode) ..................................................................................... 114

16.2.25 RMII Transmit Timing (Master Mode) ................................................................................... 115

16.2.26 RMII Receive Timing (Slave Mode) ...................................................................................... 116

16.2.27 RMII Receive Timing (Master Mode) .................................................................................... 117

16.2.28 RX_CLK Timing (RMII Master Mode) ................................................................................... 118

16.2.29 CLK_OUT Timing (RMII Slave Mode) ................................................................................... 118

16.2.30 Single Clock MII (SCMII) Transmit Timing ............................................................................ 119

16.2.31 Single Clock MII (SCMII) Receive Timing .............................................................................. 120

16.2.32 100 Mb/s X1 to TX_CLK Timing .......................................................................................... 121

17.0 Physical Dimensions .................................................................................................................. 122

5 www.national.com

DP83640

剩余123页未读,继续阅读

mrgod0558

- 粉丝: 2

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论2