基于基于FPGA的的AXI4总线时序设计与实现总线时序设计与实现

针对AXI4总线设备之间的高速数据传输需求,根据AXI4总线协议,设计实现了一种基于FPGA的AXI4总线读写

时序控制方法。以FPGA为核心,采用VHDL语言,完成了满足AXI4总线协议的读猝发方式数据传输和写猝发方

式数据传输时序控制模块的设计。利用FPGA内部嵌入式系统提供的高性能数据传输接口完成AXI4时序控制模块

的功能验证。实际应用表明,依据提出的设计方法实现的读写时序控制模块能够满足AXI4总线协议规定的时序

关系,实现数据的高速正确传输,总线数据传输速率能够达到1.09 GB/s。

0 引言引言

高级微控制器总线结构(Advanced Microcontroller Bus Architecture,AMBA)是一种应用于片上系统的总线结构。AMBA总

线协议是ARM公司制定的用于片上系统IP互联与管理的一种规范,由于它是一个开放标准的协议,所以自从出现之后,其应

用领域就超出了微控制器设备,已经广泛应用于各种ASIC和片上系统器件中。高级可扩展接口4(Advanced eXtensible

Interface 4,AXI4)总线规范是ARM公司与Xilinx公司共同制定的新一代用于片上系统内IP互联的总线规范,是第4版AMBA规

范定义的7个总线接口之一,用以满足普遍情况下的元件接口要求,为互联结构的实现提供了灵活性

[1]

。

本文通过对

1 AXI4总线协议简介总线协议简介

1.1 AXI4总线协议特性与优势总线协议特性与优势

AXI4总线协议规定的数据传输方式是猝发式的,使用首字节选通方式,在独立的读写数据通道采用独立的地址、控制和数

据周期进行数据传输,支持非对齐方式的数据传输,能够发出多个未解析的地址,从而完成无序的数据传输交易。

AXI4总线协议的上述特性,使得其与其他总线协议相比较,具有比较明显的优势。首先,AXI4总线协议简化了不同领域IP

的集成,将不同接口整合到一个接口中,简化了用户熟悉与开发的难度,从而提高了生产效率;其次,AXI4总线协议支持嵌

入式、DSP以及FPGA各种电子设计领域的用户使用,具有很大的灵活性;最后,由于第三方EDA厂商与IP开发厂商普遍接受

并采用了AXI4总线协议标准,从而使得基于AXI4总线协议的目标平台具有广泛的IP可用性

[1-4]

。

1.2 AXI4总线协议信号集与时序关系总线协议信号集与时序关系

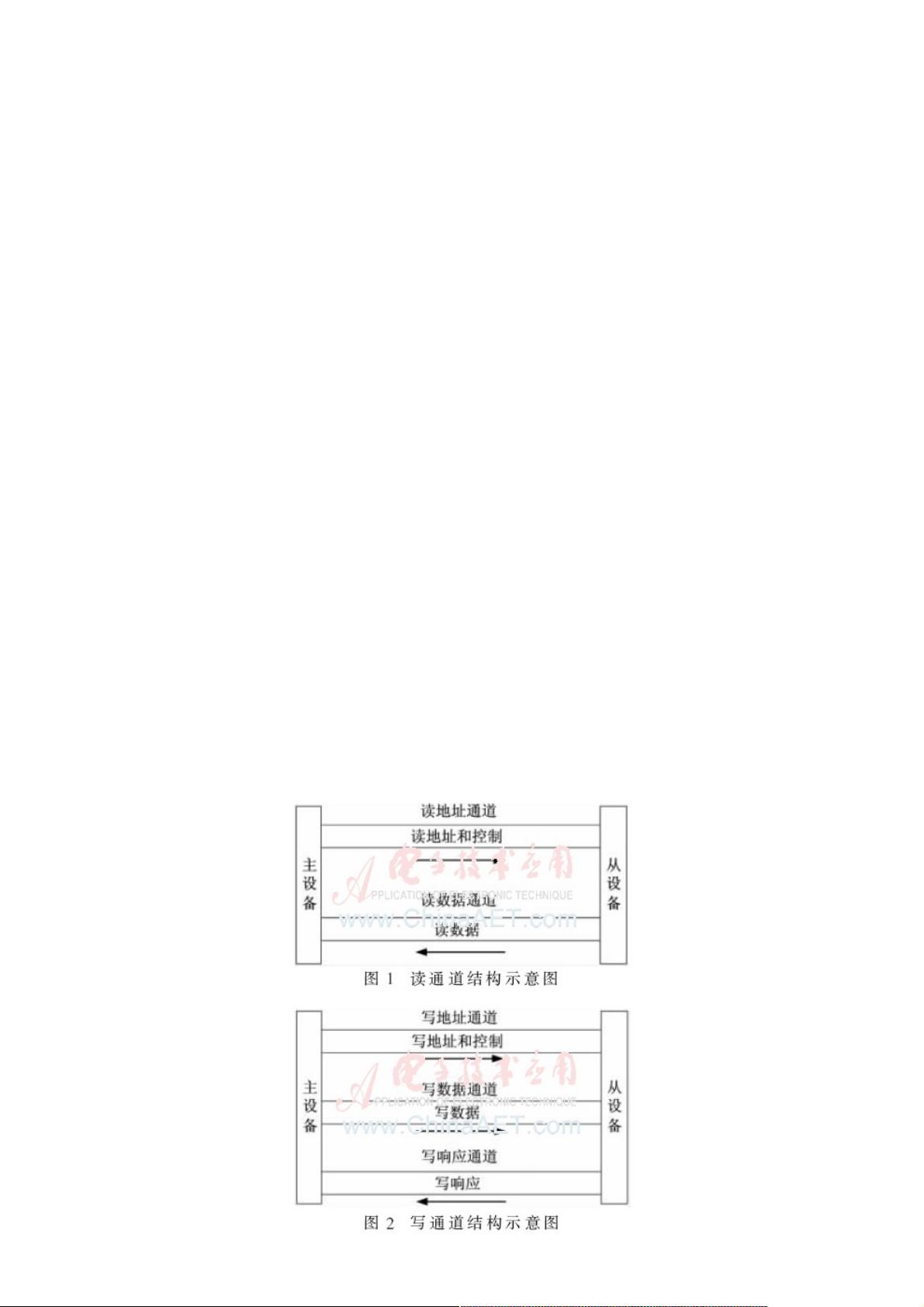

AXI4总线协议规定5个不同的通道,分别是读地址通道(Read Address Channel,AR)、写地址通道(Write Address

Channel,AW)、读数据通道(Read Data Channel,R)、写数据通道(Write Data Channel,W)和写响应通道(Write Response

Channel,B)

[5-6]

。其中,读、写地址通道传输数据交互过程中需要的地址和控制信号;读数据通道传输从从设备到主设备的

读数据以及相应读信息;写数据通道传输从主设备到从设备的写数据;写响应通道用于标识从设备响应主设备的写操作。主设

备与从设备之间的数据传输分别用到从主设备到从设备的写数据通道和从从设备到主设备的读数据通道,从主设备到从设备的

写数据交易过程中,从设备会通过响应通道向主设备反馈写操作是否完成。读地址通道与写地址通道都是从主设备到从设备。

其读通道结构如图1所示,写通道结构如图2所示。

评论5