没有合适的资源?快使用搜索试试~ 我知道了~

首页约束管理器-allegro高手进阶.pdf

约束管理器-allegro高手进阶.pdf

需积分: 50 39 下载量 174 浏览量

更新于2023-03-03

评论 2

收藏 1.59MB PDF 举报

约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB 设计流程中 用于管理所有工具的高速电子约束。约束管理器让你定义、查看和校验从原理图到分析到 PCB 设计实现的设计流程中每一步的约束。可以使用约束管理器和 SigXplorer Expert 开发电 路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。 本培训教材描述的主要是怎样在约束管理器中提取约束,并且约束如何与原理图和 PCB 的属性同步。本教材的内容是约束管理器、Concept HDL 和 PCB Design 的紧密集成的 集锦。 所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子 约束(ECSets)就是限制 PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延 迟为 2ns。

资源详情

资源评论

资源推荐

目录

第一章 约束管理器介绍............................................................................4

1.1 约束管理器简介.................................................................................................................4

1.2 约束管理器界面简介.........................................................................................................8

1.2.1 worksheet selector.......................................................................................................8

1.2.2

用户接口

.....................................................................................................................9

1.2.3 View

选项

....................................................................................................................9

1.3 启动约束管理器...............................................................................................................11

第 2 章

OBJECTS 介绍 .........................................................................12

P2.1

IN

-P

AIRS

..........................................................................................................................13

2.1.1 Pin-Pair

规则

............................................................................................................14

N2.2

ETS

和 X

NETS

.................................................................................................................14

B2.3

USES

................................................................................................................................15

M2.4

ATC H

G

ROUPS

................................................................................................................15

2.4.1

如何确定

target pin pair ..........................................................................................16

2.4.2

相对

/

匹配的群组规则

..............................................................................................16

2.5 D

IFF

P

AIRS

.........................................................................................................................16

2.5.1

差分对工作表

...........................................................................................................17

2.5.2

差分计算器(

Differential Calculator

)的使用方法

..............................................19

2.5.3

差分对规则

...............................................................................................................19

2.6 D

ESIGNS AND

S

YSTEMS

.....................................................................................................20

第 3 章

设置网络的走线约束.................................................................21

3.1.1

设置网络的最大最小传输延迟

...............................................................................21

3.1.2

设置网络相对传输延迟

...........................................................................................24

3.1.3

设置差分对约束

.......................................................................................................26

3.1.4

查看网络规范格式和物理格式

...............................................................................28

第 4 章 设置网络的时序和信号完整性约束 ........................................30

4.1 设置时序约束...................................................................................................................30

4.2 设置信号完整性约束.......................................................................................................32

4.2.1

设置电气属性约束

...................................................................................................32

0 第一章 约束管理器介绍

2

4.2.2

设置反射属性约束

...................................................................................................33

第 5 章 电子约束创建和应用.................................................................35

5.1 创建 ECSET ......................................................................................................................35

5.2 指定 ECS

ET 给网络 .........................................................................................................40

5.3 不考虑 ECS

ET 的缺省约束值..........................................................................................41

5.4 在原理图中查看 ECS

ET ..................................................................................................41

第 6 章 ECOS 实现.................................................................................43

6.1 在原理图中增加网络.......................................................................................................43

6.2 在原理图中修改约束.......................................................................................................45

6.3 在约束管理器中修改约束...............................................................................................46

6.4 在约束管理器中删除约束...............................................................................................46

6.5 在原理图中重新命名网络...............................................................................................47

第 7 章 在原理图和 PCB 之间同步约束 ..............................................50

7.1 从原理图中输出约束.......................................................................................................50

7.2 在 PCB

DESIGN 中查看和添加约束 ................................................................................50

7.3 在原理图中导入并查看约束...........................................................................................51

7.4 在 PCB 和原理图之间同步约束的两种模式 .................................................................52

7.4.1

用原理图中的约束重写

PCB

中的约束

.................................................................53

7.4.2

在原理图中导入

PCB

中变更的约束

.....................................................................56

第 8 章 约束分析.....................................................................................58

8.1 查看工作表单元格和对象...............................................................................................58

8.2 定制约束、定制测量和定制激励...................................................................................59

8.2.1

定制约束

...................................................................................................................59

8.2.1.1 用户定义的属性......................................................................................................59

8.2.1.2 约束的定制测量......................................................................................................59

第 9 章 SCHEDULING NETS ..............................................................61

9.1 SCHEDULING NETS............................................................................................................61

9.2 S

CHEDULING NETS-REVISITED..........................................................................................65

第 10 章 相对传输延迟.............................................................................68

约束管理器简介

3

第 11 章 MATCH DELAY.......................................................................73

第 12 章 解决 DRC 冲突 ..........................................................................74

第 13 章 约束管理器.................................................................................76

13.1 层次设计中的电子约束...............................................................................................76

0 第一章 约束管理器介绍

4

第一章 约束管理器介绍

约束管理器是一个交叉的平台,以工作簿和工作表的形式在 Cadence PCB 设计流程中

用于管理所有工具的高速电子约束。约束管理器让你定义、查看和校验从原理图到分析到

PCB 设计实现的设计流程中每一步的约束。可以使用约束管理器和 SigXplorer Expert 开发电

路的拓扑并得出电子约束,可以包含定制约束、定制测量和定制激励。

本培训教材描述的主要是怎样在约束管理器中提取约束,并且约束如何与原理图和

PCB 的属性同步。本教材的内容是约束管理器、Concept HDL 和 PCB Design 的紧密集成的

集锦。

所谓约束就是用户定义的限制条件,当在板上走线和放置元件时会遵守这些约束。电子

约束(ECSets)就是限制 PCB 上与电行为有关的对象,比如可以设置某个网络最大传输延

迟为 2ns。

教材主要内容如下:

• 第 1 章~第 7 章主要关于原理图约束管理器使用:

• 在约束管理器中提取 ECs(电子约束);

• 在原理图和约束管理器中执行 ECO;

• 在 Concept 和 PCB Design 中传递 ECs。

这部分面向 Concept HDL 的约束管理器的初学者,但是要熟悉 Concept HDL

和 PCB Design。此教材不讨论 Concept HDL 和 PCB Design 不同模式和属性的

细节,但是会详细地讨论约束管理器过程。

为了快速理解约束管理器的主要特点,可以看看 Concept HDL 的多媒体教

材。请见 Help – Learning Concept HDL– Demos in Concept HDL。

将练习文件 project.zip 解压缩到一个空的路径\design。

确认设置环境变量 CONCEPT_INST_DIR 到 Cadence 安装路径(一般安装时设

置好了)。

•

第 8 章~第 12 章主要关于 PCB 约束管理器使用,但是省略了与原理图相同的

部分。

• 本培训教材附两个练习文件:project.zip 和 golderboard.rar。

1.1 约束管理器简介

约束即用户定义的附加到网络或者管脚对上的要求,电子约束管理着网络和管脚对的行

为。可以使用约束管理器来提取和管理电子约束。Cadence 推荐使用约束管理器来提取约

束,因为约束管理器有下列特性:

• 提供工作表为基础的用户接口,允许快速的提取、修改、删除约束。

• 支持语法检查

• 支持约束继承,高层的约束可以被继承,低层的约束可以覆盖高层约束。

约束管理器简介

5

• 可以定义电子约束集。

• 创建约束报告。

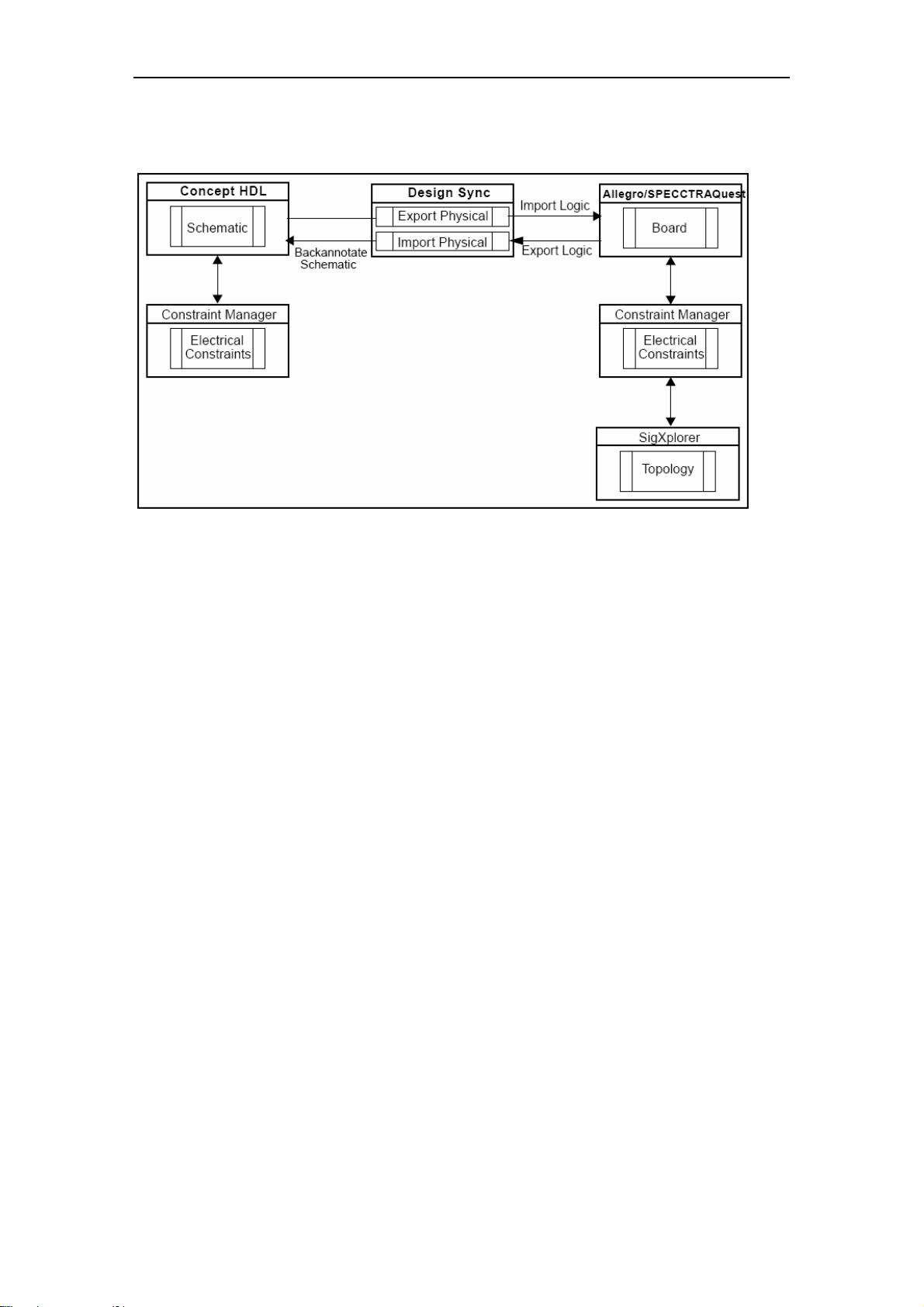

约束管理器在流程中的位置和作用请见下图:

加入约束管理器的设计流程请见下图:

在下图中约束管理器保存电子约束信息在根设计一个新的目录下,约束视图包含*.dcf

文件,里面包含设计的电子约束信息。在此流程中,在打包时 Packager-XL 创建 5 个

pst*.dat 文件,包含传统设计流程中的 3 个文件(pstchip.dat, pstxprt.dat, pstxnet.dat),还有

两个文件 pstcmdb.dat, pstcmbc.dat。pstcmdb.dat 包含当前设计中的电子约束,是 constraints

视图中的*.dcf 文件的拷贝。pstcmbc.dat 包含的是板中的约束,在执行 import physical 时产

生的。如果没有*.dcf 存在,Packager-XL 就允许在传统的流程。

剩余76页未读,继续阅读

lxcxab

- 粉丝: 0

- 资源: 16

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0