没有合适的资源?快使用搜索试试~ 我知道了~

首页综合与Design-Compiler(很好-很经典).pdf

综合与Design-Compiler(很好-很经典).pdf

综合是前端模块设计中的重要步骤之一,综合的过程是将行为描述的电路、RTL级的电路转换到门级的过程;Design Compiler是Synopsys公司用于做电路综合的核心工具,它可以方便地将HDL语言描述的电路转换到基于工艺库的门级网表。本章将初步介绍综合的原理以及使用Design Compiler做电路综合的全过程

资源详情

资源评论

资源推荐

综合与 Design Compiler

综合是前端模块设计中的重要步骤之一,综合的过程是将行为描述的电路、RTL 级的

电路转换到门级的过程;Design Compiler 是 Synopsys 公司用于做电路综合的核心工具,它

可以方便地将 HDL 语言描述的电路转换到基于工艺库的门级网表。本章将初步介绍综合的

原理以及使用 Design Compiler 做电路综合的全过程。

§1. 综合综述

1.1 什么是综合?

综合是使用软件的方法来设计硬件,然后将门级电路实现与优化的工作留给综合工具的

一种设计方法。它是根据一个系统逻辑功能与性能的要求,在一个包含众多结构、功能、性

能均已知的逻辑元件的单元库的支持下,寻找出一个逻辑网络结构的最佳实现方案。即实现

在满足设计电路的功能、速度及面积等限制条件下,将行为级描述转化为指定的技术库中单

元电路的连接。

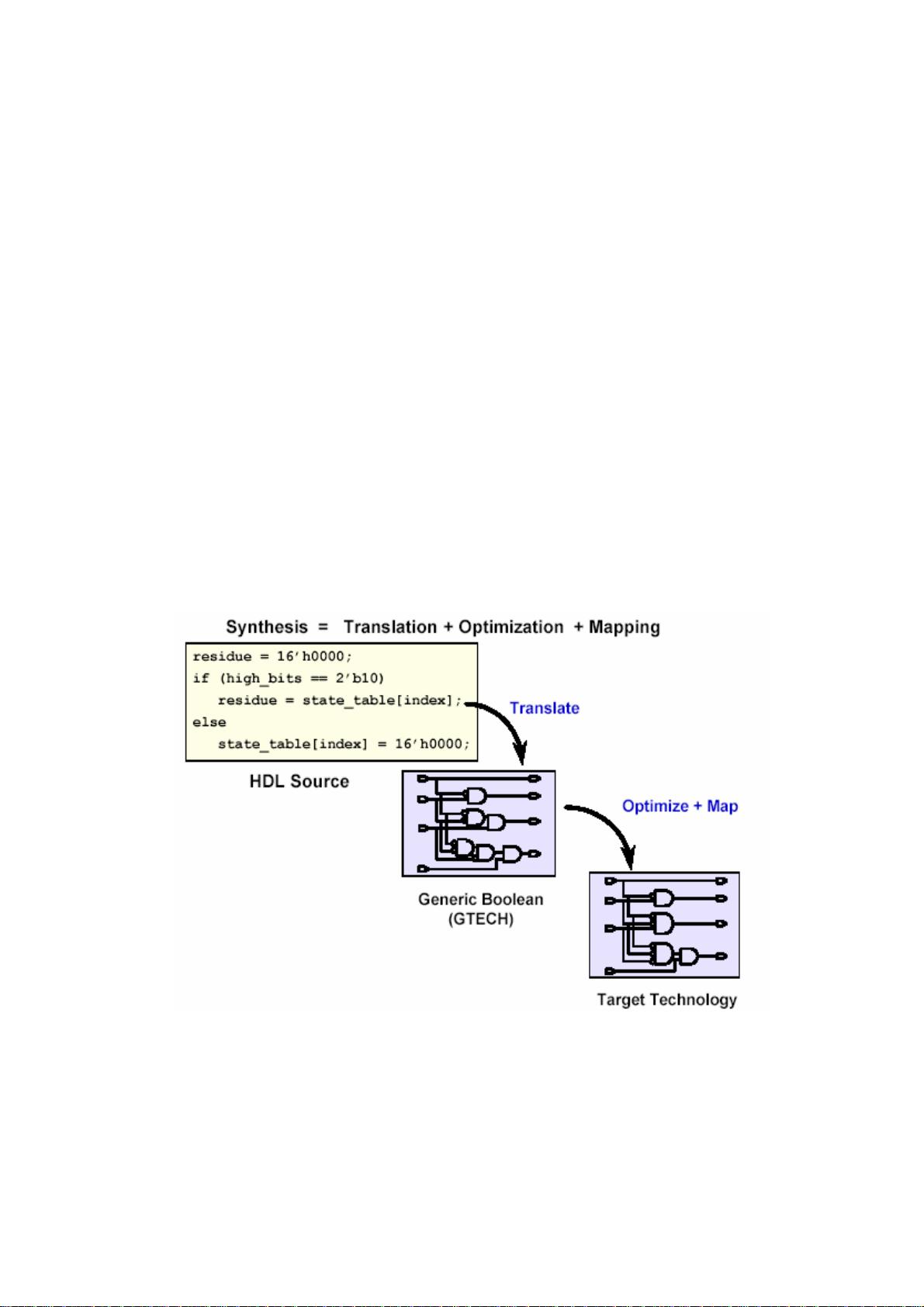

图 1 综合示意图

如图 4-1 所示,综合主要包括三个阶段:转换(translation)、映射(mapping) 与优化

(optimization)。综合工具首先将 HDL 的描述转换成一个与工艺独立(technology-independent)

的 RTL 级网表(网表中 RTL 模块通过连线互联),然后根据具体指定的工艺库,将 RTL 级网

表映射到工艺库上,成为一个门级网表,最后再根据设计者施加的诸如延时、面积方面的约

束条件,对门级网表进行优化。

①

1.2 综合的不同层次

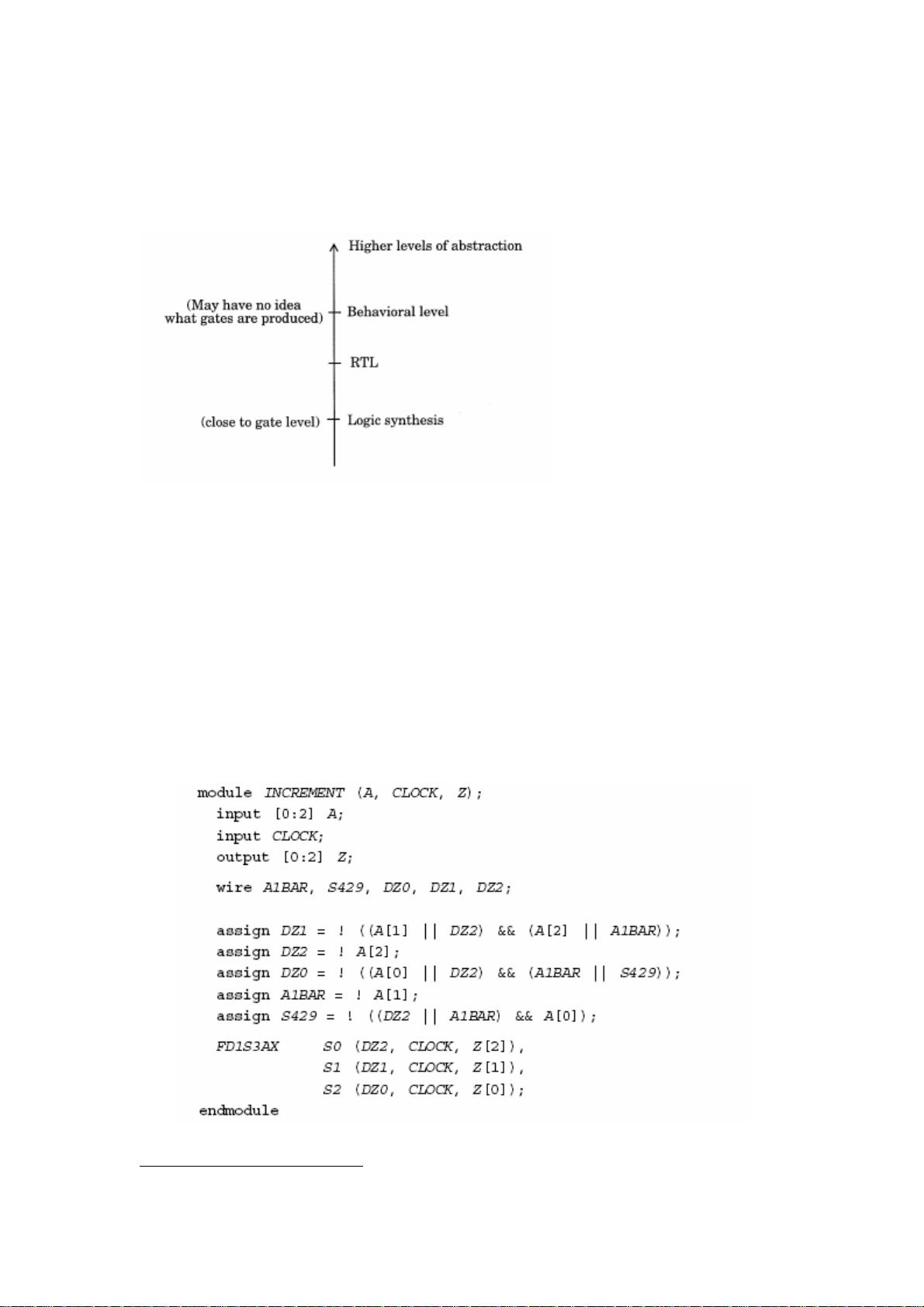

图 2 抽象层次

设计的不同的抽象层次如图 2 所示,随着抽象层次的升高,设计者对于最终硬件(门和

触发器)的控制能力越来越小。设计者可以在上述的三个层次用 HDL 语言描述他的设计,

根据 HDL 语言描述的层次的高低,综合也相应的可以分为逻辑级综合,RTL 级综合以及行

为级综合。

1.2.1 逻辑级综合

在逻辑级综合中,设计被描述成布尔等式的形式,触发器、锁存器这样的基本单元采用

元件例化(instantiate)的方式表达出来。下面是一个加法器的逻辑级描述,输出寄存——

①

有关逻辑综合优化的不同阶段,请参考«VLSI handbook» 的第 33 章

它综合以后的电路网表如下图 3 所示,对比一下不难看出,逻辑级描述实际上已经暗示

了综合以后的网表。

图 3 综合后的网表

1.2.2 RTL 级综合

与逻辑级综合不同,在 RTL 级综合中,电路的数学运算和行为功能分别通过 HDL 语言

特定的运算符和行为结构描述出来。对于时序电路,我们可以明确的描述它在每个时钟边沿

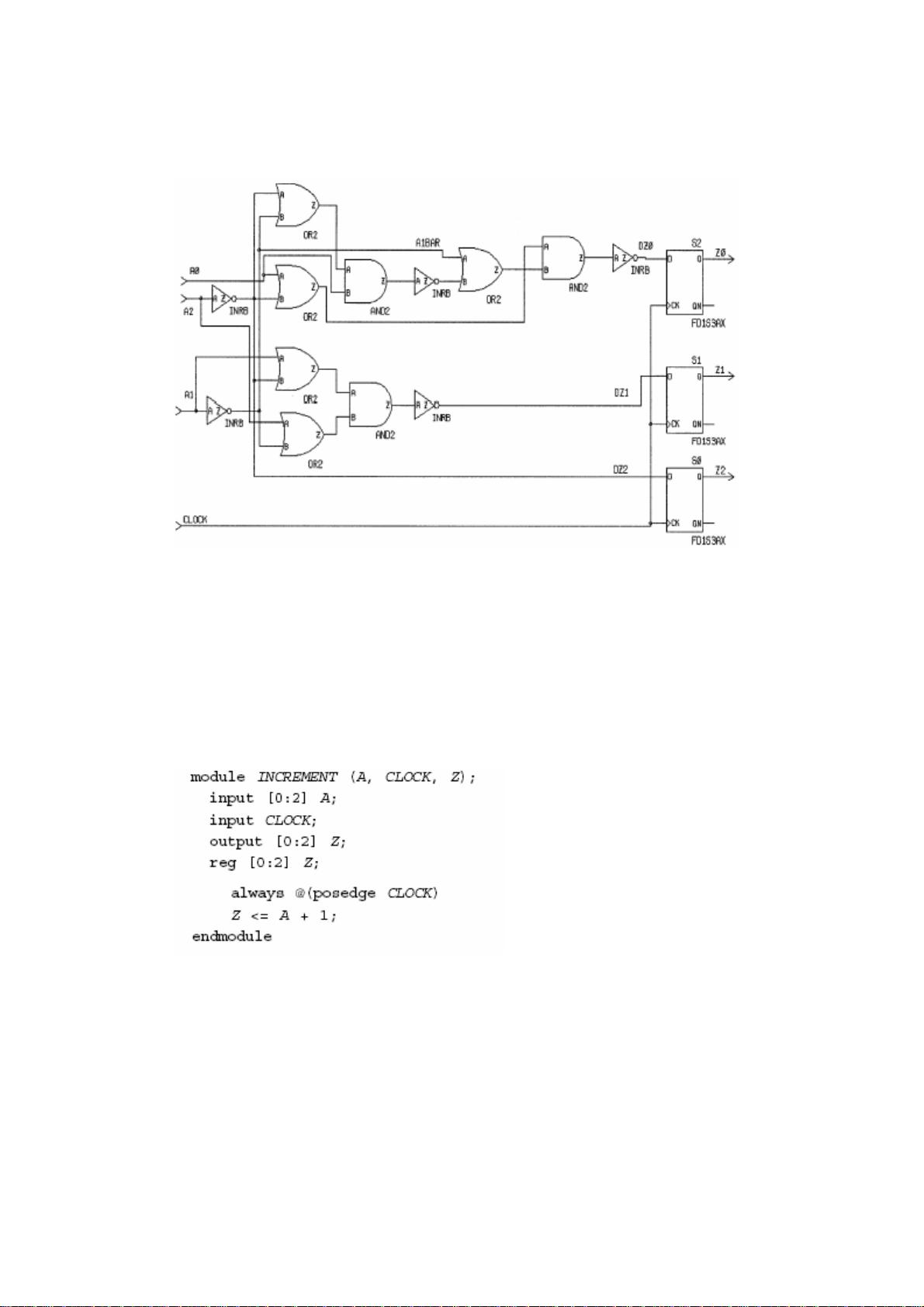

的行为。下面同样是一个加法器的描述,它综合以后的网表如图 3 所示——

注意到,图 3 中的三个触发器不是例化而是通过 HDL 的特定结构推断出来的。这种推

断是根据一些推断法则(Inference rule)进行的,例如在这个例子中,当一个信号(变量)在

时钟的边沿进行赋值(always 语句),那么这个信号(变量)可以推断为一个触发器。

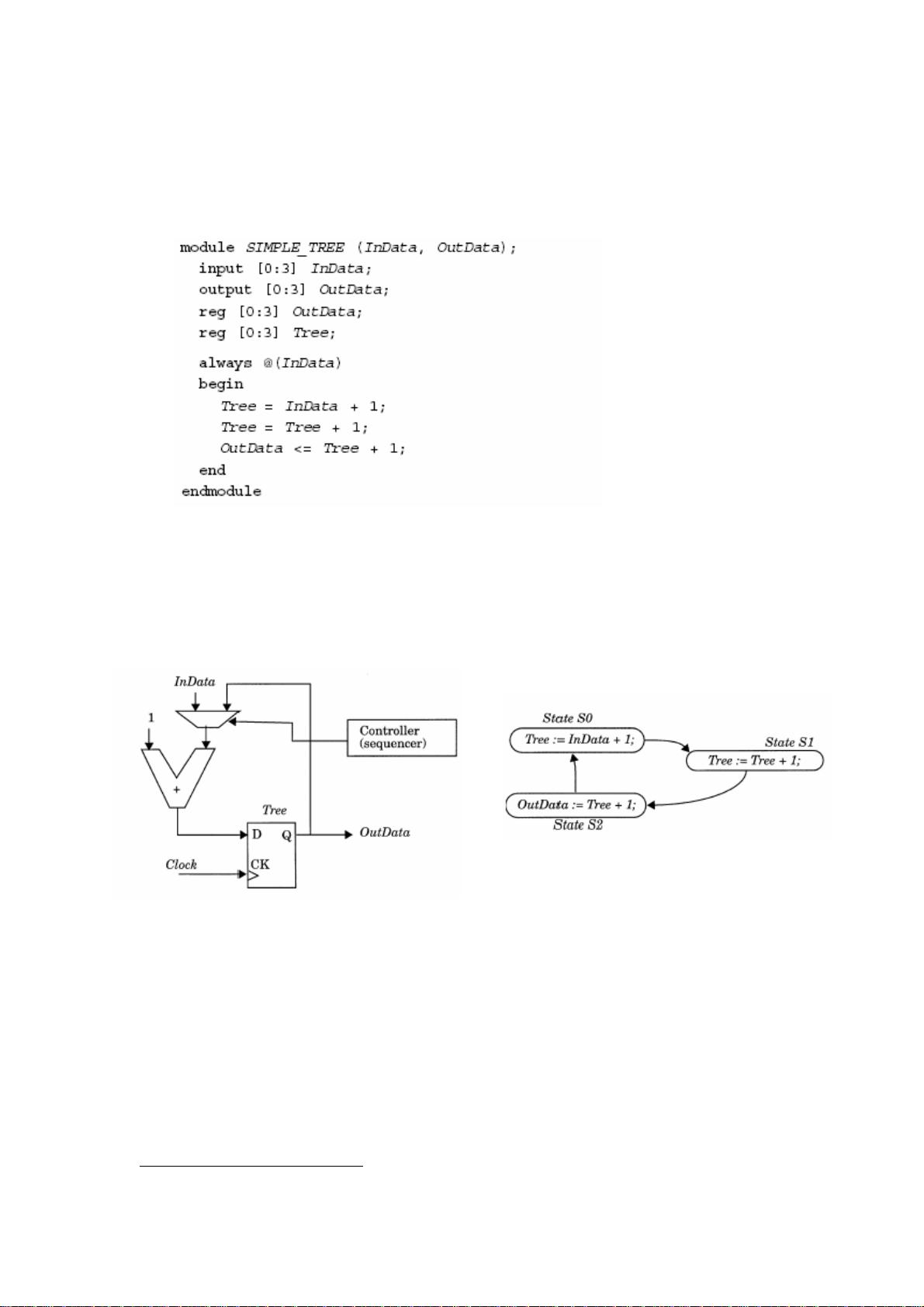

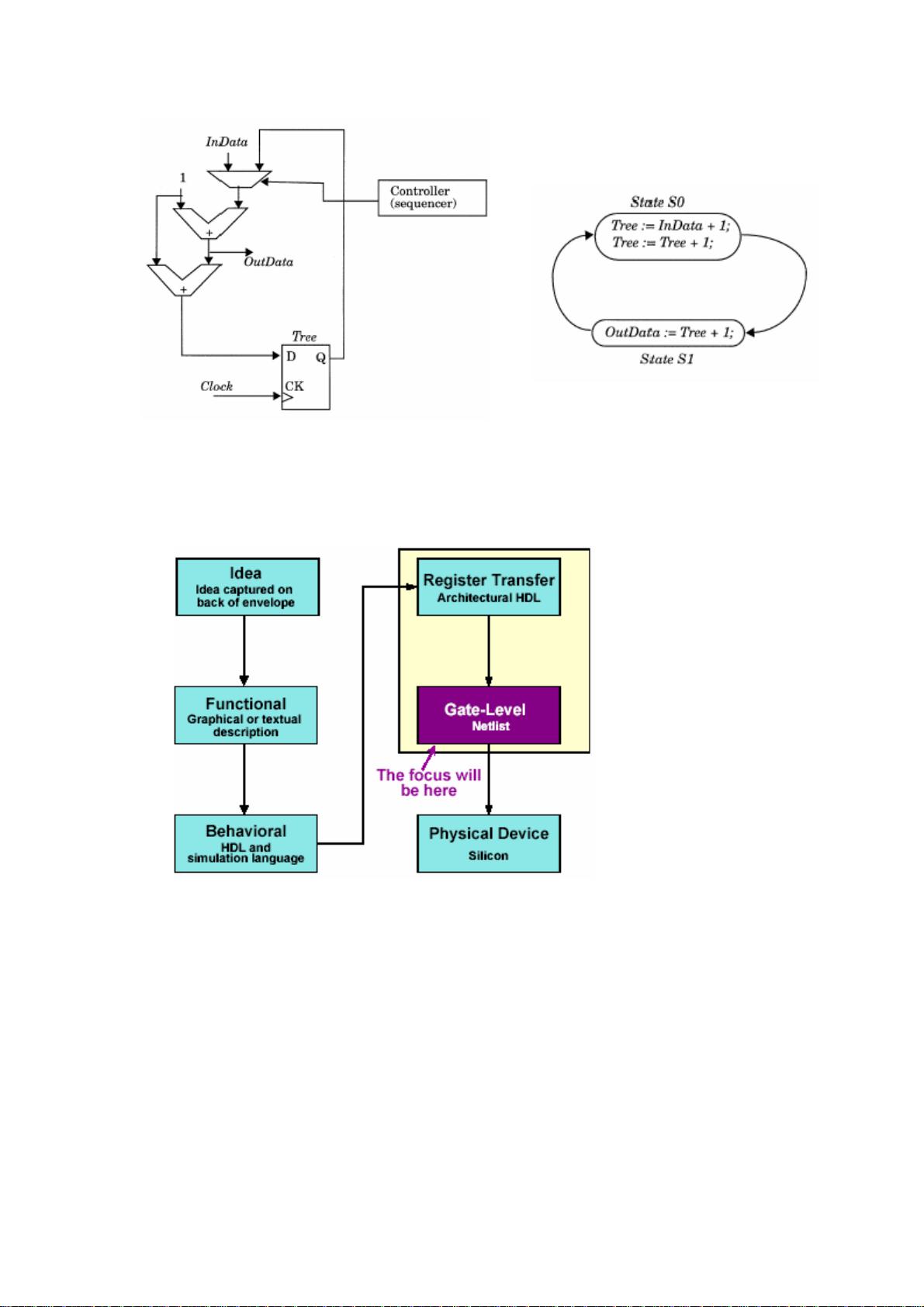

1.2.3 行为级综合

行为级综合比 RTL 级综合层次更高,同时它描述电路也越抽象,在 RTL 级中,电路在

每个时钟边沿的行为必须确切的描述出来,而行为级描述却不是这样,这里没有明确规定电

路的时钟周期,推断法则也不是用来推断寄存器。电路的行为可以描述成一个时序程序

(sequential program),综合工具的任务就是根据指定的设计约束,找出哪些运算可以在哪个

时钟周期内完成,需要在多个周期内用到的变量值需要通过寄存器寄存起来。

请看一个简单的行为综合的例子——

上面这个例子没有任何时钟的信息,现在假设一次加法操作(加法器)需要 5ns 的延时并

且假设系统的时钟是 6ns,那么可以看出执行完上述操作需要 3 个周期的时间。另外,所有

的三个加法语句可以通过重用一个加法器来实现,而且只需要一个叫做 Tree 的寄存器保存

中间变量的值(不同时钟周期的变量值)。这种假设下的电路结构图如图 4 所示,控制器的时

序关系如图 5 所示。

图 4 6ns 周期下的电路结构 图 5 控制时序图

如果改变约束条件,假设时钟周期是 11ns,那么完成全部操作仅需 2 个周期,同时需

要 2 个加法器,图 6 和图 7 分别是此时的电路结构图和控制器时序图。

①

①

有关行为综合和 RTL 综合的具体描述请参考«VLSI handbook» 的第 75 章

图 6 11ns 周期下的电路结构 图 7 控制时序

1.2.4 Design Compiler 所处的位置

图 8 Design Compiler 所处位置

图 8 向我们展示了一个设计从最初的最抽象的概念阶段到最终的芯片阶段的转化过程,

在这个过程当中,Design Compiler 主要完成将设计的 RTL 级描述转化到门级网表的过程,

比 RTL 更高的行为级的综合,将由 Synopsys 的另外一个工具——Behavior Compiler 来完成。

在以下的章节中,我们主要围绕怎样将一个 RTL 级描述的设计转化为门级网表来进行讨论。

剩余114页未读,继续阅读

tangfeng188

- 粉丝: 0

- 资源: 2

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 27页智慧街道信息化建设综合解决方案.pptx

- 计算机二级Ms-Office选择题汇总.doc

- 单链表的插入和删除实验报告 (2).docx

- 单链表的插入和删除实验报告.pdf

- 物联网智能终端项目设备管理方案.pdf

- 如何打造品牌的模式.doc

- 样式控制与页面布局.pdf

- 武汉理工Java实验报告(二).docx

- 2021线上新品消费趋势报告.pdf

- 第3章 Matlab中的矩阵及其运算.docx

- 基于Web的人力资源管理系统的必要性和可行性.doc

- 基于一阶倒立摆的matlab仿真实验.doc

- 速运公司物流管理模式研究教材

- 大数据与管理.pptx

- 单片机课程设计之步进电机.doc

- 大数据与数据挖掘.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论5