没有合适的资源?快使用搜索试试~ 我知道了~

首页富士通单片机(MB90F549G)

资源详情

资源评论

资源推荐

DS07-13703-2E

FUJITSU SEMICONDUCTOR

DATA SHEET

16-bit Proprietary Microcontroller

CMOS

F

2

MC-16LX MB90540/545 Series

MB90F543/F549/V540

■

■■

■

DESCRIPTION

The MB90540/545 series with FULL-CAN*

1

and FLASH ROM is specially designed for automotive and industrial ap-

plications. Its main features are two on board CAN Interfaces (one for MB90V545 series), which conform to V2.0

Part A and Part B, supporting very flexible message buffer

scheme and so offering more functions than a normal

full CAN approach. The instruction set by F

2

MC-16LX CPU core inherits an AT architecture of the F

2

MC*

2

family with

additional instruction sets for high-level languages, extended addressing mode, enhanced multiplication/division in-

structions, and enhanced bit manipulation instructions.The micro controller has a 32-bit accumulator for processing

long word data.The MB90540/545 series has peripheral resources of 8/10-bit A/D converters, UART(SCI), extended

I/O serial interfaces, 8/16-bit timer, I/O timer (input capture(ICU), output compare (OCU)).

*1:Controller Area Network (CAN) - License of Robert Bosch GmbH.

*2:F

2

MC stands for FUJITSU Flexible Microcontroller.

■

■■

■

FEATURES

•Clock

Embedded PLL clock multiplication circuit

Operating clock (PLL clock) can be selected from: divided-by-2 of oscillation or one to four times the oscillation

Minimum instruction execution time: 62.5 ns (operation at oscillation of 4 MHz, four times the oscillation clock,

V

CC of 5.0V)

Subsystem Clock: 32 kHz

(Continued)

■

■■

■

PACKAGE

100-pin Plastic QFP

(FPT-100P-M06)

查询MB90F546G供应商

MB90540/545 Series

2

(Continued)

• Instruction set to optimize controller applications

Rich data types (bit, byte, word, long word)

Rich addressing mode (23 types)

Enhanced signed multiplication/division instruction and RETI instruction functions

Enhanced precision calculation realized by the 32-bit accumulator

• Instruction set designed for high level language (C language) and multi-task operations

Adoption of system stack pointer

Enhanced pointer indirect instructions

Barrel shift instructions

• Program patch function (for two address pointers)

• Enhanced execution speed: 4-byte Instruction queue

• Enhanced interrupt function: 8 levels, 34 factors

• Automatic data transmission function independent of CPU operation

Extended intelligent I/O service function (EI

2

OS)

• Embedded ROM size and types

Flash ROM: 128 Kbytes / 256 Kbytes

Embedded RAM size: 6 Kbytes / 8 Kbytes (evaluation chip)

•Flash ROM

Supports automatic programming, Embedded Algorithm TM*

Write / Erase / Erase-Suspend / Resume commands

A flag indicating completion of the algorithm

Hard-wired reset vector available in order to point to a fixed boot sector in Flash Memory

Erase can be performed on each block

Block protection with external programming voltage

• Low-power consumption (stand-by) mode

Sleep mode (mode in which CPU operating clock is stopped)

Stop mode (mode in which oscillation is stopped)

CPU intermittent operation mode

Clock mode

Hardware stand-by mode

•Process

0.5 µm CMOS technology

• I/O port

General-purpose I/O ports: 81 ports

•Timer

Watchdog timer: 1 channel

8/16-bit PPG timer: 8/16-bit × 4 channels

16-bit re-load timer: 2 channels

• 16-bit I/O timer

16-bit free-run timer: 1 channel

Input capture: 8 channels

Output compare: 4 channels

• Extended I/O serial interface: 1 channel

•UART 0

With full-duplex double buffer (8-bit length)

Clock asynchronized or clock synchronized (with start/stop bit) transmission can be selectively used.

(Continued)

MB90540/545 Series

3

(Continued)

•UART 1

With full-duplex double buffer (8-bit length)

Clock asynchronized or clock synchronized serial (extended I/O serial) can be used.

• External interrupt circuit (8 channels)

A module for starting an extended intelligent I/O service (EI

2

OS) and generating an external interrupt which

is triggered by an external input.

• Delayed interrupt generation module

Generates an interrupt request for switching tasks.

• 8/10-bit A/D converter (8 channels)

8/10-bit resolution can be selectively used.

Starting by an external trigger input.

Conversion time: 26.3 µs

• FULL-CAN interfaces

MB90540 series: 2 channel

MB90545 series: 1 channel

Conforming to Version 2.0 Part A and Part B

Flexible message buffering (mailbox and FIFO buffering can be mixed)

• External bus interface: Maximum address space 16 Mbytes

*: Embedded Algorithm is a trade mark of Advanced Micro Devices Inc.

MB90540/545 Series

4

■

■■

■

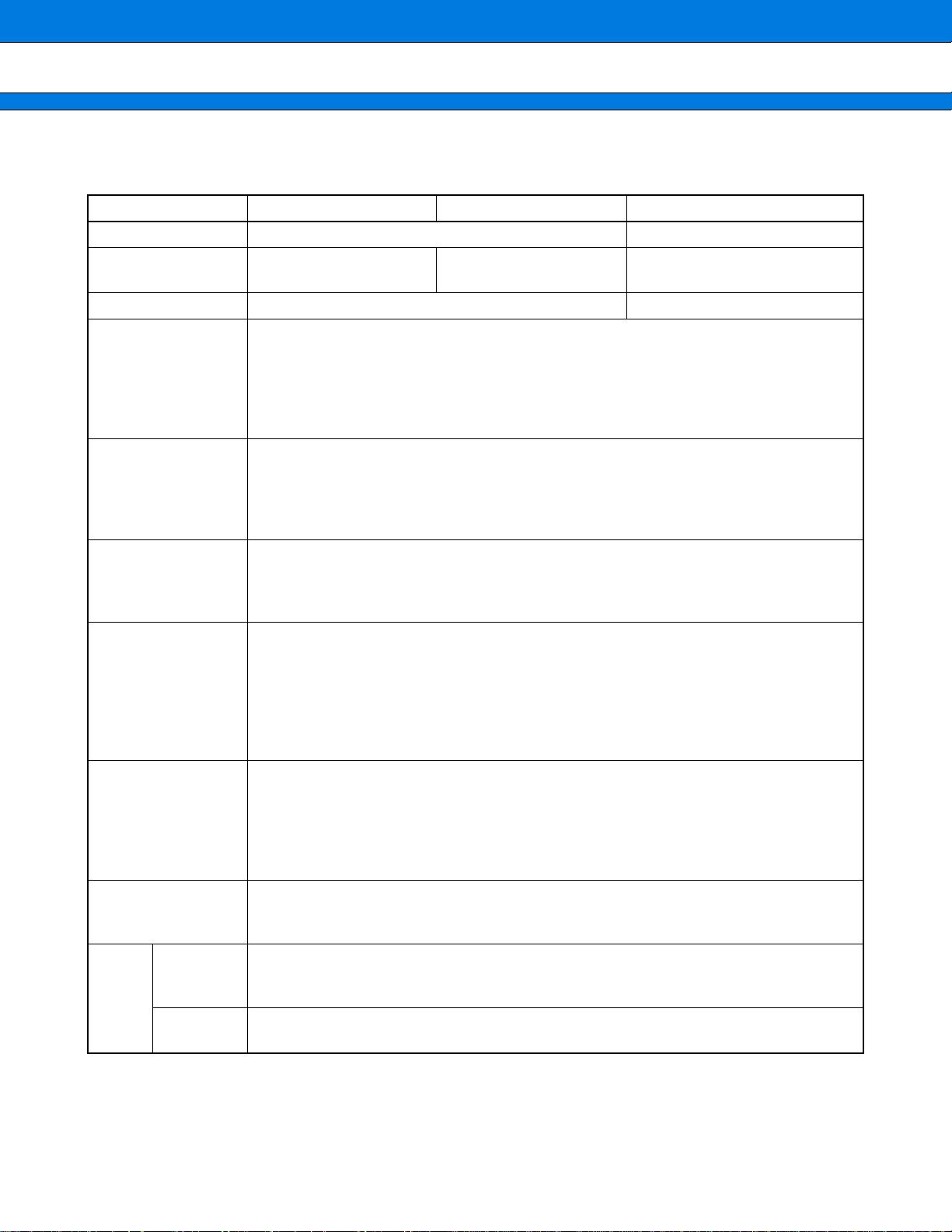

PRODUCT LINEUP

The following table provides a quick outlook of the MB90540/545 Series

(Continued)

Features MB90F543 MB90F549 MB90V540

Classification Flash ROM product Evaluation product

ROM size

128 Kbytes

Boot Block

256 Kbytes

Boot Block

None

ROM size 6 K 8 K

CPU functions

The number of instructions: 351

Instruction bit length: 8 bits, 16 bits

Instruction length: 1 byte to 7 bytes

Data bit length: 1bit, 8 bits, 16 bits

Minimum execution time: 62.5 ns (at machine clock frequency of 16 MHz)

Interrupt processing time: 1.5 µs (at machine clock frequency of 16 MHz, minimum value)

UART 0

Clock synchronized transmission (500 K / 1M / 2 Mbps)

Clock asynchronized transmission (4808 / 5208 / 9615 / 10417 / 19230 / 38460 / 62500

/500000 bps at machine clock frequency of 16 MHz)

Transmission can be performed by bi-directional serial transmission or by master/slave

connection.

UART 1 (SCI)

Clock synchronized transmission (62.5 K/ 12 K/ 250 K/ 500 K/ 1 Mbps)

Clock asynchronized transmission (1202/ 2404/ 4808/ 9615/ 31250 bps)

Transmission can be performed by bi-directional serial

Transmission or by master / slave connection.

8/10-bit A/D converter

Conversion precision: 8/10-bit can be selectively used.

Number of inputs: 8

One-shot conversion mode (converts selected channel once only)

Scan conversion mode (converts two or mode successive channels and can program up

to 8 channels)

Continuous conversion mode (converts selected channel continuously)

Stop conversion mode (converts selected channel and stop operation repeatedly)

8/16-bit PPG timers

Number of channels: 8/16 bit × 4 channels

PPG operation of 8-bit or 16 bit

A pulse wave of given intervals and given duty ratios can be output.

Pulse interval: fsys, fsys/2

1

, fsys/2

2

, fsys/2

3

, fsys/2

4

, 128 µs

(at oscillation of 4 MHz, fsys = machine clock frequency of 16 MHz, fosc = oscillation clock

frequency)

16-bit Reload timer

Number of channels:2

Operation clock frequency: fsys/2

1

, fsys/2

3

, fsys/2

5

(fsys = System clock frequency)

Supports External Event Count function

16-bit

I/O

timer

16-bit

Output com-

pares

Number of channels: 4

Pin input factor: A match signal of compare register

Input cap-

tures

Number of channels: 8

Rewriting a register value upon a pin input (rising, falling, or both edges)

MB90540/545 Series

5

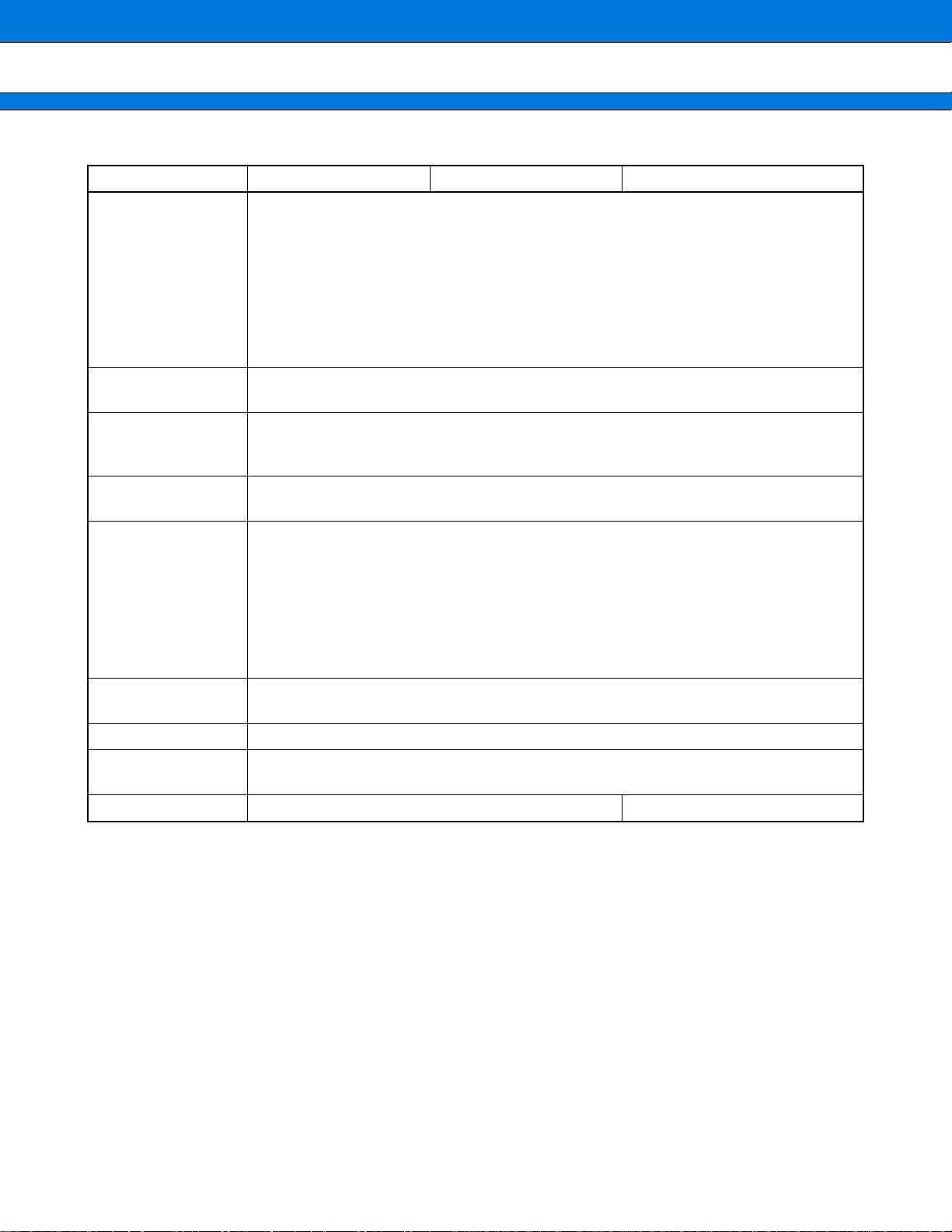

(Continued)

*: Varies with conditions such as operating frequency. (See section “ ■ Electrical Characteristics”.)

Features MB90F543 MB90F549 MB90V540

CAN Interface

Number of channels: 2(MB90540 series), 1(MB90545 series)

Conforms to CAN Specification Version 2.0 Part A and B

Automatic re-transmission in case of error

Automatic transmission responding to Remote Frame

Prioritized 16 message buffers for data and ID’s

Supports multiple messages

Flexible configuration of acceptance filtering:

Full bit compare / Full bit mask / Two partial bit masks

Supports up to 1 Mbps

External interrupt cir-

cuit

Number of inputs: 8

Started by a rising edge, a falling edge, an “H” level input, or an “L” level input.

Extended I/O serial

interface

Clock synchronized transmission (31.25 K / 62.5 K /125 K / 500 K / 1 Mbps at machine

clock frequency of 16 MHz)

LSB first / MSB first

Watchdog timer

Reset generation interval: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms

(at oscillation of 4 MHz, minimum value)

Flash Memory

Supports automatic programming, Embedded Algorithm

TM

and

Write/Erase/Erase-Suspend/Resume commands

A flag indicating completion of the algorithm

Hard-wired reset vector available in order to point to a fixed boot sector in Flash Memory

Boot block configuration

Erase can be performed on each block

Block protection with external programming voltage

Flash Writer from Minato Electronics Inc.

Low-power consump-

tion (stand-by) mode

Sleep/ stop/ CPU intermittent operation/ clock timer/ hardware stand-by

Process CMOS

Power supply voltage

for operation

5 V ± 10 %

Package QFP-100 PGA-256

剩余55页未读,继续阅读

yuefeifei10010

- 粉丝: 0

- 资源: 1

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 数据结构1800题含完整答案详解.doc

- 医疗企业薪酬系统设计与管理方案.pptx

- 界面与表面技术界面理论与表面技术要点PPT学习教案.pptx

- Java集合排序及java集合类详解(Collection、List、Map、Set)讲解.pdf

- 网页浏览器的开发 (2).pdf

- 路由器原理与设计讲稿6-交换网络.pptx

- 火电厂锅炉过热汽温控制系统设计.doc

- 企业识别CIS系统手册[收集].pdf

- 物业管理基础知识.pptx

- 第4章财务预测.pptx

- 《集成电路工艺设计及器件特性分析》——实验教学计算机仿真系.pptx

- 局域网内共享文件提示没有访问权限的问题借鉴.pdf

- 第5章网络营销策略.pptx

- 固井质量测井原理PPT教案.pptx

- 毕业实习总结6篇.doc

- UGNX建模基础篇草图模块PPT学习教案.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0