基于基于FPGA的的LVDS高速数据通信卡高速数据通信卡

介绍了基于FPGA和PCI9054的LVDS数据通信卡的设计,通过FPGA实现了LVDS数据的接收发送控制、

PCI9054实现了与上位机的数据交互,实现了10~200 Mbit·s-1速率的LVDS数据接收以及10~50 Mbit·s-1任意

速率的LVDS数据发送。此板卡的设计,可以有效地应用于某遥测模拟信号源,并对待测设备的LVDS总线协议

进行全面测试。

某遥测信号模拟源是用于产生模拟信号处理器、遥测组件测试和交付测试的前端输入信号的专用设备。该信号源生成各种

类型的信号,输入给待测产品,测试时比对遥测信号模拟源生成的信号和其经过待测产品以后的信号,以判断产品的功能是否

正常。设计中的板卡为该遥测信号模拟源的组成部分,主要用于测试产品的LVDS总线协议的功能是否正常。由于待测信号的

特殊应用,要求板卡能够接收200 Mbit·s-1内的高速串行数据并能发送10~50 Mbit·s-1的任意速率LVDs数据。因PCI总线速度

高、兼容性好、可靠性高且成本低,使其在各种与主机通信的总线技术中优势明显。

1 硬件设计

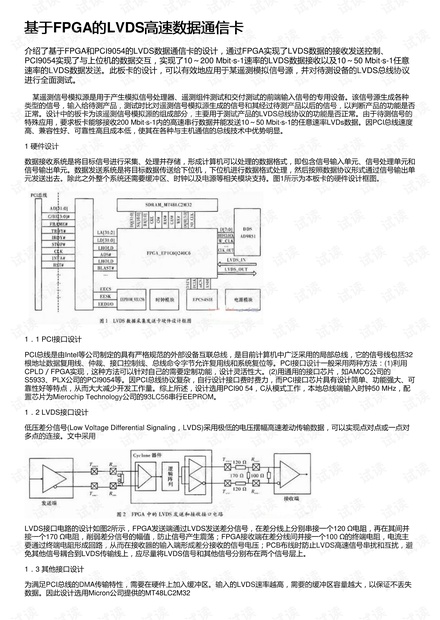

数据接收系统是将目标信号进行采集、处理并存储,形成计算机可以处理的数据格式,即包含信号输入单元、信号处理单元和

信号输出单元。数据发送系统是将目标数据传送给下位机,下位机进行数据格式处理,然后按照数据协议形式通过信号输出单

元发送出去。除此之外整个系统还需要缓冲区、时钟以及电源等相关模块支持。图1所示为本板卡的硬件设计框图。

1.1 PCI接口设计

PCI总线是由Intel等公司制定的具有严格规范的外部设备互联总线,是目前计算机中广泛采用的局部总线,它的信号线包括32

根地址数据复用线、仲裁、接口控制线、总线命令字节允许复用线和系统复位等。PCI接口设计一般采用两种方法:(1)利用

CPLD/FPGA实现,这种方法可以针对自己的需要定制功能,设计灵活性大。(2)用通用的接口芯片,如AMCC公司的

S5933、PLX公司的PCI9054等。因PCI总线协议复杂,自行设计接口费时费力,而PCI接口芯片具有设计简单、功能强大、可

靠性好等特点,从而大大减少开发工作量。综上所述,设计选用PCI90 54,C从模式工作,本地总线端输入时钟50 MHz,配

置芯片为Mierochip Technology公司的93LC56串行EEPROM。

1.2 LVDS接口设计

低压差分信号(Low Voltage Differential Signaling,LVDS)采用极低的电压摆幅高速差动传输数据,可以实现点对点或一点对

多点的连接。文中采用

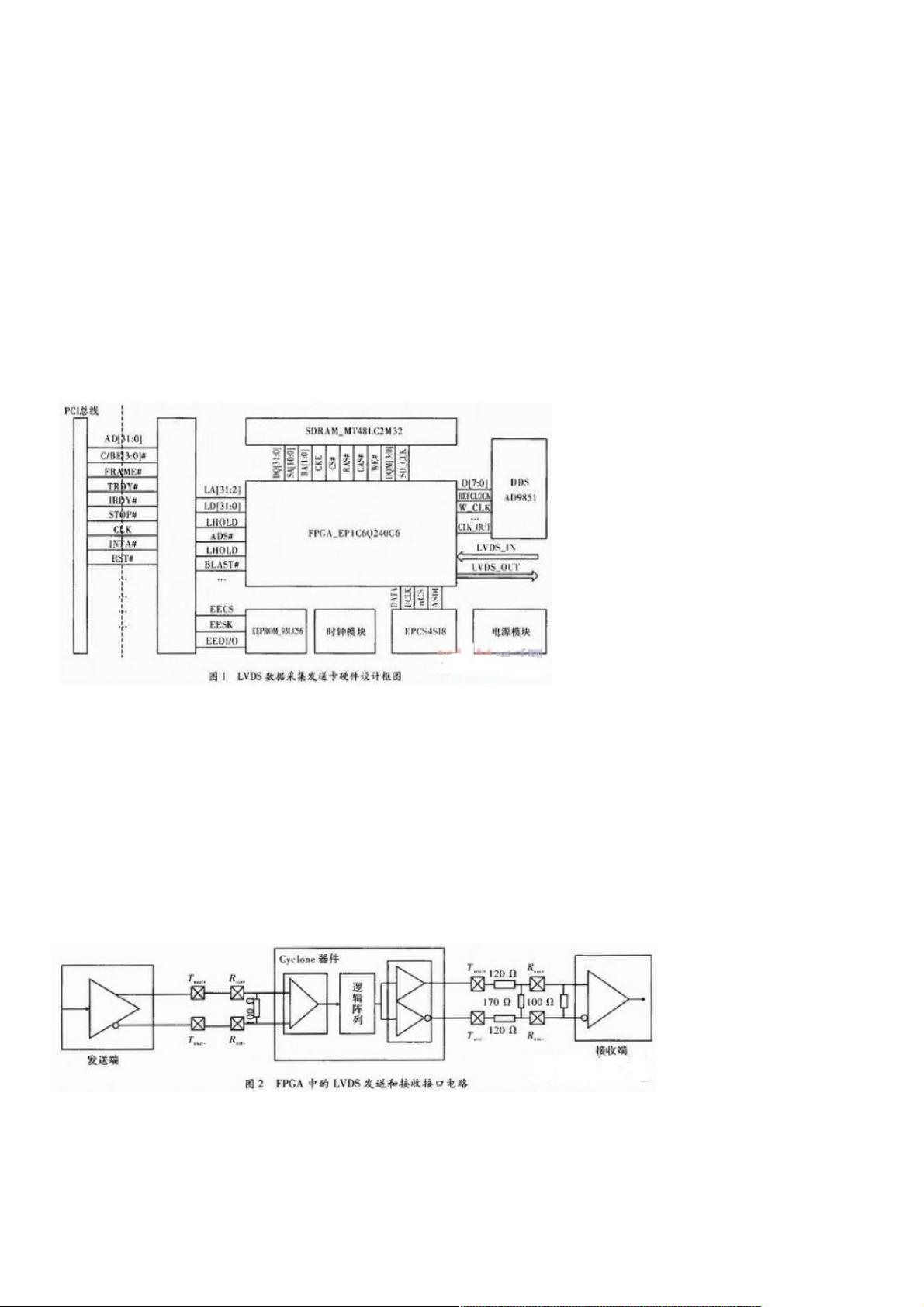

LVDS接口电路的设计如图2所示,FPGA发送端通过LVDS发送差分信号,在差分线上分别串接一个120 Ω电阻,再在其间并

接一个170 Ω电阻,削弱差分信号的幅值,防止信号产生震荡;FPGA接收端在差分线间并接一个100 Ω的终端电阻,电流主

要通过终端电阻形成回路,从而在接收器的输入端形成差分接收的信号电压;PCB布线时防止LVDS高速信号串扰和互扰,避

免其他信号耦合到LVDS传输线上,应尽量将LVDS信号和其他信号分别布在两个信号层上。

1.3 其他接口设计

为满足PCI总线的DMA传输特性,需要在硬件上加入缓冲区。输入的LVDS速率越高,需要的缓冲区容量越大,以保证不丢失

数据。因此设计选用Micron公司提供的MT48LC2M32

评论5