没有合适的资源?快使用搜索试试~ 我知道了~

首页AR0135CS Register Reference.pdf

AR0135CS Register Reference.pdf

需积分: 37 29 下载量 165 浏览量

更新于2023-03-03

评论

收藏 93KB PDF 举报

AR0135CS寄存器参考手册 - AR0135CS Register Reference This register reference is provided for engineers who are designing cameras that use the AR0135CS.

资源详情

资源评论

资源推荐

© Semiconductor Components Industries, LLC, 2016

August, 2016 − Rev. 4

1 Publication Order Number:

AND9385/D

AND9385/D

AR0135CS

Register Reference

Introduction

This register reference is provided for engineers who are

designing cameras that use the AR0135CS.

Conventions and Notations

This document follows the conventions and notations

described below.

• Hexadecimal Numbers Have a 0x Prefix

• Binary Numbers Have 0b Prefix

Example: 0b1010 = 0xA

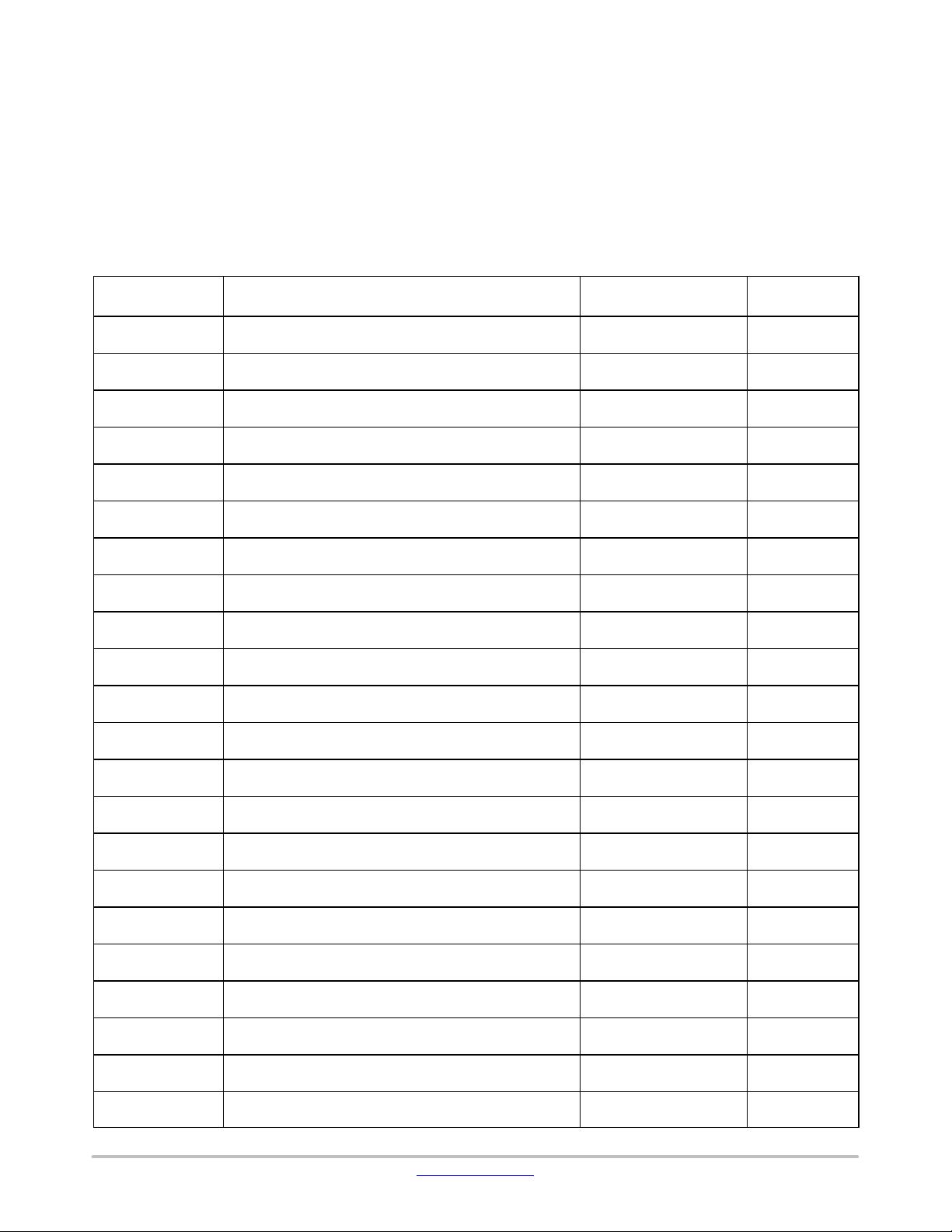

Register Address Space

The AR0135CS provides a 16-bit register address space

accessed through a serial interface. Each register location is

8 or 16 bits in size.

The address space is divided into the five major regions

shown in Table 1.

Table 1. ADDRESS SPACE REGIONS

Address Range

Description

0x0000–0x0FFF Reserved

0x1000–0x1FFF Reserved

0x2000–0x2FFF Reserved

0x3000–0x3FFF Manufacturer-Specific Registers (Read-Only and Read/Write Dynamic Registers)

0x4000–0xFFFF Reserved (Undefined)

Register Notation

The underlying mechanism for reading and writing

registers provides byte write capability. However, it is

convenient to consider some registers as multiple adjacent

bytes. The AR0135CS uses 8-bit, 16-bit, and 32-bit

registers, all implemented as 1 or more bytes at naturally

aligned, contiguous locations in the address space.

In this document, registers are described either by address

or by name. When registers are described by address, the

size of the registers is explicit. For example, R0x3024 is an

8-bit register at address 0x3024, and R0x3000−1 is a 16-bit

register at address 0x3000–0x3001. When registers are

described by name, the size of the register is implicit. It is

necessary to refer to the register table to determine that

model_id is a 16-bit register.

Register Aliases

A consequence of the internal architecture of the

AR0135CS is that some registers are decoded at multiple

addresses. Some registers in “configuration space” are also

decoded in “manufacturer-specific space”. To provide

unique names for all registers, the name of the register

within manufacturer-specific register space has a trailing

underscore. For example, R0x0000–1 is model_id, and

R0x3000–1 is model_id_. The effect of reading or writing

a register through any of its aliases is identical.

Bit Fields

Some registers provide control of several different pieces

of related functionality, and this makes it necessary to refer

to bit fields within registers. As an example of the notation

used for this, the least significant 4 bits of the model_id

register are referred to as model_id[3:0] or R0x0000–1[3:0].

Bit Field Aliases

In addition to the register aliases described above, some

register fields are aliased in multiple places. For example,

R0x0100 (mode_select) only has one operational bit,

R0x0100[0]. This bit is aliased to R0x301A–B[2]. The

effect of reading or writing a bit field through any of its

aliases is identical.

Byte Ordering

Registers that occupy more than 1 byte of address space

are shown with the lowest address in the highest-order byte

lane to match the byte-ordering on the bus. For example, the

model_id register is R0x3000−1. In the register table the

default value is shown as 0x0754. This means that a READ

from address 0x3000 would return 0x07, and a READ from

address 0x3001 would return 0x54. When reading this

register as two 8-bit transfers on the serial interface, the 0x07

will appear on the serial interface first, followed by the 0x54.

www.onsemi.com

APPLICATION NOTE

AND9385/D

www.onsemi.com

2

Address Alignment

All register addresses are aligned naturally. Registers that

occupy two bytes of address space are aligned to even 16-bit

addresses, and registers that occupy four bytes of address

space are aligned to 16-bit addresses that are an integer

multiple of 4.

Bit Representation

For clarity, 32-bit hex numbers are shown with an

underscore between the upper and lower 16 bits. For

example: 0x3000_01AB.

Data Format

Most registers represent an unsigned binary value or set of

bit fields. For all other register formats, the format is stated

explicitly at the start of the register description. The notation

for these formats is shown in Table 2.

Table 2. DATA FORMATS

Name Description

FIX16 Signed fixed-point, 16-bit number: two’s complement number, 8 fractional bits.

Examples:

0x0100 = 1.0

0x8000 = –128

0xFFFF = –0.0039065

UFIX16 Unsigned fixed-point, 16-bit number: 8.8 format.

Examples:

0x0100 = 1.0

0x280 = 2.5

FLP32 Signed floating-point, 32-bit number: IEEE 754 format.

Example: 0x4280_0000 = 64.0

REGISTER BEHAVIOR

Registers vary from “read-only”, “read/write”, and “read,

write-1-to-clear”.

Double-Buffered Registers

Some sensor settings cannot be changed during frame

readout. For example, changing x_addr_start partway

through frame readout would result in inconsistent row

lengths within a frame. To avoid this, the AR0135CS

double-buffers many registers by implementing a “pending”

and a “live” version. READs and WRITEs access the

pending register; the live register controls the sensor

operation.

The value in the pending register is transferred to a live

register at a fixed point in the frame timing, called frame

start. Frame start is defined as the point at which the first

dark row is read out internally to the sensor. In the register

tables the “Buffering” column shows which registers or

register fields are single- or double-buffered.

Bad Frames

A bad frame is a frame where all rows do not have the

same integration time or where offsets to the pixel values

have changed during the frame.

Many changes to the sensor register settings can cause a

bad frame. For example, when line_length_pck is changed,

the new register value does not affect sensor behavior until

the next frame start. However, the frame that would be read

out at that frame start will have been integrated using the old

row width, so reading it out using the new row width would

result in a frame with an incorrect integration time.

By default, bad frames are not masked. If the masked bad

frame option is enabled, both LV and FV are inhibited for

these frames so that the vertical blanking time between

frames is extended by the frame time.

In the register tables, the “Bad Frame” column shows

where changing a register or register field will cause a bad

frame. This notation is used:

• N − No. Changing the register value will not produce

a bad frame.

• Y − Yes. Changing the register value might produce

a bad frame.

• YM − Yes; but the bad frame will be masked out when

mask_corrupted_frames (R0x301A[9]) is set to “1”.

AND9385/D

www.onsemi.com

3

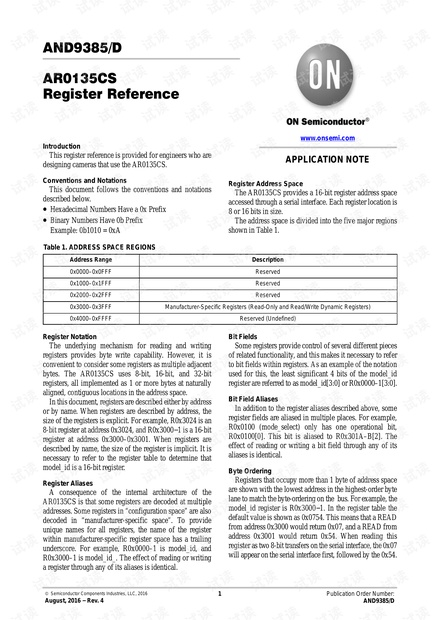

REGISTER SUMMARY TABLES

NOTE: Green1 corresponds to greenR; green2 corresponds to greenB.

Caution:Writing and changing the value of a reserved register (word or bit) puts the device in an unknown state and may

damage the device.

Manufacturer-Specific Registers

Table 3. MANUFACTURER-SPECIFIC REGISTER LIST

(1 = read-only, always 1; 0 = read-only, always 0; d = programmable; ? = read-only, dynamic)

Register

Dec (Hex)

Name

Data Format

(Binary)

Default Value

Dec (Hex)

R12288

(R0x3000)

chip_version_reg dddd dddd dddd dddd 1876

(0x0754)

R12290

(R0x3002)

y_addr_start 0000 00dd dddd dddd 0

(0x0000)

R12292

(R0x3004)

x_addr_start 0000 0ddd dddd dddd 0

(0x0000)

R12294

(R0x3006)

y_addr_end 0000 00dd dddd dddd 959

(0x03BF)

R12296

(R0x3008)

x_addr_end 0000 0ddd dddd dddd 1279

(0x04FF)

R12298

(R0x300A)

frame_length_lines dddd dddd dddd dddd 990

(0x03DE)

R12300

(R0x300C)

line_length_pck dddd dddd dddd ddd0 1388

(0x056C)

R12302

(R0x300E)

revision_number dddd dddd 36

(0x24)

R12304

(R0x3010)

lock_control dddd dddd dddd dddd 48879

(0x0BEEF)

R12306

(R0x3012)

coarse_integration_time dddd dddd dddd dddd 100

(0x0064)

R12308

(R0x3014)

fine_integration_time dddd dddd dddd dddd 0

(0x0000)

R12310

(R0x3016)

coarse_integration_time_cb dddd dddd dddd dddd 16

(0x0010)

R12312

(R0x3018)

fine_integration_time_cb dddd dddd dddd dddd 0

(0x0000)

R12314

(R0x301A)

reset_register d00d dddd dddd dddd 4312

(0x10D8)

R12318

(R0x301E)

data_pedestal 0000 dddd dddd dddd 168

(0x00A8)

R12326

(R0x3026)

gpi_status 0000 0000 0000 ???? 0

(0x0000)

R12328

(R0x3028)

row_speed 0000 0000 0ddd 0000 16

(0x0010)

R12330

(R0x302A)

vt_pix_clk_div 0000 0000 dddd dddd 8

(0x0008)

R12332

(R0x302C)

vt_sys_clk_div 0000 0000 000d dddd 1

(0x0001)

R12334

(R0x302E)

pre_pll_clk_div 0000 0000 00dd dddd 2

(0x0002)

R12336

(R0x3030)

pll_multiplier 0000 0000 dddd dddd 44

(0x002C)

R12338

(R0x3032)

digital_binning 0000 0000 00dd 00dd 0

(0x0000)

AND9385/D

www.onsemi.com

4

Table 3. MANUFACTURER-SPECIFIC REGISTER LIST (continued)

(1 = read-only, always 1; 0 = read-only, always 0; d = programmable; ? = read-only, dynamic)

Register

Dec (Hex)

Default Value

Dec (Hex)

Data Format

(Binary)

Name

R12346

(R0x303A)

frame_count dddd dddd dddd dddd 0

(0x0000)

R12348

(R0x303C)

frame_status 0000 0000 0000 00?? 0

(0x0000)

R12352

(R0x3040)

read_mode dd00 0000 0000 0000 0

(0x0000)

R12356

(R0x3044)

dark_control 000d ddd0 d000 dd00 1028

(0x0404)

R12358

(R0x3046)

flash ??00 000d d000 0000 0

(0x0000)

R12374

(R0x3056)

green1_gain 0000 0000 dddd dddd 32

(0x0020)

R12376

(R0x3058)

blue_gain 0000 0000 dddd dddd 32

(0x0020)

R12378

(R0x305A)

red_gain 0000 0000 dddd dddd 32

(0x0020)

R12380

(R0x305C)

green2_gain 0000 0000 dddd dddd 32

(0x0020)

R12382

(R0x305E)

global_gain 0000 0000 dddd dddd 32

(0x0020)

R12388

(R0x3064)

embedded_data_ctrl 000d dddd d0d0 dddd 6530

(0x1982)

R12398

(R0x306E)

datapath_select dddd dd0d 000d 00dd 36864

(0x9000)

R12400

(R0x3070)

test_pattern_mode 0000 000d 0000 0ddd 0

(0x0000)

R12402

(R0x3072)

test_data_red 0000 dddd dddd dddd 0

(0x0000)

R12404

(R0x3074)

test_data_greenr 0000 dddd dddd dddd 0

(0x0000)

R12406

(R0x3076)

test_data_blue 0000 dddd dddd dddd 0

(0x0000)

R12408

(R0x3078)

test_data_greenb 0000 dddd dddd dddd 0

(0x0000)

R12410

(R0x307A)

test_raw_mode 0000 0000 0000 00dd 0

(0x0000)

R12422

(R0x3086)

seq_data_port dddd dddd dddd dddd 0

(0x0000)

R12424

(R0x3088)

seq_ctrl_port ?d00 000d dddd dddd 49152

(0xC000)

R12426

(R0x308A)

x_addr_start_cb 0000 0ddd dddd dddd 2

(0x0002)

R12428

(R0x308C)

y_addr_start_cb 0000 00dd dddd dddd 4

(0x0004)

R12430

(R0x308E)

x_addr_end_cb 0000 0ddd dddd dddd 1281

(0x0501)

R12432

(R0x3090)

y_addr_end_cb 0000 00dd dddd dddd 963

(0x03C3)

R12448

(R0x30A0)

x_even_inc 0000 0000 0000 000? 1

(0x0001)

R12450

(R0x30A2)

x_odd_inc 0000 0000 0000 000d 1

(0x0001)

剩余17页未读,继续阅读

leowangef

- 粉丝: 3

- 资源: 5

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论0