没有合适的资源?快使用搜索试试~ 我知道了~

首页JESD204B应用指南-ADI-中文版.pdf

资源详情

资源评论

资源推荐

内容

1

|

JESD204B应用指南

MS-2374:什么是JESD204标准,为什么我们要重视它? ......................................................................................... 2

MS-2304:高速转换器应用指南: 数字数据输出 ...................................................................................................... 6

MS-2442:JESD204B与串行LVDS接口相比针对宽带数据转换器应用的考虑 ........................................................ 10

MS-2448:抓住JESD204B接口功能的关键问题.......................................................................................................... 14

MS-2433:使用JESD204B同步多个ADC ........................................................................................................................ 21

MS-2447:JESD204B发射器的三个关键物理层(PHY)性能指标................................................................................. 23

MS-2446:交错ADC入门................................................................................................................................................. 31

MS-2438:针对高速数据转换器的最新高速JESD204B标准带来了验证挑战........................................................ 36

MS-2503:消除影响JESD204B链路传输的因素.......................................................................................................... 44

MS-2672:JESD204B子类(第一部分): JESD204B子类简介和确定性延迟 ............................................................ 48

MS-2677:JESD204B子类(第二部分):子类1与子类2系统考虑因素 ...................................................................... 54

MT-201:FPGA与ADC数字数据输出的接口.................................................................................................................. 60

AD9144:四通道、16位、2.8 GSPS, TxDAC+

®

数模转换器数据手册(第一页) .......................................................... 70

AD9234:12位、1 GSPS JESD204B双通道模数转换器数据手册(第一页) ................................................................ 71

AD9250:14位、170 MSPS/250 MSPS、JESD204B、双通道模数转换器数据手册(第一页) ................................... 72

AD9625:12位、2.5/2.0 GSPS、1.3 V/2.5 V模数转换器数据手册初始版(第一页).................................................... 73

AD9675:八通道超声波AFE带JESD204B数据手册(第一页) ....................................................................................... 74

AD9680:14位、1 GSPS JESD204B双通道模数转换器数据手册(第一页) ................................................................ 75

有关JESD204的更多信息 ............................................................................................................................................... 76

一种新的转换器接口的使用率正在稳步上升,并且有望成

为未来转换器的协议标准。这种新接口——JESD204——诞

生于几年前,其作为转换器接口经过几次版本更新后越来

越受瞩目,效率也更高。随着转换器分辨率和速度的提

高,对于效率更高的接口的需求也随之增长。JESD204接

口可提供这种高效率,较之其前代CMOS和LVDS产品在速

度、尺寸和成本上更有优势。采用JESD204的设计拥有更

快的接口带来的好处,能与转换器更快的采样速率同步。

此外,引脚数量的减少使得封装尺寸更小且布线数量更

少,这些都让电路板更容易设计并且整体系统成本更低。

该标准可以方便地调整,从而满足未来需求 这从它已经历

的两个版本的变化中即可看出。自从2006年发布以来,

JESD204标准经过两次更新,目前版本为B。由于该标准已

为更多的转换器供应商、用户以及FPGA制造商所采纳,

它被细分并增加了新特性,提高了效率和实施的便利性。

此标准既适用于模数转换器(ADC)也适用于数模转换器

(DAC),主要用做FPGA的通用接口(也可能用于ASIC)。

JESD204——它是什么?

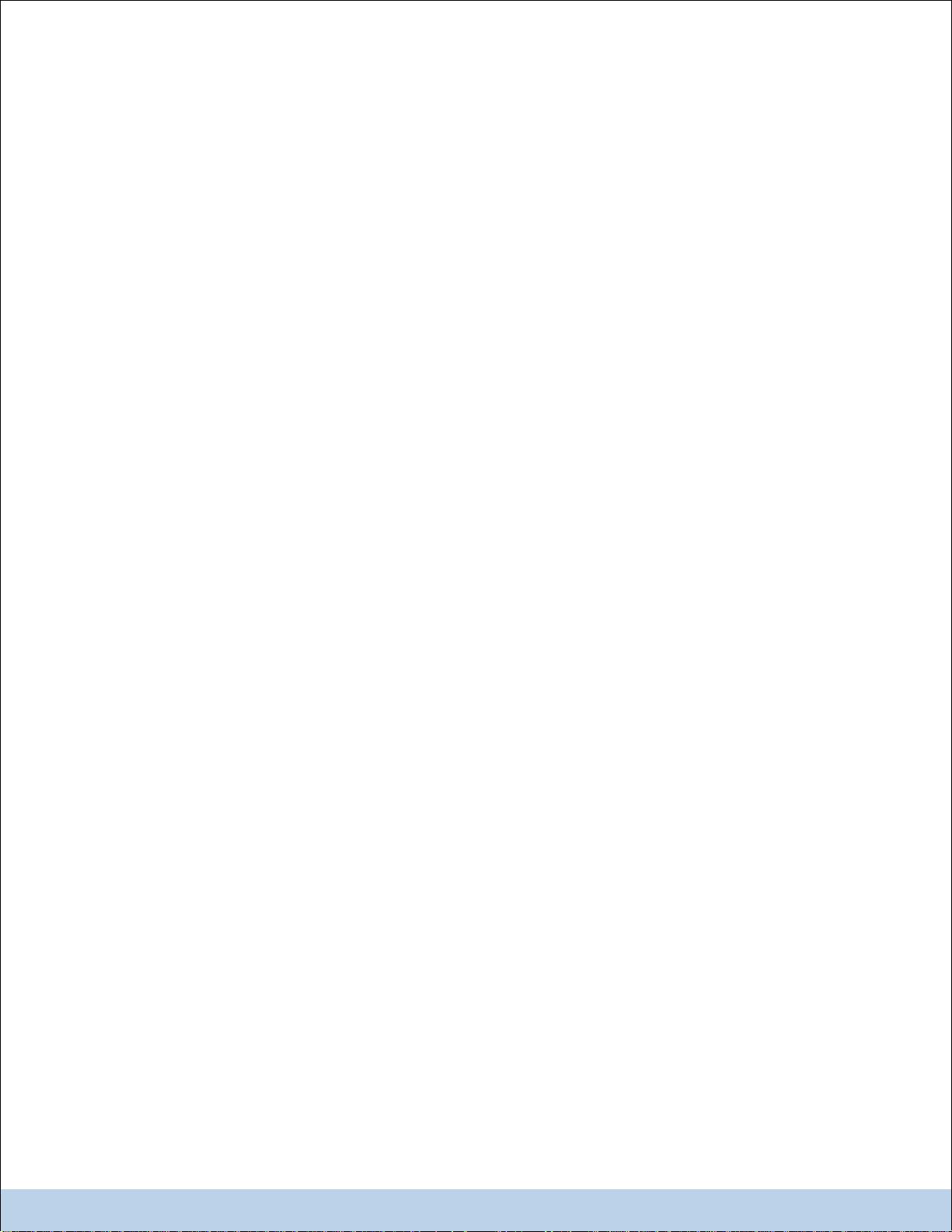

2006年4月,JESD204最初版本发布。该版本描述了转换器

和接收器(通常是FPGA或ASIC)之间数Gb的串行数据链

路。在JESD204的最初版本中,串行数据链路被定义为一

个或多个转换器和接收器之间的单串行通道。图1给出了

图形说明。图中的通道代表M个转换器和接收器之间的物

理接口,该接口由采用电流模式逻辑(CML)驱动器和接收

器的差分对组成。所示链路是转换器和接收器之间的串行

数据链路。帧时钟同时路由至转换器和接收器,并为设备

间的JESD204链路提供时钟。

通道数据速率定义为312.5 Mbps与3.125 Gbps之间,源阻抗

与负载阻抗定义为100 Ω ±20%。差分电平定义为标称800 mV

峰峰值、共模电平范围从0.72 V至1.23 V。该链路利用8b/10b

编码,采用嵌入式时钟,这样便无需路由额外的时钟线

路,以及相关的高数据速率下传输的数据与额外的时钟信

号对齐的复杂性。当JESD204标准开始受公众关注时,人

们开始意识到该标准需要修订以支持多个转换器下的多

路、对齐的串行通道,以满足转换器日益增长的速度和分

辨率。

这种认识促成了2008年4月份JESD204第一个修订版的发

布,即JESD204A。此修订版增加了支持多个转换器下的多

路对齐串行通道的能力。该版本所支持的通道数据速率依

然为312.5 Mbps至3.125 Gbps,另外还保留了帧时钟和电气

接口规范。增加了对多路对齐串行通道的支持,可让高采

样速率和高分辨率的转换器达到3.125 Gbps的最高支持数据

速率。图2以图形表示JESD204A版本中增加的功能,即支

持多通道。

技术文章

MS-2374

www.analog.com

Page 1 of 4 ©2013 Analog Devices, Inc. All rights reserved.

图1. JESD204最初标准

|

2

什么是JESD204标准,为什么我

们要重视它?

作者:Jonathan Harris,ADI公司应用工程师

JESD204B应用指南

虽然最初的JESD204标准和修订后的JESD204A标准在性能

上都比老的接口标准要高,它们依然缺少一个关键因素。

这一缺少的因素就是链路上串行数据的确定延迟。对于转

换器,当接收到信号时,若要正确重建模拟域采样信号,

则关键是了解采样信号和其数字表示之间的时序关系(虽然

这种情况是针对ADC而言,但DAC的情况类似)。该时序

关系受转换器的延迟影响,对于ADC,它定义为输入信号采

样边沿的时刻直至转换器输出数字这段时间内的时钟周期

数。类似地,对于DAC,延迟定义为数字信号输入DAC的

时刻直至模拟输出开始转变这段时间内的时钟周期数。

JESD204及JESD204A标准中没有定义可确定性设置转换器

延迟和串行数字输入/输出的功能。另外,转换器的速度和

分辨率也不断提升。这些因素导致了该标准的第二个版

本——JESD204B。

2011年7月,第二版本标准发布,称为JESD204B,即当前

版本。修订后的标准中,其中一个重要方面就是加入了实

现确定延迟的条款。另外,对数据速率的支持上升到了

12.5 Gbps,并分成设备的不同速度等级。此修订版标准使用

设备时钟作为主要时钟源,而不是像之前版本那样以帧时

钟作为主时钟源。图3表示JESD204B版本中的新增功能。

在JESD204标准之前的两个版本中,没有确保通过接口的

确定延迟相关的条款。JESD204B修订版通过提供一种机

制,确保两个上电周期之间以及链路重新同步期间,延迟

是可重现和确定性的。其工作机制之一是:在定义明确的

时刻使用SYNC~输入信号,同时初始化所有通道中转换器

最初的通道对齐序列。另一种机制是使用SYSREF信号——

一种JESD204B定义的新信号。SYSREF信号作为主时序参

考,通过每个发射器和接收器的设备时钟以及本地多帧时

钟对齐所有内部分频器。这有助于确保通过系统的确定延

迟。JESD204B规范定义了三种设备子类:子类0——不支

持确定性延迟;子类1——使用SYSREF的确定性延迟;子

类2——使用SYNC~的确定性延迟。子类0可与JESD204A链

路做简单对比。子类1主要针对工作在500 MSPS或以上的转

换器,而子类2y主s要针对工作在500 MSPS以下的转换器。

除了确定延迟,JESD204B支持的通道数据速率上升到

12.5 Gbps,并将设备划分为三个不同的速度等级:所有三个

速度等级的源阻抗和负载阻抗相同,均定义为100 Ω ±20%。

第一速度等级与JESD204和JESD204A标准定义的通道数据速

率相同,即通道数据电气接口最高为3.125 Gbps。JESD204B

的第二速度等级定义了通道数据速率最高为6.375 Gbps的电

气接口。该速度等级将第一速度等级的最低差分电平从

500 mV峰峰值降为400 mV峰峰值。JESD204B的第三速度等

级定义了通道数据速率最高为12.5 Gbps的电气接口。该速度

等级电气接口要求的最低差分电平降低至360 mV峰峰值。

随着不同速度等级的通道数据速率的上升,通过降低所需

驱动器的压摆率,使得所需最低差分电平也随之降低,以

便物理实施更为简便。

MS-2374

Page 2 of 4

图2. 第一版 – JESD204A

图3. 第二(当前)版 – JESD204B

3

|

JESD204B应用指南

为提供更多的灵活性,JESD204B版本采用设备时钟而非帧

时钟。在之前的JESD204和JESD204A版本中,帧时钟是

JESD204系统的绝对时间参照。帧时钟和转换器采样时钟

通常是相同的。这样就没有足够的灵活性,而且当要将此

同样的信号路由给多个设备并计数不同路由路径之间的偏

斜时,就会对系统设计产生不必要的复杂性。JESD204B

中,采用设备时钟作为JESD204系统每个元件的时间参

照。每个转换器和接收器分别接收由时钟发生器电路产生

的设备时钟,该发生器电路负责从同一个源产生所有设备

的时钟。这让系统设计更加灵活,但需为每个给定设备指

定帧时钟和设备时钟之间的关系。

JESD204——为什么我们要重视它?

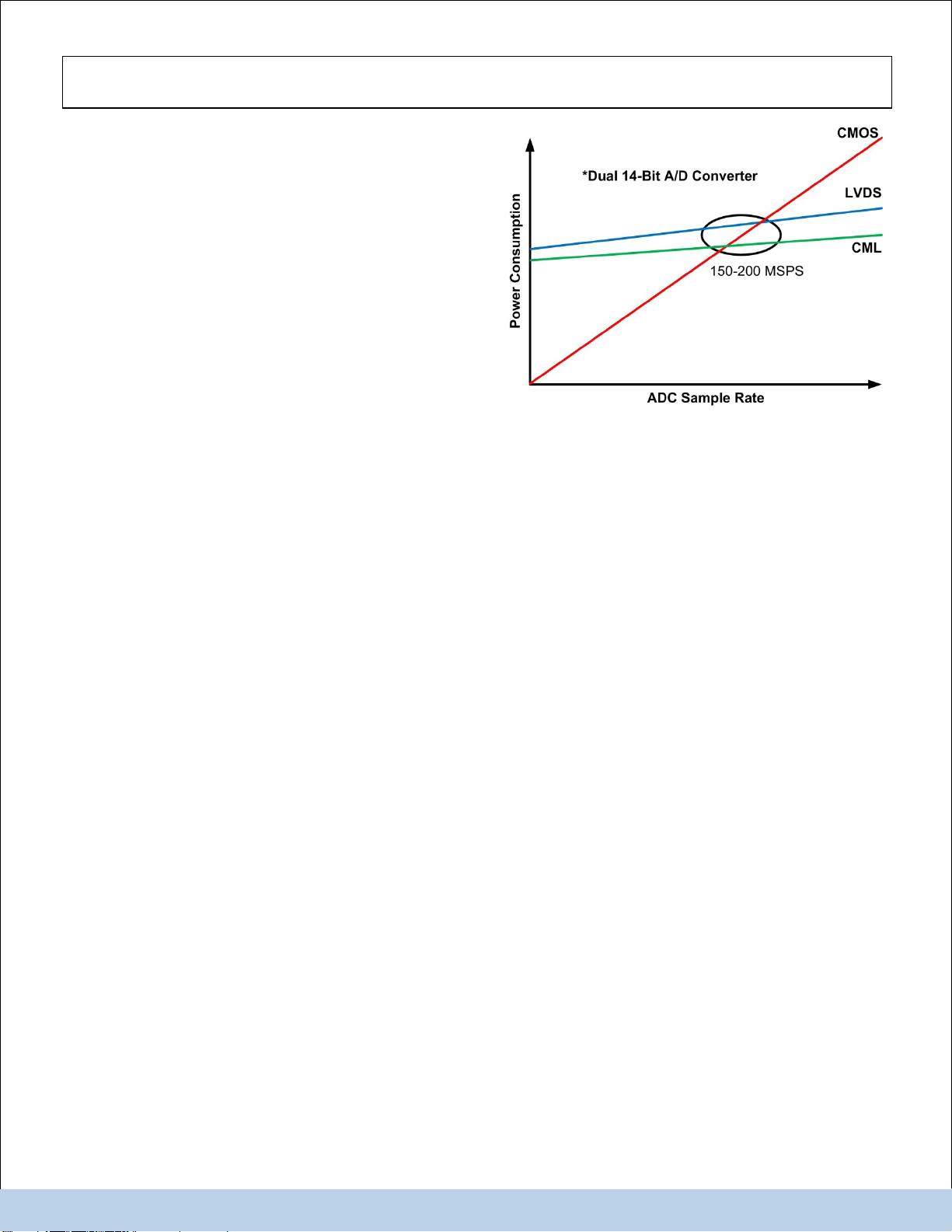

就像几年前LVDS开始取代CMOS成为转换器数字接口技术

的首选,JESD204有望在未来数年内以类似的方式发展。

虽然CMOS技术目前还在使用中,但已基本被LVDS所取

代。转换器的速度和分辨率以及对更低功耗的要求最终使

得CMOS和LVDS将不再适合转换器。随着CMOS输出的数

据速率提高,瞬态电流也会增大,导致更高的功耗。虽然

LVDS的电流和功耗依然相对较为平坦,但接口可支持的

最高速度受到了限制。这是由于驱动器架构以及众多数据

线路都必须全部与某个数据时钟同步所导致的。图4显示

一个双通道14位ADC的CMOS、LVDS和CML输出的不同功

耗要求。

在大约150 MSPS至200 MSPS和14位分辨率时,就功耗而言,

CML输出驱动器的效率开始占优。CML的优点是:因为数

据的串行化,所以对于给定的分辨率,它需要的输出对数

少于LVDS和CMOS驱动器。JESD204B接口规范所说明的

CML驱动器还有一个额外的优势,因为当采样速率提高并

提升输出线路速率时,该规范要求降低峰峰值电压水平。

同样,针对给定的转换器分辨率和采样率,所需的引脚数

目也大为减少。表1显示采用200 MSPS转换器的三种不同接

口各自的引脚数目,转换器具有各种通道数和位分辨率。

在CMOS和LVDS输出中,数据用作每个通道数据的同步时

钟,使用CML输出时,JESD204B数据传输的最大数据速率

为4.0 Gbps。从该表中可以发现,使用CML驱动器的JESD204B

优势十分明显,引脚数大为减少。

MS-2374

3

Page 3 of 4

图4. CMOS、LVDS和CML驱动器功耗比较

|

4

JESD204B应用指南

剩余77页未读,继续阅读

jhr12300

- 粉丝: 2

- 资源: 11

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- 2023年中国辣条食品行业创新及消费需求洞察报告.pptx

- 2023年半导体行业20强品牌.pptx

- 2023年全球电力行业评论.pptx

- 2023年全球网络安全现状-劳动力资源和网络运营的全球发展新态势.pptx

- 毕业设计-基于单片机的液体密度检测系统设计.doc

- 家用清扫机器人设计.doc

- 基于VB+数据库SQL的教师信息管理系统设计与实现 计算机专业设计范文模板参考资料.pdf

- 官塘驿林场林防火(资源监管)“空天地人”四位一体监测系统方案.doc

- 基于专利语义表征的技术预见方法及其应用.docx

- 浅谈电子商务的现状及发展趋势学习总结.doc

- 基于单片机的智能仓库温湿度控制系统 (2).pdf

- 基于SSM框架知识产权管理系统 (2).pdf

- 9年终工作总结新年计划PPT模板.pptx

- Hytera海能达CH04L01 说明书.pdf

- 数据中心运维操作标准及流程.pdf

- 报告模板 -成本分析与报告培训之三.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论1