没有合适的资源?快使用搜索试试~ 我知道了~

首页Verilog串口通信程序(详细注释)

Verilog串口通信程序(详细注释)

Verilog串口通信程序,详细注释自己看了很多材料以后,精心整理的串口通信实验原理和指导,在网上找了很多代码,大部分因为没有很好的注释,看起来很头疼,于是自己写了一份,附带详细的注释,在modelsim仿真器上已经得到验证,现在传上来,仅供参考。 PS1:最后部分给出了一个测试文件,写的非常简单,只是验证了功能,不是很好的测试; PS2:代码部分看上去有点乱,因为在word中代码的层次结构无法清晰显示,如有需要,下载后把代码copy到notepad++这种类似的专用变成工具里面,就很清晰的显示代码和注释了。

资源详情

资源评论

资源推荐

自己看了很多材料以后,精心整理的串口通信实验原理和指导,在

网上找了很多代码,大部分因为没有很好的注释,看起来很头疼,

于是自己写了一份,附带详细的注释,在 仿真器上已经

得到验证,现在传上来,仅供参考。

最后部分给出了一个测试文件,写的非常简单,只是验证了功

能,不是很好的测试;

:代码部分看上去有点乱,因为在 中代码的层次结构无

法清晰显示,如有需要,下载后把代码 到 这种

类似的专用变成工具里面,就很清晰的显示代码和注释了。

第一部分:实验原理

串行通信要求的传输线少,可靠性高,传输距离远,被广泛应用于计算机

和外设的数据交换。通常都由通用 异步收发器 来实现串口通信的功能。

在实际应用中,往往只需要 的几个主要功能,专用的接口芯片会造成资

源浪费和成本提高。随着 ! 的飞速发展与其在现代电子设计中的广

泛应用, ! 功能强大、开发过程投资小、周期短、可反复编程、保

密性好等特点也越来越明显。因此可以充分利用其资源,在芯片上集成

功能模块,从而简化了电路、缩小了体积、提高了可靠性,而且设计时的灵活

性更大,周期更短。

UART 简介

("#$%#"# 通用异步收发

器)是一种应用广泛的短距离串行传输接口。常常用于短距离、低速、低成本

的通讯中。&'(、&'、)*+'( 等芯片都是常见的 器件。

基本的 通信只需要两条信号线(,!、,!)就可以完成数据的相

互通信,接收与发送是全双工形式。,! 是 发送端,为输出;,! 是

接收端,为输入。

的基本特点是:

()在信号线上共有两种状态,可分别用逻辑 (高电平)和逻辑 ((低

电平)来区分。在发送器空闲时,数据线应该保持在逻辑高电平状态。

()起始位(#-):发送器是通过发送起始位而开始一个字符传送

起始位使数据线处于逻辑 ( 状态,提示接受器数据传输即将开始。

(.)数据位(!#-):起始位之后就是传送数据位。数据位一般为

& 位一个字节的数据(也有 * 位、/ 位的情况),低位( - )在前,高位

( 0- )在后。

(+)校验位(#-):可以认为是一个特殊的数据位。校验位一般

用来判断接收的数据位有无错误,一般是奇偶校验。在使用中,该位常常取消。

(')停止位:停止位在最后,用以标志一个字符传送的结束,它对应于逻

辑 状态。

(*)位时间:即每个位的时间宽度。起始位、数据位、校验位的位宽度是

一致的,停止位有 (1' 位、 位、1' 位格式,一般为 位。

(/)帧:从起始位开始到停止位结束的时间间隔称之为一帧。

(&)波特率: 的传送速率,用于说明数据传送的快慢。在串行通信

中,数据是按位进行传送的,因此传送速率用每秒钟传送数据位的数目来表示,

称之为波特率。如波特率 9600=9600bps(位/秒)。

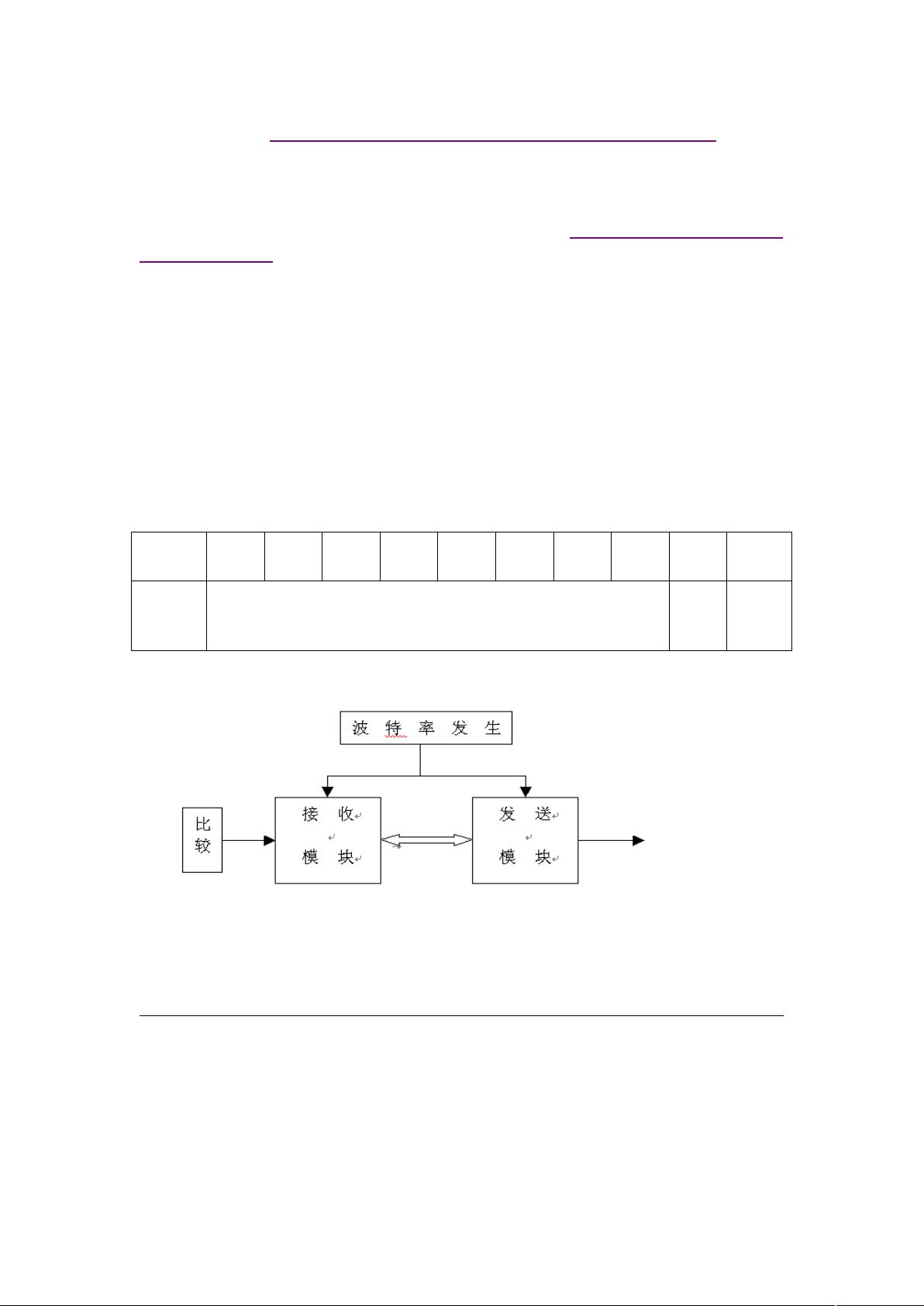

的数据帧格式为:

!( ! ! !. !+ !' !* !/ 2

起始位 数 据 位 校验

位

停止

位

# 系统组成 :如下图所示,# 由三个子模块组成:

波特率发生器;接收模块;发送模块;

模块设计:

系统由四部部分组成:顶层模块;波特率发生器; 接收器;

发送器

顶层模块

异步收发器的顶层模块由波特率发生器、 接收器和 发送器构成。

发送器的用途是将准备输出的并行数据按照基本 帧格式转为

,! 信号串行输出。

接收器接收 ,! 串行信号,并将其转化为并行数据。

波特率发生器就是专门产生一个远远高于波特率的本地时钟信号对输入

,!# #

####

不断采样,使接收器与发送器保持同步。# #

波特率发生器

波特率发生器实际上就是一个分频器。

可以根据给定的系统时钟频率(晶振时钟)和要求的波特率算出波特率分

频因子,算出的波特率分频因子作为分频器的分频数。

波特率分频因子可以根据不同的应用需要更改。

波特率发生器模块主要用于产生接收模块和发送模块的时钟频率,其实质

就是一个分频器,可以根据给定的系统时钟频率和要求的波特率算出波特率分

频因子,作为分频器的分频数。波特率发生器产生的时钟频率 CLK16X 不是

波特率时钟频率 CLK,而是波特率时钟频率 CLK 的 16 倍。

UART 在发送或接收数据时,使用的时钟信号频率 f 是波特率(b=9 600

b/s)的 16 倍,由外部系统时钟进行 * 分频得到。 每 * 个波特时钟发

送或接收一个二进制位,设计中采用的晶振频率 3'#045,那么波特率发生

器输出的时钟信号周期为:

UART 接收器

由于串行数据帧和接收时钟是异步的,由逻辑 转为逻辑 ( 可以被视为一

个数据帧的起始位。

然而,为了避免毛刺影响,能够得到正确的起始位信号,必须要求接收到

的起始位在波特率时钟采样的过程中至少有一半都是属于逻辑 0 才可认定接收

到的是起始位。由于内部采样时钟 bclk 周期(由波特率发生器产生)是发送

或接收波特率时钟频率的 16 倍,所以起始位需要至少 8 个连续 bclk 周期的逻

辑 0 被接收到,才认为起始位接收到,接着数据位和奇偶校验位将每隔 16 个

bclk 周期被采样一次(即每一个波特率时钟被采样一次)。

如果起始位的确是 16 个 bclk 周期长,那么接下来的数据将在每个位的中

点处被采样。

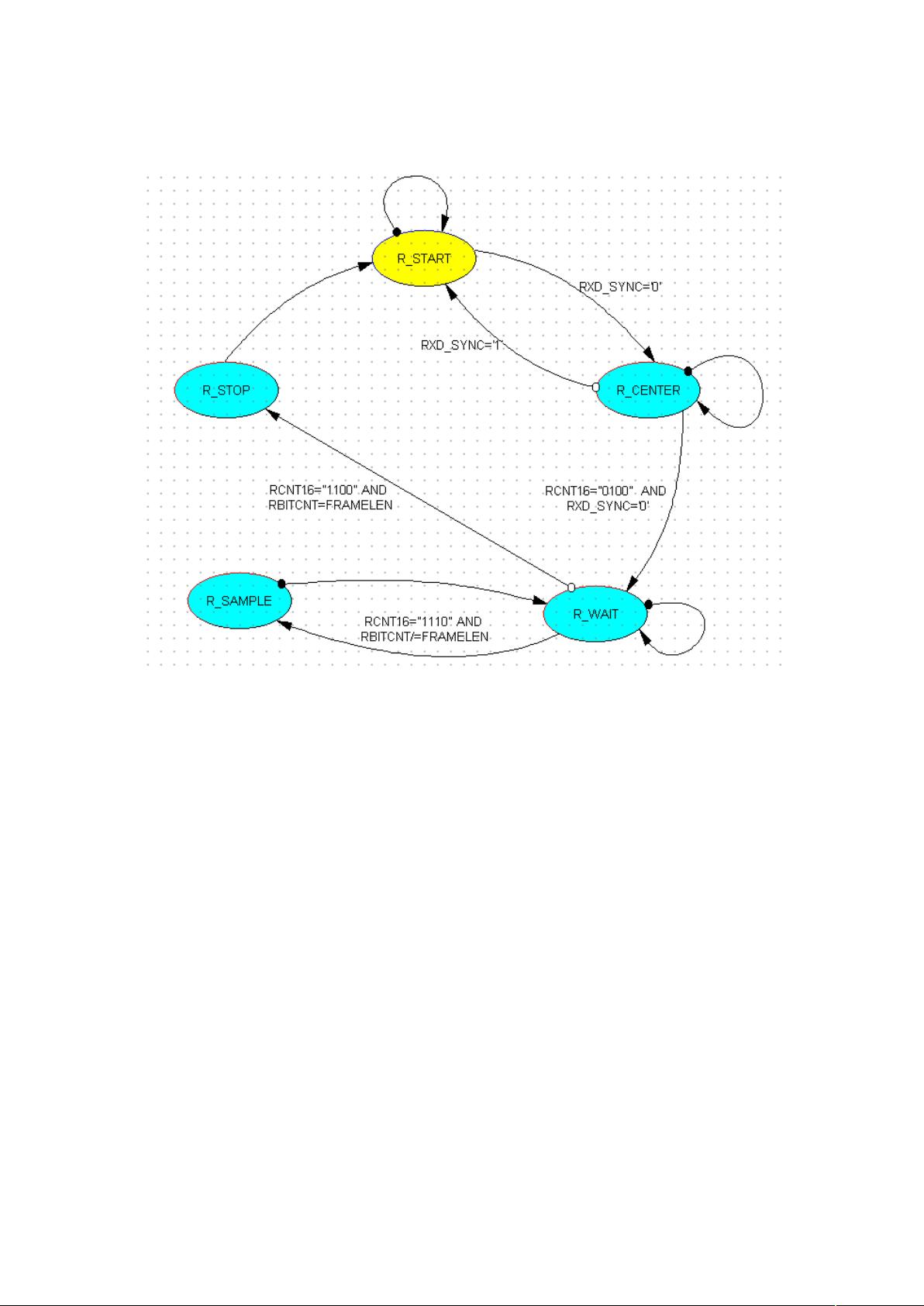

接收器的接收状态机

接收状态机一共有 ' 个状态: 6(等待起始位);67)7

(求中点);

689(等待采样);60 7(采样);62(停止位接收)。

R_START 状态

####当 接收器复位后,接收状态机将处于这一个状态。

在此状态,状态机一直在等待 ,! 的电平跳转,从逻辑 变为逻辑 (,即

起始位,这意味着新的一帧 数据帧的开始,一旦起始位被确定,状态机

将转入 67)7 状态。

状态图中的 RXD_SYNC 信号是 RXD 的同步信号,因为在进行逻辑 1 或

逻辑 0 判断时,不希望检测的信号是不稳定的,所以不直接检测 RXD 信号,

而是检测经过同步后的 RXD_SYNC 信号。

R_CENTER 状态

对于异步串行信号,为了使每一次都检测到正确的位信号,而且在较后的

数据位检测时累计误差较小,显然在每位的中点检测是最为理想的。

在本状态,就是由起始位求出每位的中点,通过对 bclk 的个数进行计数

(RCNT16),但计数值不是想当然的“ 1000”,要考虑经过一个状态,也

即经过了一个 bclk 周期,所希望得到的是在采样时 1/2 位。

另外,可能在 6 状态检测到的起始位不是真正的起始位,可能是

一个偶然出现的干扰尖脉冲(负脉冲)。这种干扰脉冲的周期是很短的,所以

可以认为保持逻辑 ( 超过 + 个位时间的信号一定是起始位。

R_WAIT 状态

当状态机处于这一状态,等待计满 15 个 bclk,在第 16 个 bclk 是进入

R_SAMPLE 状态进行数据位的采样检测,同时也判断是否采集的数据位长度

已达到数据帧的长度(FRAMELEN),如果到来,就说明停止位来临了。

FRAMELEN 在设计时是可更改的(使用了 Generic),在本设计中默

认为 8,即对应的 UART 工作在 8 位数据位、无校验位格式。

R_SAMPLE 状态

即数据位采样检测,完成后无条件状态机转入 689 状态,等待下次数

据位的到来。

R_STOP 状态

无论停止位是 还是 1' 位,或是 位,状态机在 62 不具体检测

,!,只是输出帧接收完毕信号(REC_DONE<=‘1’),停止位后状态机转

回到 R_START 状态,等待下一个帧的起始位。

补充:

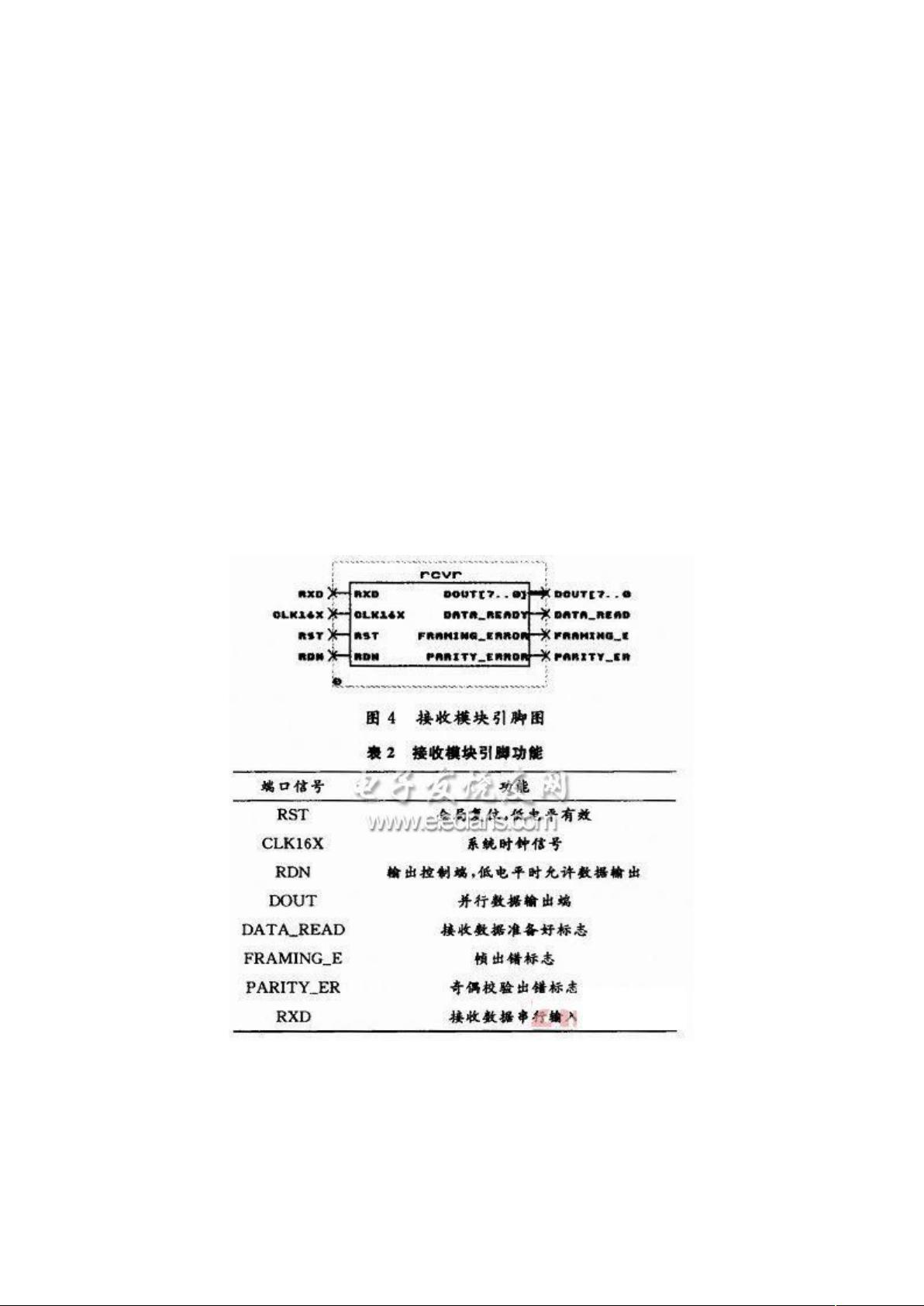

接收模块的作用是把收到的串行数据转换成并行数据进行输出,并判断收

到的数据是否有错。接收模块的引脚如图 + 所示,各引脚功能见表 。

:

接收器进入准备接收数据状态,不断监视串行输入线 ,! 端,如果出现低

电平,立刻启动起始位检测电路进行确认,一旦确认为接收到正确的起始位,

则以波特率作为采样时钟,对每个数据位的中间位置采样一次,并把采样到的

剩余20页未读,继续阅读

yan_lanfei

- 粉丝: 7

- 资源: 4

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论30