Product Brief

Overview

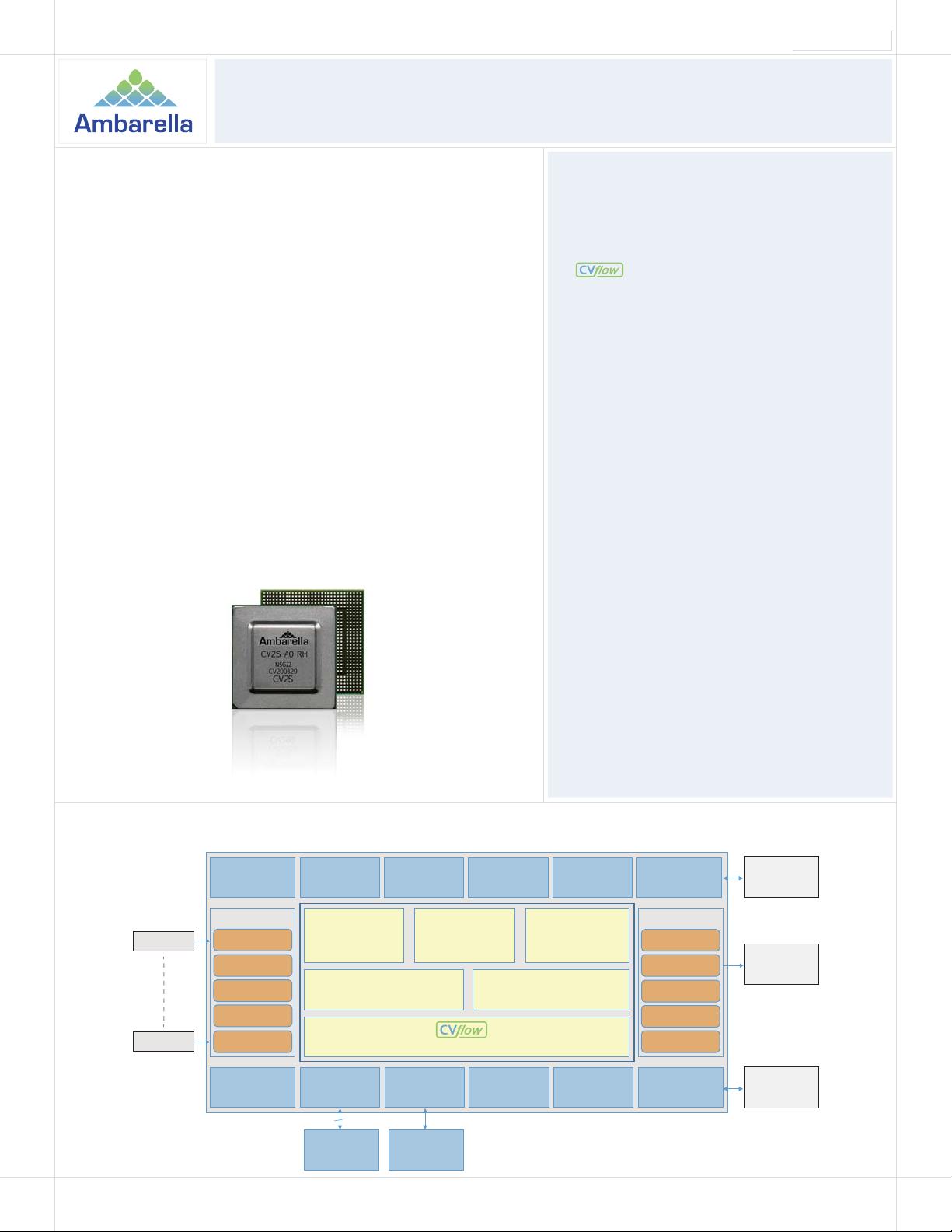

Block Diagram

The diagram below illustrates a design based on the Ambarella CV2S device.

Key Features

CV2S - Computer Vision SoC

for IP Cameras

The CV2S chip targets IP camera designs

Flexible Low-Power Platform

• 10 nm low-power CMOS process

• 64-bit quad-core Arm

®

Cortex

®

-A53 CPU

up to 1.0 GHz

• Linux kernel version 4.14+ or newer (64-bit)

•

®

vector processor for CNN/DNN

algorithms

• OTP, secure boot, TrustZone

, IO

virtualization

• Industry leading image sensors support

4K Computer Vision Engine

• CNN- / DNN-based processing: detection,

classification, tracking, and more

• CNN performance up to 20 times of CV1

• Dedicated CVflow computer vision processor

• Tools for high- and low-level algorithm

development

• Dedicated hardware for stereo processing

• CNN toolkit for easy porting with Caffe,

TensorFlow, and ONNX

• Open SDK

Advanced Image Processing

• More than 800 MPixels input rate

• Multi-exposure line-interleaved HDR

• Hardware dewarping engine support

• Electronic image stabilization (EIS)

• Six independent sensor inputs

• 3D motion-compensated temporal filtering

(MCTF)

• Superior low light processing

High-Efficiency Video Encoding

• H.265 and H.264 video compression

• Flexible multi-streaming capability

• Up to 4Kp30+1080p30 video performance

• Multiple CBR and VBR bit rate control modes

• Smart H.264 and H.265 encoder algorithms

Ambarella’s CV2S SoC combines image processing, 4Kp30+ video encoding,

and CVflow

®

computer vision processing in a single, low-power design.

The CV2S’s CVflow architecture provides the deep neural network (DNN)

processing required for the next generation of intelligent IP cameras.

Fabricated in advanced 10 nm process technology, it achieves an

industry-leading combination of low power and high performance in both

human vision and computer vision applications. In addition, CV2S also

includes dedicated hardware for the stereo processing unit that can support

stereo IP cameras.

The CV2S’s CVflow architecture provides cutting-edge computer vision

processing at full 4K resolution, with up to 20 times the CNN performance of

Ambarella’s CV1

®

to enable image recognition over long distances and with

high accuracy. It includes efficient 4K encoding in both AVC and HEVC

video formats, delivering high-resolution video streaming with very low

bit rates to minimize cloud storage costs. The CV2S’s next-generation

image signal processor (ISP) provides outstanding imaging in low-light

conditions while high dynamic range (HDR) processing extracts maximum

image detail in high contrast scenes, further enhancing the computer vision

capabilities of the chip. It includes a suite of advanced security features to

implement advanced on-device physical security, including secure boot,

TrustZone

®

, and key storage. A complete set of tools is provided to help

customers easily port their own neural networks on the CV2S.

Image Signal

Processor (ISP)

Video Codec

H.264

H.265

MJPEG

Quad Core

Arm

®

Cortex

®

-A53

Ambarella Memory System

Security

DRAM Scrambling, TrustZone, Random

Number Generator, Secure Boot, OTP

Video Input

HiSPi

™

Video Output

DDR

Interface

Audio Input

(I2S)

SD / SDIO NAND / NOR

SPII2C GPIO

Timers

WDT

Ethernet

LCD

10 / 100 /

GigE

LPDDR4 /

LPDDR4x

SD Card /

eMMC

Sensor 1

Sensor 6

MIPI CSI-2

Analog

Parallel

MIPI CSI-2

SLVS

LVDS

Parallel

HDMI

MIPI DSI

64-BIT

Stereo and Computer Vision Processor

USB 2.0

Host / Device

Wifi / BLE

JTAG

UART

Audio Output

(I2S)

评论0