没有合适的资源?快使用搜索试试~ 我知道了~

首页C8051F系列单片机使用中文应用笔记

C8051F系列单片机使用中文应用笔记

C8051F系列单片机使用中文应用笔记.pdf C8051F系列单片机使用中文应用笔记.pdf C8051F系列单片机使用中文应用笔记.pdf

资源详情

资源评论

资源推荐

C8051F MCU

应

用

笔

记

Silicon Laboratories Inc. 新华龙电子有限公司

4635 Boston Lane 深圳市福田区华强北路现代之窗大厦 A 座 13F C 室(518013)

Austin, TX 78735

0755-83645240 83645242 83645244 83645251

AN001 — 配置端口 I/O 交叉开关译码器

XBR0, XBR1,

XBR2

PRT3CF

P0

P1

P2

8

8

8

P3

P3

I/O

P3.0

P1

I/O

SMBus

2

SPI

4

UART

2

PCA

6

T0, T1,

T2

3

/SYSCLK

CNVSTR

P3.7

P1.0

P1.7

P2

I/O

P2.0

P2.7

P0

I/O

P0.0

P0.7

8

8

8

(P2.0-P2.7)

(P1.0-P1.7)

(P0.0-P0.7)

8

PRT0CF, PRT1CF,

PRT2CF

(P3.0-P3.7)

2

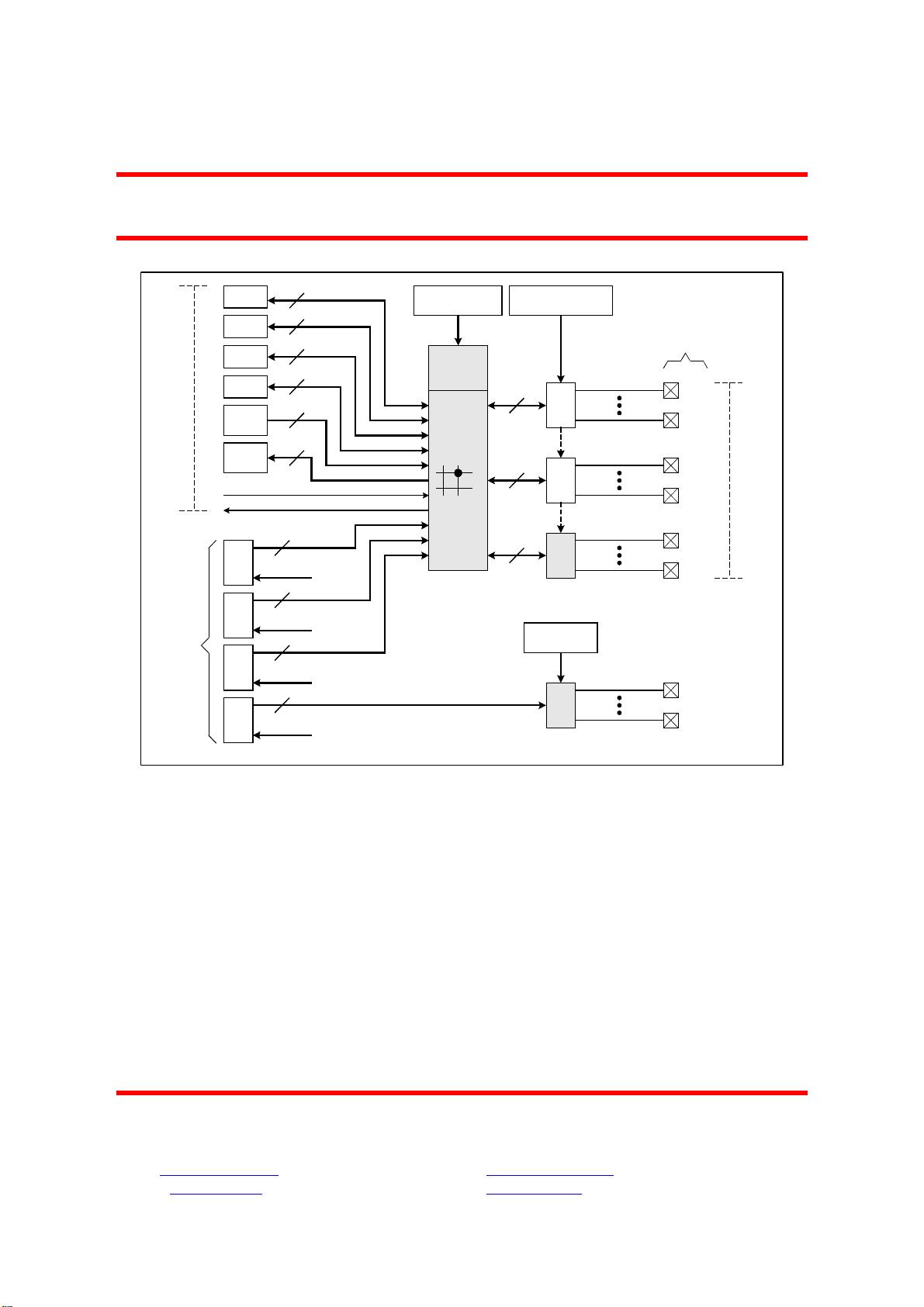

图1. 交叉开关译码器原理框图

外部引脚

高优先级

低优先级

寄存器

单元

单元

单元

单元

寄存器寄存器

优先级

译码器

数字

交叉开关

高优先级

低优先级

比较器

输 出

内部数字信号

端口

锁存器

引言

本应用笔记的目的是说明如何配置和使用端口 I/O 交叉开关译码器。本文提供软件示例。

如图 1 所示,交叉开关是一个多路选择器,它用于为器件内部的硬件外设分配 I/O 端口。例

如,它可以决定 UART 的 RXD 和 TXD 连到哪一个端口引脚。

交叉开关负责 SMBus、SPI、UART、定时器捕捉模块、外部 PCA 输入、比较器输出、定时

器外部输入、/SYSCLK 以及 A/D 转换启动输入的引脚分配。交叉开关必须在访问这些外设的 I/O

之前被配置和允许。

未指定的端口引脚作为通用 I/O。

交叉开关提供了两个关键的系统特性:

电话:

Email: mcuinfo@silabs.com

(版权所有)

电邮:shenzhen@xhl.com.cn

Internet: www.silabs.com

网址:www.xhl.com.cn

AN001 — 配置端口 I/O 交叉开关译码器

在端口 0、端口 1 和端口 2 上的所有未分配的通用 I/O 口引脚都被连续组合在一起。

对于引脚数量少的器件,它提供了外设选择的灵活性。外设选择只受限于可用的端口引脚数,

而不受限于哪一个引脚是可用的。这就允许系统设计者在使用引脚数少的器件时能选择将哪

些数字外设分配到器件上的数字 I/O 引脚。

关键点

为了使用端口 0、端口 1 或端口 2 的任何一个引脚作为输出,交叉开关必须被允许。

交叉开关译码器必须在任何一个数字外设被允许前配置。

交叉开关通常在复位时被配置一次,在复位处理过程的最开始处,以后不再进行配置。

交叉开关的设置改变器件的引脚分配。

每一种交叉开关设置导致唯一的器件引脚分配,如果你在交叉开关中允许或禁止外设,引脚

分配将发生变化。

对于输出端口引脚,其输出方式(漏极开路或推挽)必须被显式设置,即使那些由交叉开关

分配的端口引脚也是如此。例外情况是 SMBus 上的 SDA 和 SCL 及 UART 的 RXD 引脚,这

些引脚被自动配置为漏极开路。

交叉开关分配的输入引脚(例如 NSS 或/INT0)是开路或推挽并不重要。这些引脚被配置为

输入,而与相应端口配置寄存器的设置无关。为了将一个通用 I/O 引脚配置为输入,与这一

引脚相关的端口配置寄存器位必须被清 0,这样选择该引脚为漏极开路输出方式。此外,与

该引脚相关的端口位必须被置 1,这样使该引脚处于高阻态,或在 XBR2 中的 WEAKPUD 被

清 0 时弱上拉为高电平,这是端口引脚的复位配置。

在任意时刻可以通过读取相应端口 SFR 得到端口引脚的电平值,而不管交叉开关寄存器的设

置如何或引脚被配置为输入还是输出。

交叉开关寄存器中的允许位是独立的。与数字外设本身的允许位是分开的。

○ 外设部件在使用时不需要在交叉开关中被允许(例如,一个 PCA 模块即使在输出没有被接

到引脚的情况下也能产生中断)。

○ 那些在交叉开关中被允许但在它们自己的 SFR 中被禁止的外设,仍然控制端口引脚。这就

是说,端口引脚可以在任何时候被读取,但是输出被占用它的外设所控制,不能作为通用

输出口来访问。

端口 1 上的四个外部中断(P1.[4..7])是由引脚上的下降沿触发的,与下降沿触发源、交叉开

关设置或端口引脚的输出方式无关。

与标准 8051 不同的是,C8051 提供了真正的推挽输出。如果需要 8051 的上拉功能,可以通

过将相应的端口输出配置为“推挽”方式,然后再配置为“漏极开路”来进行软件仿真。

确定器件引脚分配

本节介绍如何使用优先权交叉开关译码表即表 4 来决定器件的引脚分配,这种分配基于交叉

开关寄存器中的外设选择,这些选择在图 2-图 4 中列出。

为了确定引脚分配,首先根据所需要的外设来配置交叉开关寄存器。然后从优先权交叉开关

译码表的顶部开始向下扫描,直到遇到第一个被允许的外设部件。该设备将使用 P0.0,如果需要

多个引脚,就可以按顺序从 P0.1 向后分配。例如,如果 SPI 是第一个被允许的外设,则 SCK、

MISO、MOSI 和 NSS 将分别被分配到 P0.0、P0.1、P0.2、P0.3。下一个被允许的外设将被分配到

2 AN01-1.1

AN001 — 配置端口 I/O 交叉开关译码器

引脚 P0.4。所有未分配的引脚作为通用 I/O。

例

1

假设一个应用需要:

SPI

UART

两个捕捉模块

/INT0

T2。

参考图 2-图 4 中的 I/O 端口交叉开关寄存器说明,交叉开关寄存器配置如下:

XBR0=00010110b;允许 UART、两个捕捉模块和 SPI

XBR1=00100100b;允许 T2 和/INT0

XBR2=01000000b;允许交叉开关

从表 4 的顶部开始我们发现 SPI 引脚将占用 P0.[0..3](因为不使用 SMBus),UART 占用引脚

P0.[4..5],CEX0 占用 P0.6,CEX1 占用 P0.7,/INT0 占用 P1.0,T2 占用 P1.1。其它端口引脚 P1.[2..7]

和 P2.[0..7]作为通用端口引脚。引脚分配情况列于表 1。

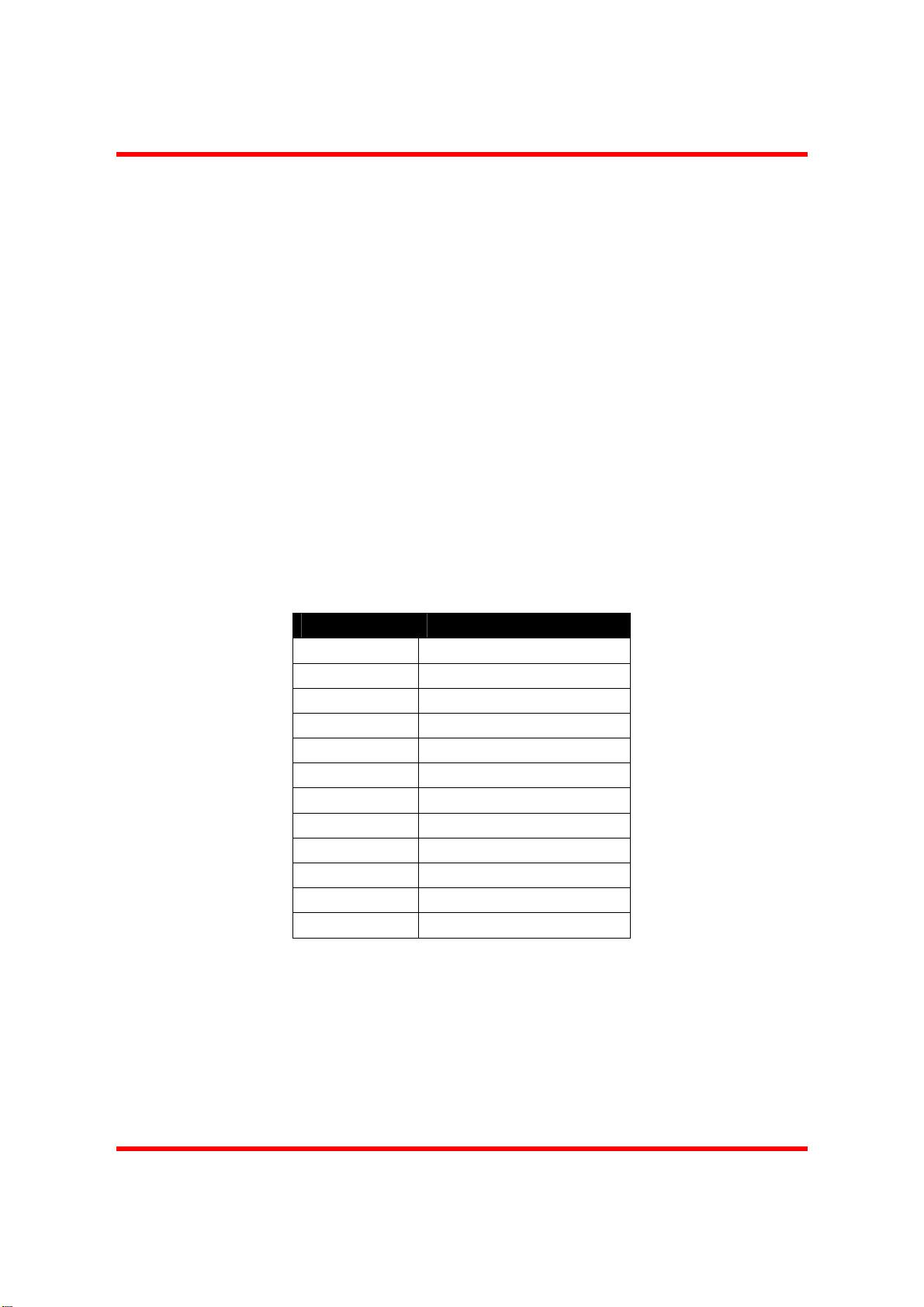

表 1. 例 1 的引脚分配

引脚 功能

P0.0 SCK

P0.1 MISO

P0.2 MOSI

P0.3 NSS

P0.4 TX

P0.5 RX

P0.6 CEX0

P0.7 CEX1

P1.0 /INT0

P1.1 T2

P1.[2..7] GPIO

P2.[0..7] GPIO

例

2

假设一个应用需要:

UART

/INT1

/SYSCLK

CNVSTR

交叉开关寄存器的配置如下:

AN01-1.1 3

AN001 — 配置端口 I/O 交叉开关译码器

XBR0=00000100b;允许 UART

XBR1=10010000b;允许/INT1 和/SYSCLK

XBR2=01000001b;允许 CNVSTR 和交叉开关

引脚分配情况列于表 2。

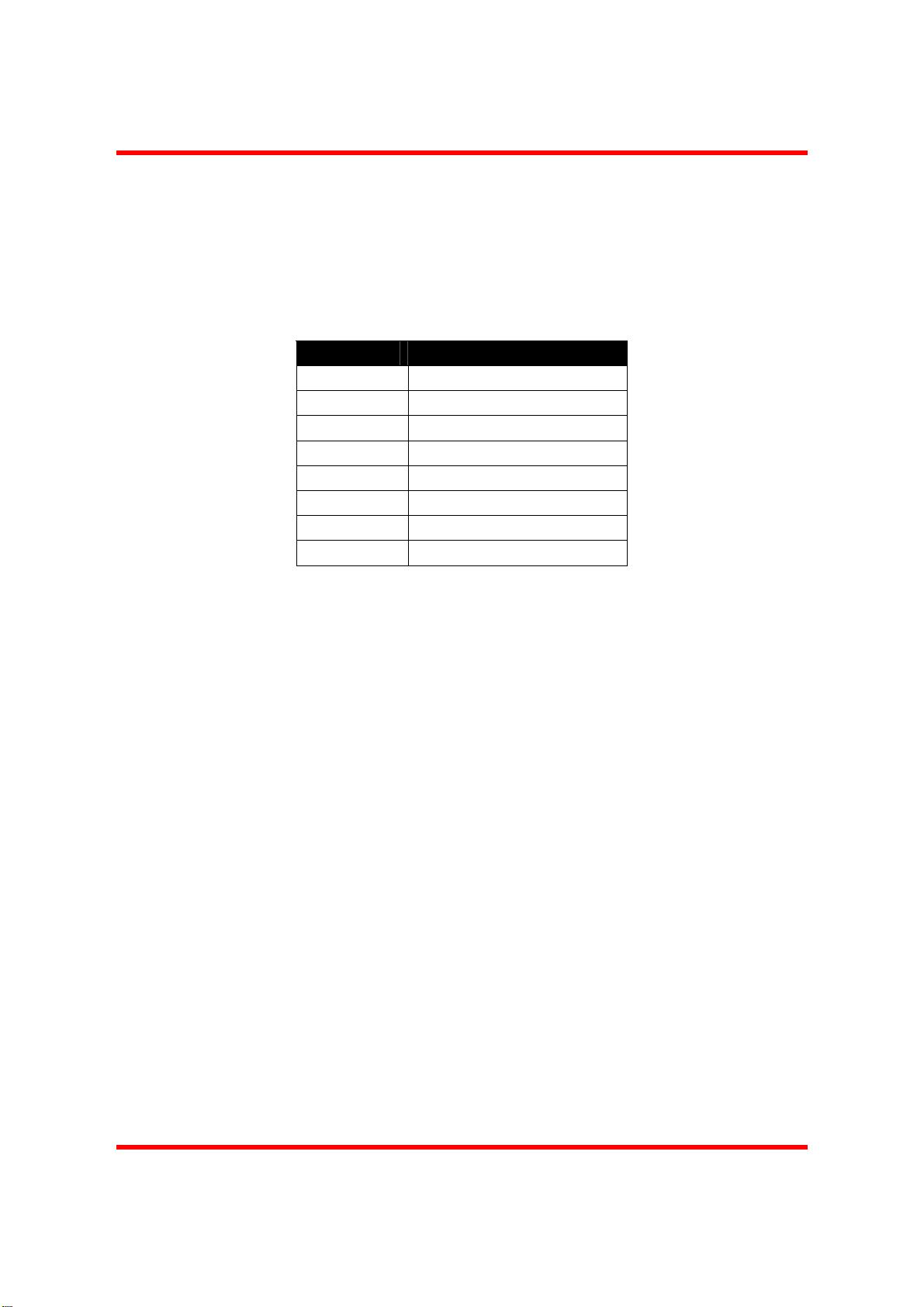

表 2. 例 2 的引脚分配

引脚 功能

P0.0 TX

P0.1 RX

P0.2 /INT1

P0.3 /SYSCLK

P0.4 CNVSTR

P0.5[5..7] GPIO

P1[0..7] GPIO

P2[0..7] GPIO

例

3

假设一个应用需要下列外设之外的所有部件:

定时器捕捉模块

SPI 端口

T0、T1 和 T2 输入

比较器输出

/SYSCLK。

也就是说需要下列部件:

SMBus(I2C 口)

UART

ECI

/INT0

/INT1

T2EX

CNVSTR

为了允许以上部件,我们将交叉开关寄存器配置如下:

XBR0=01000101b;允许 ECI、UART 和 SMBus

XBR1=01010100b;允许/INT0、/INT1 和 T2EX

XBR2=01000001b;允许 CNVSTR 和交叉开关

引脚分配情况列于表 3。

4 AN01-1.1

AN001 — 配置端口 I/O 交叉开关译码器

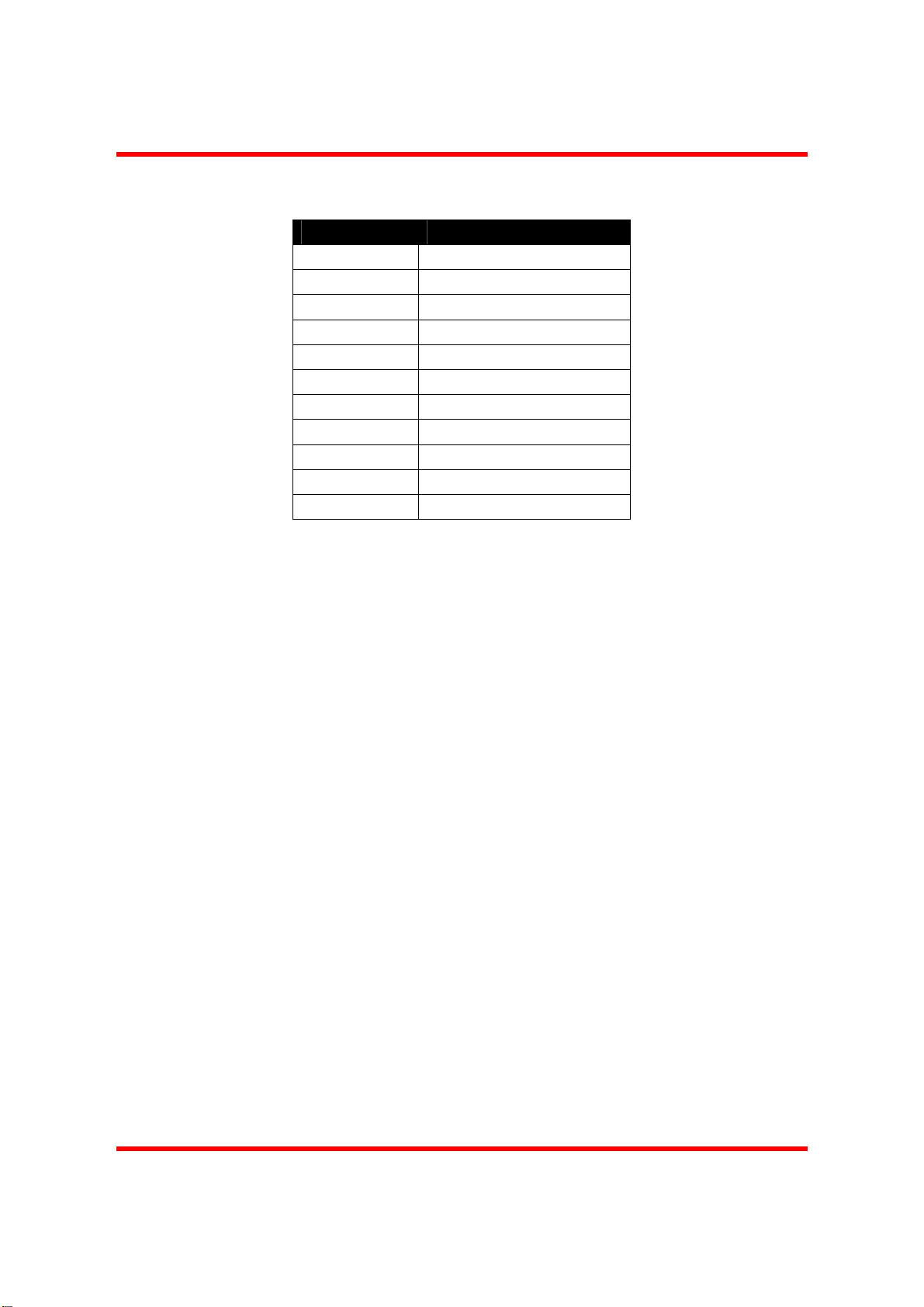

表 3. 例 3 的引脚分配

引脚 功能

P0.0 SDA

P0.1 SCL

P0.2 TX

P0.3 RX

P0.4 ECI

P0.5 /INT0

P0.6 /INT1

P0.7 T2EX

P1.0 /CNVSTR

P1.[1..7] GPIO

P2.[0..7] GPIO

AN01-1.1 5

剩余434页未读,继续阅读

huayangcvj

- 粉丝: 28

- 资源: 45

上传资源 快速赚钱

我的内容管理

收起

我的内容管理

收起

我的资源

快来上传第一个资源

我的资源

快来上传第一个资源

我的收益 登录查看自己的收益

我的收益 登录查看自己的收益 我的积分

登录查看自己的积分

我的积分

登录查看自己的积分

我的C币

登录后查看C币余额

我的C币

登录后查看C币余额

我的收藏

我的收藏  我的下载

我的下载  下载帮助

下载帮助

会员权益专享

最新资源

- c++校园超市商品信息管理系统课程设计说明书(含源代码) (2).pdf

- 建筑供配电系统相关课件.pptx

- 企业管理规章制度及管理模式.doc

- vb打开摄像头.doc

- 云计算-可信计算中认证协议改进方案.pdf

- [详细完整版]单片机编程4.ppt

- c语言常用算法.pdf

- c++经典程序代码大全.pdf

- 单片机数字时钟资料.doc

- 11项目管理前沿1.0.pptx

- 基于ssm的“魅力”繁峙宣传网站的设计与实现论文.doc

- 智慧交通综合解决方案.pptx

- 建筑防潮设计-PowerPointPresentati.pptx

- SPC统计过程控制程序.pptx

- SPC统计方法基础知识.pptx

- MW全能培训汽轮机调节保安系统PPT教学课件.pptx

资源上传下载、课程学习等过程中有任何疑问或建议,欢迎提出宝贵意见哦~我们会及时处理!

点击此处反馈

安全验证

文档复制为VIP权益,开通VIP直接复制

信息提交成功

信息提交成功

评论7