SystemVerilog SVA检查库详解与应用实例

需积分: 50 178 浏览量

更新于2023-03-03

3

收藏 4.6MB PDF 举报

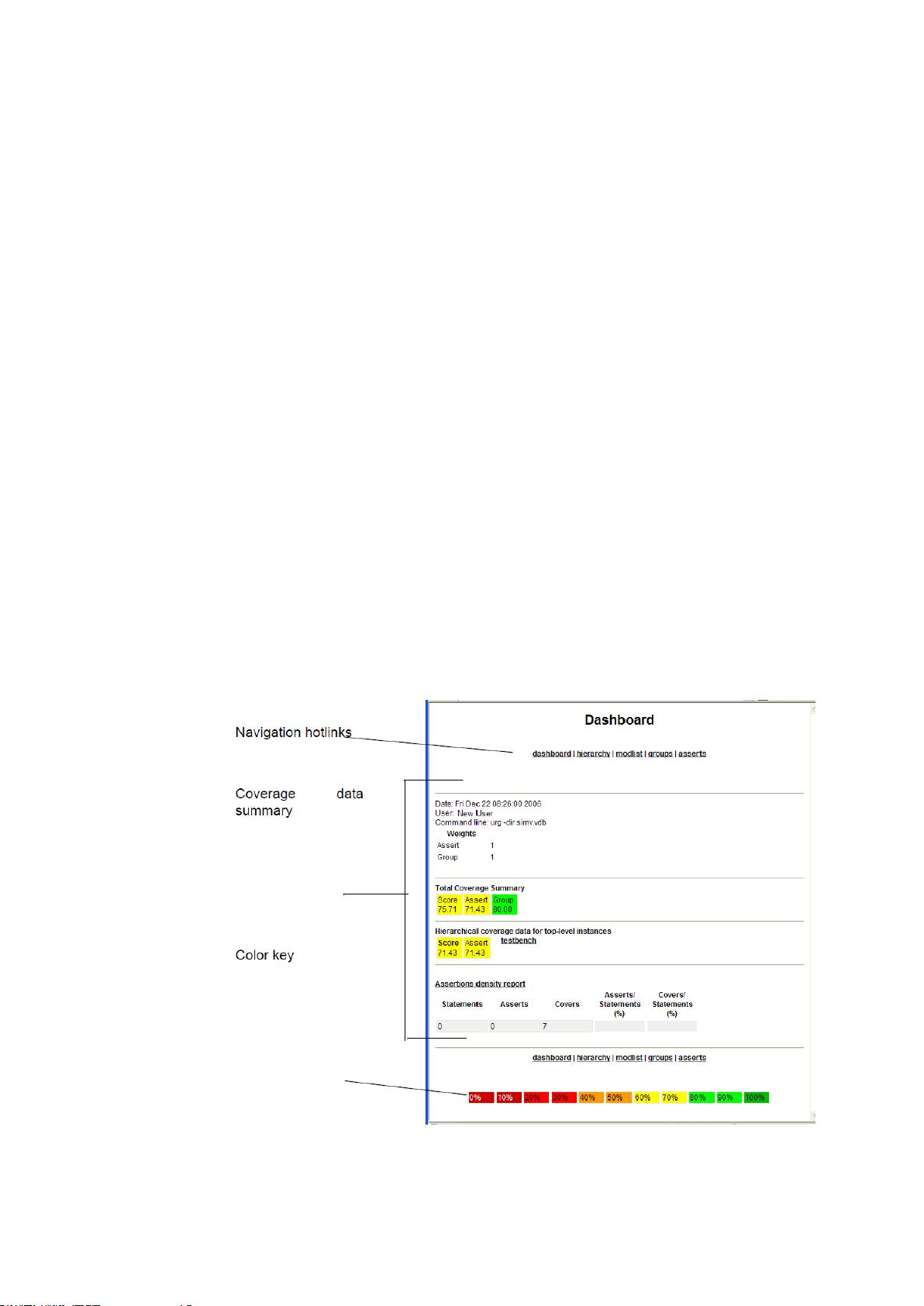

SystemVerilog 断言 (SVA) 是一种强大的工具,用于在系统级验证中提高效率和一致性。它是由Synopsys公司提供的一个标准库,旨在帮助设计者创建可重复使用的验证模块,以解决传统验证流程中的混乱问题。SVA的核心概念是检查器,它们是针对特定行为或属性的测试单元,通过实例化SVA库中的单元来实现。

1. **全局控制**:SVA提供了全局控制机制(GlobalControls),允许设置检查器的行为,如启用或禁用、设定严重性级别、选择性地报告错误等。这有助于统一验证策略并管理整个设计的验证流程。

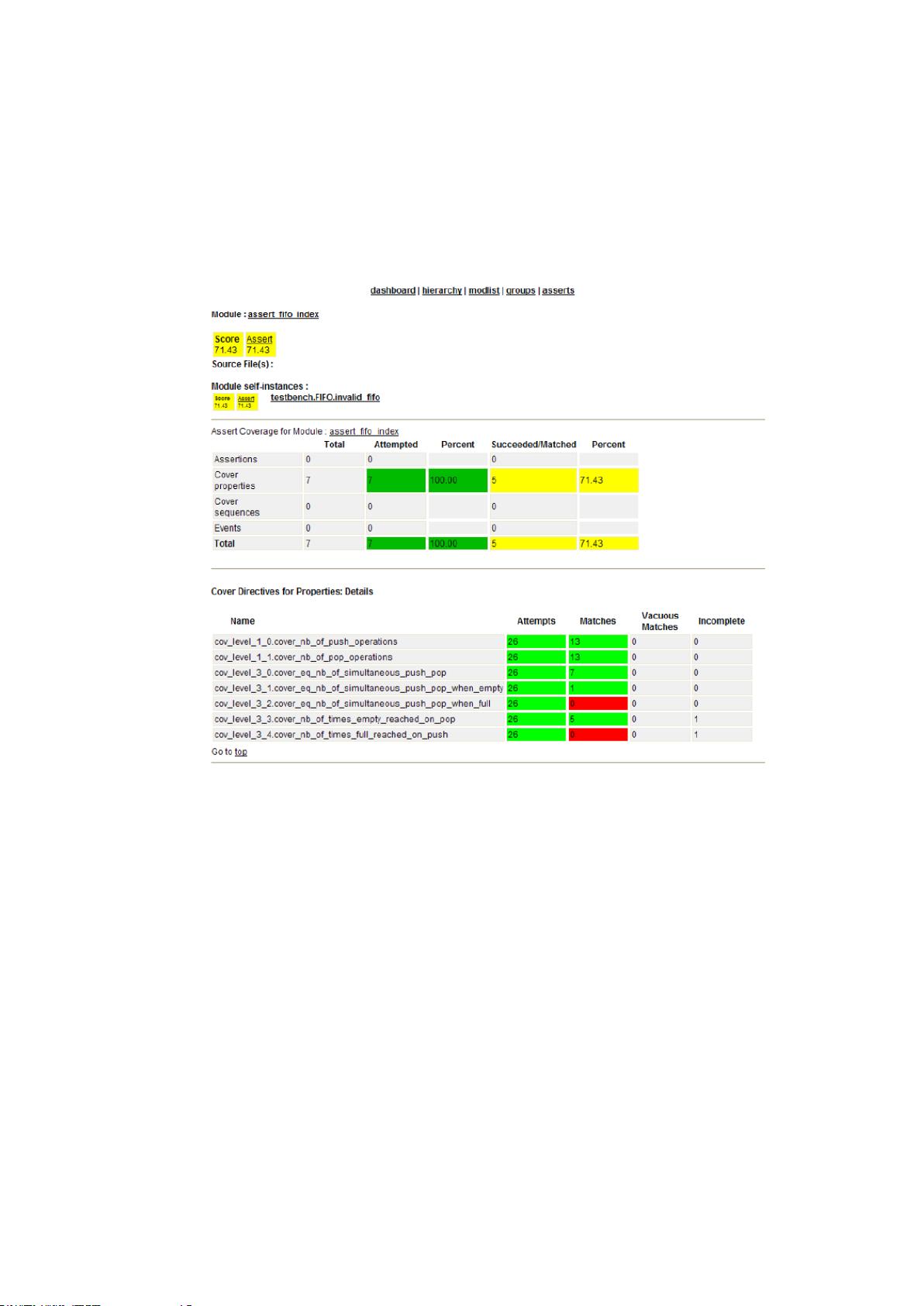

2. **检查器触发条件**:检查器可以根据多种条件触发,例如事件(assert_always, assert_always_on_edge)、时间周期(covergroup)、或者覆盖等级(coverage_level_i)来执行相应的验证检查。

3. **VMM报告**:SVA支持VMM(Verilog Monitoring and Modeling)报告,允许生成详细的验证信息,包括消息(msg)、类别(category)以及覆盖率等级(coverage_level_i)。

4. **覆盖率等级**:SVA强调了覆盖率的重要性,允许根据不同的等级(Level1、Level2、Level3)报告检查结果,以便设计者更深入地了解设计的验证覆盖率。

5. **参数检查**:使用SVA检查器时,可以设置模型参数,确保验证环境的一致性和准确性。同时,SVA也支持模式(pattern)的使用,这在处理复杂的行为或数据模式匹配时非常有用。

6. **基础检查器**:文档详细列举了两种主要的检查器:assert_always和assert_always_on_edge,它们分别用于持续检查和边沿触发的条件。每个检查器都有其特定的语法、参数设置,以及覆盖率模式示例,帮助用户理解和应用。

7. **范例和命名示例**:文档提供了丰富的例子,包括基于名称的示例,以便读者更好地理解如何在实际设计中实例化和配置这些检查器。

通过阅读这份翻译文档,学习者可以掌握如何有效地利用Synopsys的SVA库进行系统级验证,并遵循最佳实践,从而提升验证效率和代码的可维护性。此外,附录A引用的《A Practical Guide for SystemVerilog Assertions》进一步提供了深入的指导,确保设计者能够充分利用SVA的强大功能。

694 浏览量

816 浏览量

409 浏览量

455 浏览量

182 浏览量

157 浏览量

250 浏览量

246 浏览量

Jemwang

- 粉丝: 0

最新资源

- 英数图像识别库:验证码的通用处理技术

- 全面技术项目源码合集:商业名片设计与整站开发教程

- Android万能下载器:在线下载任意格式文件

- ACAD2008 Express汉化补丁使用指南

- C语言核心概念:指针、活动记录与内存管理

- webCAMotion:网络摄像头模拟鼠标的开源程序

- Axure高效设计模板:导航条与版权页母版

- C语言实现最小生成树算法及路径自动生成

- SPM8数据预处理及分析批处理工具

- 绿色大气个人摄影相册网站模板及全技术领域源码分享

- Android全屏注册界面的设计与实现技巧

- 易通远程屏幕监控系统安装与卸载详细指南

- Ehcache复制机制详解与集群环境演示教程

- Facebook Messenger终端控制:全新Python自动化脚本

- MATLAB动态规划程序包:优化算法实践

- Android ADT-22.0.5版本发布,探索新特性